Assigning Testpoints on a PCB in Altium Designer

Altium 제품에 접근할 수 있는 레벨에 따라 사용할 수 있는 기능이 달라집니다. 다양한 레벨의 Altium Designer Software Subscription에 포함된 기능과 Altium 365 플랫폼에서 제공하는 애플리케이션을 통해 제공되는 기능을 비교해보세요.

소프트웨어에서 논의된 기능을 찾을 수 없는 경우, Altium 영업팀에 문의하여 자세한 정보를 확인해주세요.

테스트는 보드 제조 과정에서 중요한 부분입니다. 제작 후, 보드는 일반적으로 Short이나 개방 회로가 없는지 확인하기 위해 테스트됩니다. 모든 부품이 완전히 장착된 후에는, 보드가 종종 신호 무결성과 장치 작동을 보장하기 위해 다시 테스트됩니다. 이 과정을 돕기 위해, 테스트 장비가 프로브하여 필요한 테스트를 수행할 수 있는 보드 상의 점들의 계획 - Test Point - 가 있으면 근본적으로 유익합니다.

보드에 Test Point의 위치는 테스트의 모드(베어보드 제작 테스트, 인-서킷 어셈블리 테스트 등 포함)와 테스트 방법(플라잉 프로브와 베드-오브-네일즈 고정 장치를 사용한 자동 테스트, 수동 테스트 등 포함)을 포함한 여러 요소에 따라 달라질 것입니다.

예를 들어, 베어보드 제작 테스트를 수행할 때는 보드가 장착되지 않았기 때문에 모든 Pad와 Via가 Test Point를 할당할 때 '공정한 게임'입니다. 그러나 인-서킷 어셈블리 테스트를 수행할 때 사용되는 Test Point의 위치는 거의 항상 다를 것입니다. 보드가 장착되면, 부품 Pad에 프로브 접근이 더 이상 가능하지 않을 수 있고, 부품 아래의 Pad와 Via에는 확실히 접근할 수 없습니다!

Altium Designer는 Test Point 요구 사항을 처리하고 보드의 테스트 가능성을 향상시키는 강력한 시스템을 제공하여, 필요에 따라 베어보드 제작 테스트 및/또는 인-서킷 어셈블리 테스트를 위해 별도로 Test Point를 할당할 수 있습니다. Test Point는 수동으로 할당하거나, Test Point Manager 대화 상자를 사용하여 더 간소화되고 자동화된 방식으로 할당할 수 있습니다.

Test Point 전략 고려하기 Copy Link Copied

Pad와 Via를 Test Point 위치로 사용하기 위해 할당하기 전에, 무엇이 필요한지에 대해 한발 물러나 생각해 보는 것이 좋습니다. 다음은 Test Point를 설계에 통합하기 위한 전략을 정의할 때 고려해야 할 몇 가지 지침입니다:

- Test Point가 허용될 보드의 어느 쪽 면을 선택할 때는, 사용될 테스트 공정과 관련된 고정 장치를 고려해야 합니다. 예를 들어, 보드가 하단 면에서만, 상단 면에서만, 아니면 양쪽 면에서 모두 프로빙될지 여부입니다.

- 부품 아래(부품와 같은 보드 쪽에)에 있는 Test Point는 일반적으로 베어보드 테스트 단계에서 사용됩니다. 조립된 보드 테스트를 위한 Test Point 위치를 계획할 때 이 점을 고려해야 합니다.

- 필요한 경우 Via를 사용하여 모든 Test Point를 보드의 한쪽 면에만 위치시키는 것이 좋습니다. 이는 듀얼 헤드 테스트 고정 장치가 단일 헤드 테스트 고정 장치보다 더 많은 비용이 들기 때문입니다.

- Test Point의 패턴이 비표준적이고 복잡할수록 보드를 테스트하기 위해 고정 장치를 구성하는 데 더 많은 비용이 들게 됩니다. 가장 좋은 철학은 일반적인 테스트 가능성을 달성할 수 있는 방법론을 개발하는 것입니다. 잘 다듬어진 유연한 Test Point 정책은 다양한 설계을 효율적이고 비용 효과적으로 테스트할 수 있게 해줍니다.

- 설계의 Via 텐팅 요구 사항에 대해 신중하게 고려해야 합니다. Test Point로 지정된 Via를 텐팅하면 테스트 프로브 접촉을 효과적으로 차단합니다. 액상 포토 이미지 가능(LPI) 솔더 마스크를 사용한 부분적 텐팅조차도 접촉 문제를 일으킬 수 있으며, 마스크 액체가 Via 홀을 통해 빠져나가려는 경향이 있습니다. 벗겨질 수 있는 솔더 마스크는 이러한 지정된 Via의 임시 텐팅에 사용될 수 있지만, 이는 종종 상당히 비용이 많이 들 수 있습니다.

- Test Point를 지정할 때 특정 설계 매개변수가 고려되도록 제작 및 조립 업체와 긴밀히 협의하십시오. 이러한 매개변수에는 일반 배치 및 라우팅 클리어런스보다 더 엄격할 수 있는 Test Point 간 클리어런스 및 Test Point와 부품 간 클리어런스가 포함될 수 있습니다.

다음 섹션에서는 제작 및 조립 테스트를 자세히 살펴보며, 각각과 관련된 특정 Test Point 제약 사항 및 고려 사항을 다룹니다.

Fabrication 테스트

제작 테스트는 어떤 부품도 보드에 배치되기 전, 제조의 사전 조립 단계에서 인쇄 회로 기판의 테스트와 관련이 있습니다. 따라서 이는 종종 베어보드 테스트로 언급됩니다. 이 테스트 방법은 일반적으로 네트별 테스트를 수행하기 위해 플라잉 프로브 장치를 사용하는 것을 포함할 수 있습니다.

본질적으로, 두 프로브가 협력하여 작동하도록 프로그래밍되며, 하나는 신호를 네트를 통해 펄스하고 다른 하나는 그 신호의 존재(또는 부재)를 감지합니다. 베어보드 제작 테스트에 대한 두 가지 일반적인 테스트 시나리오는 다음과 같습니다:

- 의도된 end-to-end 연속된 구리가 최대 허용 임피던스 임계값 아래에서 깨끗한 신호를 전달하는지 확인하는 테스트(오픈 회로 없이).

- 네트가 서로 Short되지 않았는지 확인하는 테스트.

Fabrication Test Point 위치 제약사항 Copy Link Copied

- 제작 테스트를 위해 전용 Test Point Pad/Via는 보통 필요하지 않습니다. 보드에 아직 부품이 장착되지 않았기 때문에, 프로브는 부품 Pad에 자유롭게 접근할 수 있습니다. 이 단계에서 Pad는 일반적으로 솔더 마스크가 없기 때문에, Test Point는 일반적으로 Pad 자체에 위치합니다.

- 플라잉 프로브 테스트는 그리드에 의해 제약받지 않습니다. 플라잉 프로브 장치는 상당히 정밀한 위치를 할 수 있기 때문입니다.

- 각 위치 쌍은 프로브 헤드의 물리적 크기 때문에 최소 분리 거리에 의해 제약됩니다.

예외 및 기타 고려 사항 Copy Link Copied

- 미세 피치 장치의 경우, 단일 부품 Pad를 프로브하는 것이 불가능하거나 실용적이지 않을 수 있습니다. 이러한 구리 특징은 매우 작고 섬세할 수 있으므로, 테스트 프로브와의 접촉을 피하는 것이 가끔 권장됩니다. 이러한 경우, 설계자가 보드에 전용 테스트 Pad/Via를 추가하는 것이 좋을 수 있습니다.

- 베어보드 제작 테스트 중에는 베드 오브 네일스 고정 장치를 사용할 수도 있습니다. 이는 일반적으로 대량 생산 시에 해당되며, 이러한 고정 장치를 사용하는 것은 플라잉 프로브보다 테스트 시간이 적게 걸립니다. 그러나 bed-of-nails 테스트는 더 엄격한 Test Point 위치 제약을 수반할 수 있으며, 테스트 고정 장치가 맞춤형이 아닌 경우, Test Point가 특정 그리드에 맞춰야 할 수도 있습니다.

- 특정 Test Point 위치 쌍이 플라잉 프로브에 의해 함께 테스트되지 않는 경우가 있습니다. 이는 두 네트 사이에 Short(또는 크로스토크)의 위험이 없을 때 일반적으로 발생합니다. 즉, 두 네트의 모든 객체가 물리적 근접성에 의해 서로 분리되어 있습니다.

Assembly (조립) 테스트

조립 테스트는 제조의 후반 단계, 즉 인쇄 회로 기판(PCB)이 관련 자재 목록(BOM)에 명시된 모든 부품로 채워진 후에 수행되는 테스트를 말합니다. 따라서, 이는 종종 인-서킷 또는 전기 테스트로 언급됩니다. 이 테스트 방법은 일반적으로 (하지만 반드시 그런 것은 아닙니다!) 수동으로 구성된 bed-of-nails(fixture)의 사용을 포함합니다. 픽스처를 사용하여 수행되는 테스트의 유형에 따라, 보드는 전원이 공급될 수도 있고 그렇지 않을 수도 있습니다.

인-서킷 조립 테스트에 대한 두 가지 일반적인 테스트 시나리오는 다음과 같습니다:

- 각 네트워크(또는 관심 있는 네트워크)마다 전용 Test Point를 동시에 탐색합니다. 이는 각 프로브를 개별적으로 펄스 신호를 통해 주입하고, 다른 모든 프로브에서 신호 수신 결과를 감지하는 방식으로 수행됩니다.

- 특정 부품/버스를 테스트하여 장치 자체가 제대로 작동하는지 확인합니다. 이러한 테스트는 다양한 테스트 방법을 사용하여 수행할 수 있는 전문화된 테스트입니다. 가장 간단한 경우, 네일 침대 고정구를 사용하여 부품 Pad를 통해 테스트할 수 있습니다.

Assembly Test Point 위치 제약사항 Copy Link Copied

- Test Point 위치는 일반적으로 최소 간격 요구사항을 준수해야 합니다. 침대형 네일 고정 장치 프로브 헤드와 같은 테스트 장비는 서로 가까이 있을 수 있는 몸체 크기에 제약을 받습니다. 맞춤형 고정 장치를 사용하지 않는 한, Test Point 위치는 종종 특정 그리드에 있어야 합니다. 맞춤형 고정 장치를 제작하는 것은 재사용 가능한 침대형 네일 고정 장치를 구성하는 것보다 더 비용이 많이 들고 시간이 걸립니다.

- Test Point는 부품 몸체에 대한 최소 클리어런스에 따라 위치해야 할 수 있습니다. 대부분의 테스트 고정 장치의 프로브 헤드는 고정 장치에 가까울수록 크기가 커지고 프로브의 샹크에 접근함에 따라 더 작은 크기로 좁아집니다. 더 높은 부품은 더 많은 클리어런스를 요구합니다. 따라서 보드의 최대 부품 높이를 고려하고 이 최악의 시나리오를 고려하여 전체 몸체 클리어런스를 정의하는 것이 가장 좋습니다.

- Test Point 위치는 보드 가장자리에 대한 최소 클리어런스에 따라 위치해야 할 수 있습니다. flying probe pair 이나 bed-of-nails 배열로 보드에 접촉하는 과정은 보드 자체에 어려울 수 있으며, 자동 테스트의 압력 하에 보드가 어느 정도 휠 수 있습니다. 이러한 이유로, Test Point가 보드 가장자리에서 멀리 위치할 때 얇고 취약한 보드의 손상이 최소화됩니다.

- Test Point Pad/Via는 설계 중 각 네트에 추가되어야 하는데, 이는 여러 가지 이유로 필요합니다:

1. Bare copper 부품 Pad는 일반적으로 배치된 부품의 존재로 인해 접근할 수 없게 됩니다.

2. 보드가 테스트를 염두에 두고 특별히 설계되지 않는 한, 부품 Pad와 Via는 필요한 Test Point 그리드에 위치하지 않을 가능성이 큽니다.

3. 부품 Pad 자체가 Test Point 위치로 사용하기에 적합해 보일지라도, 부품 몸체에 대한 클리어런스 제약으로 인해 사용할 수 없습니다.

예외 사항 및 기타 고려 사항 Copy Link Copied

- bed-of-nails fixture는 조립 테스트의 일반적인 방법이지만, 유일한 방법은 아닙니다. 대안 중에는 부품이 배치된 것과 충돌하지 않도록 주의하면서 flying probe 장치가 사용되는 경우도 있습니다.

- 특정 부품에 대한 전기 테스트를 수행할 때, 테스트 프로브가 어느 정도까지는 부품 Pad에 접근할 수 있습니다. 그러나 부품 본체가 이러한 Pad의 중앙을 종종 가리기 때문에, 중요한 점은 보드가 조립된 후에 접근 가능한 Pad 부분이 Pad 중앙 위치를 거의 포함하지 않는다는 것입니다.

Pad 및 Via Test Point 지원 Copy Link Copied

Altium Designer는 Test Point에 대한 전체 지원을 제공하여, 제작 및/또는 조립 테스트에서 Test Point 위치로 사용될 Pad(스루홀 또는 SMD) 및/또는 Via를 지정할 수 있습니다. Pad 또는 Via는 관련 Test Point Properties을 설정하고 두 가지 주요 질문에 답함으로써 Test Point로 지정됩니다:

- Pad/Via를 제작 및/또는 조립 Test Point로 사용해야 합니까?

- Pad/Via를 Test Point로 사용할 보드의 어느 쪽에 위치해야 합니까 - 상단, 하단, 또는 양쪽?

이러한 Properties은 설계 공간에서 Pad(참조 Pad Properties) 또는 Via(참조 Via Properties) 객체가 선택될 때 각각 Properties 패널에서 찾을 수 있습니다.

선택된 Pad 또는 Via가 Properties 패널을 통해 제공되는 관련 옵션을 통해 Test Point로 지정됩니다.

선택된 Pad 또는 Via가 Properties 패널을 통해 제공되는 관련 옵션을 통해 Test Point로 지정됩니다.

Test Point Properties을 수동으로 설정할 필요성을 줄이고 과정을 간소화하기 위해, Altium Designer는 정의된 Design Rule을 기반으로 자동으로 Test Point를 할당하는 방법을 제공하며, Test Point Manager를 사용합니다. 이 자동 할당은 각 경우에 Pad/Via의 관련 Test Point Properties을 설정합니다. 또한, Test Point를 수동으로 지정할 수 있는 옵션도 있습니다 - 본질적으로 개별 Pad/Via 수준에서 수작업을 하는 것 - 이는 보드에 사용된 Test Point 체계에 대한 전체 제어를 가능하게 합니다. 소프트웨어의 Summer 09 릴리스 이전에 생성된 PCB 설계을 열 때, 활성화된 Test Point 옵션은 Fabrication Test Point 옵션으로 활성화됩니다.

Test Point Design Rule Copy Link Copied

PCB 설계의 제약 사항은 잘 다듬어진 Design Rule 세트로 생각하고 구현되어야 합니다. 모든 정의된 Test Point에 접근하여 베어보드 및/또는 인-서킷 테스트의 일부로 사용할 수 있는 성공적인 Test Point 체계를 구현하기 위해서는 지배적인 제약 사항이 마련되어야 합니다. 이를 위해, 다음과 같은 Rule 유형이 PCB Editor의 Design Rule 시스템의 일부로 정의될 수 있습니다:

- Fabrication Test Point Style

- Fabrication Test Point 사용법

- Assembly Test Point Style

- Assembly Test Point 사용법

PCB Rule 및 Constraint Editor 대화 상자(Design » Rule)에서 이러한 유형의 Rule에 접근하고 정의하세요.

제작 Test Point와 조립 Test Point로 사용될 수 있는 Pad 및/또는 Via를 제한하고 어떤 네트에 Test Point가 필요한지를 정의하는 별도의 Design Rule을 정의합니다.

제작 Test Point와 조립 Test Point로 사용될 수 있는 Pad 및/또는 Via를 제한하고 어떤 네트에 Test Point가 필요한지를 정의하는 별도의 Design Rule을 정의합니다.

Test Point Style 및 사용 Rule은 제작 및 조립의 두 테스트 모드에서 제약 조건 측면에서 동일합니다. Style Rule은 Pad나 Via가 Test Point 위치로 선택되기 위해 충족해야 하는 제약 조건을 기본적으로 지정합니다. 사용 Rule은 어떤 네트에 Test Point가 필요한지를 지정합니다.

Test Point 사용(상단) 및 Test Point Style(하단) Rule에 대한 기본 제약 조건.

Test Point 사용(상단) 및 Test Point Style(하단) Rule에 대한 기본 제약 조건.

Test Point Design Rule은 Test Point Manager, Autorouter, 온라인 및 배치 DRC 프로세스, 그리고 출력 생성 중에도 사용됩니다.

디폴트 Fabrication/ Assembly Test Point Style 및 Test Point 사용 Rule이 존재합니다. 이러한 Rule이 귀하의 보드 요구 사항을 충족하는지 확인하고 필요에 따라 변경해야 합니다. 동일한 유형의 여러 Rule이 필요한 경우, 더 구체적인 범위를 가진 Rule이 먼저 적용되도록 Design Rule의 우선 순위 측면을 사용하십시오(예: DRC 실행 시).

Test Point Manager가 Test Point를 성공적으로 할당하려면 범위가 'All'인 해당 Test Point Style Rule이 반드시 하나 이상 있어야 합니다. 소프트웨어의 Summer 09 릴리스 이전에 생성된 PCB 설계을 열거나 Design Rule을 가져올 때, Test Point Style Rule은 제작 Test Point Style Rule이 되고 Test Point 사용 Rule은 제작 Test Point 사용 Rule이 됩니다.

Test Point Manager Copy Link Copied

Test Point를 수동으로 할당하는 것은 매우 까다롭고 힘든 작업이며, 특히 수백 개의 부품이 장착된 복잡한 보드에서는 더욱 그렇습니다(보드 양면에 걸쳐서). 보드 설계에서 Test Point를 효율적으로 관리할 수 있도록 Altium Designer는 PCB Editor에 Test Point Manager를 제공합니다.

Test Point Manager를 사용하면 정의된 Design Rule을 기반으로 Test Point를 자동으로 할당할 수 있으며, 이는 베어보드 제작 테스트 및/또는 인-서킷 어셈블리 테스트를 위한 것입니다. 이 자동 할당은 각 경우에 Pad/Via에 대한 관련 Test Point Properties을 설정합니다.

접근은 메인 메뉴에서 Tools » Test Point Manager 명령을 선택함으로써 이루어집니다.

제작 및 조립 Test Point 요구 사항을 Test Point Manager를 사용하여 신속하고 효율적으로 관리하세요.

제작 및 조립 Test Point 요구 사항을 Test Point Manager를 사용하여 신속하고 효율적으로 관리하세요.

대화 상자를 사용하여 한 곳에서 Test Point를 자동으로 할당하고 지울 수 있습니다.

설계의 모든 네트 목록이 Testpoint Net Status 영역에 제공되며, 베어보드 제작 및 인-서킷 조립 테스트에 대한 Test Point 커버리지를 나타내는 상태 - Complete 또 Incomplete가 표시됩니다. Fabrication Testpoints 또는 Assembly Testpoints버튼을 클릭하거나, 마우스 오른쪽 버튼을 클릭하여 해당 유형의 Test Point를 할당하거나 지우는 명령에 접근할 수 있습니다. 대화 상자의 상단 영역에서 네트를 수동으로 선택하여 Test Point를 선택적으로 할당/지울 수 있음을 유의하십시오.

설계의 일부 또는 모든 네트에 대해 Test Point를 할당하는 경우, Test Point Manager는 제작 및 조립 Test Point에 대해 정의된 Style 및 사용 Rule을 따릅니다. 유효한 객체가 검색되는 순서를 보려면 Search Order 버튼을 클릭하십시오.

Status Summaries 영역은 보드의 Test Point 상태에 대한 전체 요약을 제공하며, 두 가지 테스트 모드 모두에 대해 제공됩니다. 이 영역은 할당 또는 해제 작업이 수행될 때마다 업데이트됩니다. 더 낮은 수준의 세부 정보를 원하면 Assignment Results 영역을 사용하세요. 예를 들어, 할당/해제에 관련된 상단/하단 Pad/Via의 수와 실패의 표시와 같은 세부 정보를 제공합니다.

Test Point의 유효성 검사 Copy Link Copied

PCB 편집기의 Design Rule 검사(DRC) 기능의 일부로 정의된 제작 및 조립 Test Point Rule이 따라집니다. 온라인 및/또는 배치 DRC 검사는 Design Rule Checker 대화 상자(Tools » Design Rule 검사) 내에서 다양한 Rule 유형에 대해 활성화할 수 있습니다.

온라인 또는 배치 DRC 프로세스의 일부로 Test Point Design Rule을 포함합니다.

온라인 또는 배치 DRC 프로세스의 일부로 Test Point Design Rule을 포함합니다.

Test Point 관련 쿼리 필드 Copy Link Copied

설계에서 할당할 수 있는 다양한 제작 및 조립 Test Point를 지원하기 위해, 논리적 쿼리 표현식을 사용하여 Test Point를 대상으로 할 때 사용할 수 있는 다음 키워드들이 있습니다. 다음 각각은 PCB Fuctions - Fields 카테고리에서 쿼리 도우미를 사용할 때 찾을 수 있습니다:

IsAssyTestpoint- 조립 Test Point입니다.IsFabTestpoint- 제작 Test Point입니다.IsTestpoint- 상단 또는 하단 측면 Test Point입니다.Testpoint- 상단 또는 하단 측면 Test Point인가요?TestpointAssy- 조립 Test Point인가요?TestpointAssyBottom- 하단 측면 조립 Test Point인가요?TestpointAssyTop- 상단 측면 조립 Test Point인가요?TestpointBottom- 하단 측면 Test Point인가요?TestpointFab- 제작 Test Point인가요?TestpointFabBottom- 하단 측면 제작 Test Point인가요?TestpointFabTop- 상단 측면 제작 Test Point인가요?TestpointTop- 상단 측면 Test Point인가요?

설계에서 필요에 따라 Test Point를 대상으로 하고 반환하기 위한 논리적 표현식을 생성하세요. 제작 및 조립 Test Point를 대상으로 하는 논리적 쿼리 표현식의 예는 다음과 같습니다:

(ObjectKind = 'Pad') And (TestpointAssy = 'True')

조립 Test Point인 모든 Pad를 대상으로 합니다.IsPad And (TestpointAssyTop = 'True')

상단 조립 Test Point인 모든 Pad를 대상으로 합니다.(ObjectKind = 'Pad') And (TestpointFab = 'True')

제작 Test Point인 모든 Pad를 대상으로 합니다.((IsPad 또는 IsVia)) And (TestpointAssy = 'True')

조립 Test Point인 모든 Pad와 Via를 대상으로 합니다.((IsPad 또는 IsVia)) And IsFabTestpoint

제작 Test Point인 모든 Pad와 Via를 대상으로 합니다.

Test Point 보고서 생성 Copy Link Copied

Altium Designer는 제작 및 조립 Test Point 보고서를 각각 생성하기 위한 전용 보고서 생성기를 포함하고 있습니다. 이 두 보고서 생성기는 설계의 Pad와 Via 원시물에 대한 관련 Test Point Properties을 활용합니다.

보고서는 두 가지 방법으로 생성할 수 있습니다:

- PCB 문서 내에서 직접 File » Fabrication Outputs » Test Point Report 및 File » Assembly Outputs » Test Point Report 명령을 사용하여 생성합니다.

- 출력 작업 구성 파일(

*.OutJob)에 정의된 적절하게 구성된 출력을 사용하여 생성합니다.

자체 포함되고 다재다능한 출력 작업 구성 파일 내에 제작 및 조립 Test Point 보고서 출력을 포함시키고 구성하세요. 한 번 정의하면 버튼을 누르는 것만으로 보고서를 얻을 수 있습니다!

자체 포함되고 다재다능한 출력 작업 구성 파일 내에 제작 및 조립 Test Point 보고서 출력을 포함시키고 구성하세요. 한 번 정의하면 버튼을 누르는 것만으로 보고서를 얻을 수 있습니다!

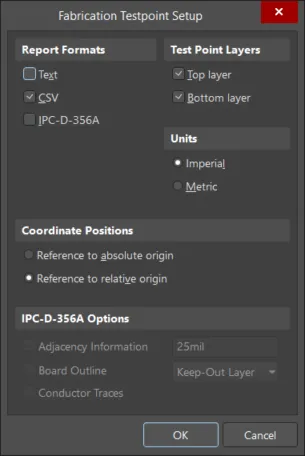

보고서를 생성하는 데 사용된 방법에 관계없이, 보고서 옵션 자체는 동일한 대화 상자에서 정의됩니다. 제작 Test Point 보고서의 경우, Fabrication Testpoint Setup dialog 가 사용됩니다. 조립 Test Point 보고서의 경우, Assembly Testpoint Setup dialog 가 사용됩니다. 이 대화 상자들 사이의 보고서 옵션은 동일합니다.

관련 보고서 설정 대화 상자를 사용하여 생성된 파일 형식을 포함한 보고서 옵션을 정의합니다.

IPC-D-356A 넷리스트 파일의 역할 Copy Link Copied

Test Point 보고서 출력 형식의 세 가지 유형 중 하나는 IPC-D-356A 넷리스트 파일입니다. 이 파일은 일반적으로 베어보드 제작 테스트 모드를 대상으로 사용됩니다. IPC 파일은 비행 프로브 테스트 장치를 구동하는 명령으로 후처리됩니다.

IPC-D-356A 파일에서 Test Point 위치로 특별히 식별된 기능에 관계없이, 보드 제작 업체는 파일 데이터를 사용하여 원하는 어떤 유형의 테스트라도 일반적으로 수행할 수 있습니다. 그러나 상황과 파일의 내용에 따라, 이를 수행하기 위해 수동 개입이 필요할 수도 있습니다.