Configuring the DRC

Configuration for design rule checking is performed in the Design Rule Checker dialog accessed through the Tools » Design Rule Check command from a PCB document.

The Design Rule Checker dialog showing defaults with certain Online DRC checks disabled to improve PCB Editor performance. Use the associated options to include a design rule type for checking as part of Online DRC and/or Batch DRC.

The Design Rule Checker dialog showing defaults with certain Online DRC checks disabled to improve PCB Editor performance. Use the associated options to include a design rule type for checking as part of Online DRC and/or Batch DRC.

Options and Controls of the Design Rule Checker Dialog

The dialog's functionality is essentially divided into two areas:

-

Configuration of options relating to a Batch DRC.

-

Configuration of which rules to check, and whether those rules should be checked as part of the Online and/or Batch DRC.

These areas are reflected by, and accessed through, the folder-like entries in the left-hand pane.

Report Options

Clicking on the Report Options folder loads the right-hand side of the dialog with additional options that are available when running a Batch DRC.

DRC Report Options

-

Create Violations – enable this option to have violations highlighted in the design space in accordance with defined violation display settings. This option is also required to have violations appear listed in the Violations region of the PCB Rules And Violations panel.

Management of how DRC violations are displayed – using custom violation graphics and/or a defined violation overlay – is performed on the

PCB Editor – DRC Violations Display page of the

Preferences dialog.

-

Sub-Net Details – if an Un-Routed Net rule has been defined, enable this option to include sub-net details in the DRC report.

The Un-Routed Net rule should only be enabled for checking when all connections have been routed, as a connection line is effectively an "open circuit".

-

Verify Shorting Copper – enable this option to verify the integrity of the shorting copper in any Net Tie components used in the design. This check looks for any unconnected copper in a component (indicative of a pad not shorting the other pad(s) correctly).

-

Report Drilled SMT Pads – enable this option to include any SMT (Surface Mount Technology) pads that have been erroneously drilled in the DRC Report.

An SMT pad can be, for example, a short pin; flat contact; one of a matrix of balls (BGAs); a termination on the body of a component (passives); or a short lead in a gull-wing formation (QFPs).

This option is only for detecting SMT pads with holes defined in them, which was possible in legacy versions of the software. To check for vias under SMD pads, the

Vias Under SMD rule (in the

High Speed category) must be added to the design and enabled for Batch DRC.

-

Report Multilayer Pads with 0 size Hole – enable this option to include any invalid multi-layer pads found in the design. An invalid multi-layer pad is one whose hole size is zero that would otherwise make it an SMT pad.

-

Stop when n violations found – use this field to determine the maximum number of violations that can be detected before the batch DRC process is stopped (default =

500). Limiting the number of violations that are reported is a key strategy in keeping the checking process manageable.

Split Plane DRC Report Options

-

Report Broken Planes – enable this option to have the batch rule checking process look for and report broken planes. Broken planes occur when an area of a plane that has connectivity to a net becomes electrically disconnected from the rest of the plane. An example of where this may occur is a connector placed across a split plane but not connected to it. The voids around the pins join to completely cut through the plane copper, effectively breaking it into two parts.

To check for broken planes, the

Un-Routed Net rule (in the

Electrical category) must be enabled for Batch DRC.

-

Report Dead Copper larger than – enable this option to have the batch rule checking process look for, and report, dead copper regions larger than the specified area. Dead copper refers to sections of copper that have no connectivity to a net, and which also become electrically disconnected from the original parent plane. An example of where this may occur is a connector (not connected to the plane) with closely spaced pins, in which the voids around the pins join to isolate areas of plane copper from the rest of the plane. Use the associated field to specify a value for the minimum permissible area of dead copper, beyond which is considered a rule breach (default = 100 sq. mils).

When the Report Dead Copper larger than option is enabled, all objects with no net assigned, regardless of their size, will also be reported during batch rule checking. This feature is available by setting the value of the PCB.Rules.DeadCopperNoNet option in the Advanced Settings dialog to configure the desired detection setting as shown below. The default value is 2.

0 - Do not check any.

1 - Check all.

2 - Check all except free Pads, Text objects, and objects in Components.

Also, when the Report Dead Copper larger than option is enabled, copper layer objects with a net assignment but not connected to any pad object of the same net and not connected with other objects of the same net with connection lines will be checked. This feature is in Open Beta and available when the PCB.Rules.DeadCopperInNet option is enabled in the Advanced Settings dialog.

To check for dead copper, the

Un-Routed Net rule (in the

Electrical category) must be enabled for Batch DRC.

-

Report Starved Thermals with less than n% available copper – enable this option to have the batch rule checking process look for and report 'starved' thermal connections larger than the specified percentage. Thermals are connections to a plane with thermal relief 'cutouts' around them to reduce heat conductivity to the plane copper. A thermal can become 'starved' when the surface area of the copper spokes connecting it to the plane is reduced by void areas. This option also checks the surface area for the thermal (not just the spokes) against any void areas that encroach into the thermal. Use the associated field to specify a value for the minimum permissible percentage of connecting copper that must remain, below which is considered a rule breach (default =

50%).

-

Run Design Rule Check – click this button to perform a Batch DRC in accordance with rules enabled for Batch checking and additional options defined for this type of checking.

After the check has been completed, all violations will appear in the Messages panel.

Rules To Check

Clicking on the Rules To Check folder loads the right-hand side of the dialog with a list of all checkable rule types. Alternatively, click on a specific category (below the folder) to list only those design rule types associated to that category.

For each rule type, the following information is presented;

-

Rule – the type of rule.

-

Category – the parent category to which the rule type is associated.

-

Online – the current state of this rule type with respect to Online DRC (where available). Click to toggle.

-

Batch – the current state of this rule type with respect to Batch DRC. Click to toggle.

Enable each rule type for Online and/or Batch checking as required.

Use the right-click menu to access commands for quickly enabling/disabling all rule types for Online or Batch DRC or only those rule types that are used (defined and enabled for use).

Notes

-

A generated Design Rule Verification Report lists each rule that was tested during the batch checking process as specified in this dialog. Each violation that was located is listed with full details of any reference information, such as the layer, net name, component designator, and pad number, as well as the location of the object. Click on the entry for an offending object to cross probe directly to that object in the design space.

-

To give further flexibility when displaying rule violations in the design space, the two violation display types – violation details (custom violation graphics) and violation overlay – have separate associated system colors. This allows you to differentiate between the two using different, distinct colors. Color assignment is performed on the Layers & Colors tab of the View Configuration panel:

-

Violation Details – uses the color assigned to the Violation Markers color in the System Colors region.

-

Violation Overlay – uses the color assigned to the DRC Error Markers color in the System Colors region.

-

After running a Batch DRC, double-click on a violation message in the Messages panel to cross-probe to the object(s) causing that violation in the design space.

-

When running an Online or Batch DRC, any rule violations will be listed in the Violations region of the PCB Rules and Violations panel.

-

Violations associated with a particular design object can be interrogated directly within the PCB design space. Position the cursor over an offending object, right-click then choose a command from the Violations sub-menu. Either choose to investigate an individual violation that the object is involved in, or choose to view all violations in which it is involved, using the Show All Violations command. In each case, the Violation Details dialog will appear providing detailed violation information and controls for highlighting and jumping to the offending object(s).

In the folder-tree pane on the left side of the dialog, each of the design rule categories whose rule types can be checked are listed under the Rules To Check folder. Click on this top-level folder to list all checkable rule types on the right side of the dialog. Alternatively, click on a specific category to list only those design rule types associated to that category. Use the dialog to enable/disable Online (where available) and/or Batch Mode checking for each rule type you want to check.

Use the right-click menu to access commands for quickly enabling/disabling all rule types for Online or Batch DRC, or only those rule types that are used (defined and enabled for use in the design).

It is particularly recommended that a batch mode design rule check always be performed prior to generating final artwork. Online DRC only detects new violations – violations that are created after the feature is enabled – while Batch DRC allows a check to be manually run at any time during the board design process. So while good designers know the value of the Online DRC, they also know that board design should begin and end with a Batch DRC. For detail on configuration options for a Batch DRC, see

Using Batch DRC.

Using Online DRC

Online Design Rule Checking runs in the background, in real-time, flagging and/or automatically preventing design rule violations. This is especially helpful when interactively routing your board to immediately highlight clearance, width and parallel segment violations. For a rule to be subject to the Online DRC, the following three requirements must be met:

-

The rule must be enabled. This can be done in either the PCB Rules and Constraints Editor dialog by ensuring the Enabled option for the rule is checked, or in the PCB Rules and Violations panel by ensuring the On option for the rule is checked.

Ensure that design rules you wish to have monitored by the Online DRC are actually enabled for use in the design.

Ensure that design rules you wish to have monitored by the Online DRC are actually enabled for use in the design.

-

The rule type must be enabled for online checking in the Design Rule Checker dialog.

Ensure that the rule type is enabled for Online DRC.

Ensure that the rule type is enabled for Online DRC.

-

The Online DRC feature must be turned on. Do this by enabling the Online DRC option on the PCB Editor - General page of the Preferences dialog.

Ensure that the Online DRC feature is enabled.

Ensure that the Online DRC feature is enabled.

If any objects are found to be in violation of an applicable design rule that is enabled for online checking, they will be highlighted in the design space in accordance with defined violation display options.

Using Batch DRC

Whereas Online DRC only detects new violations - violations that are created after the feature is enabled - Batch DRC allows a check to be manually run at any time during the board design process. So while good designers know the value of Online DRC, they also know that board design should begin and end with a Batch DRC.

To clear existing error markers, select Tools » Reset Error Markers from the PCB editor menus.

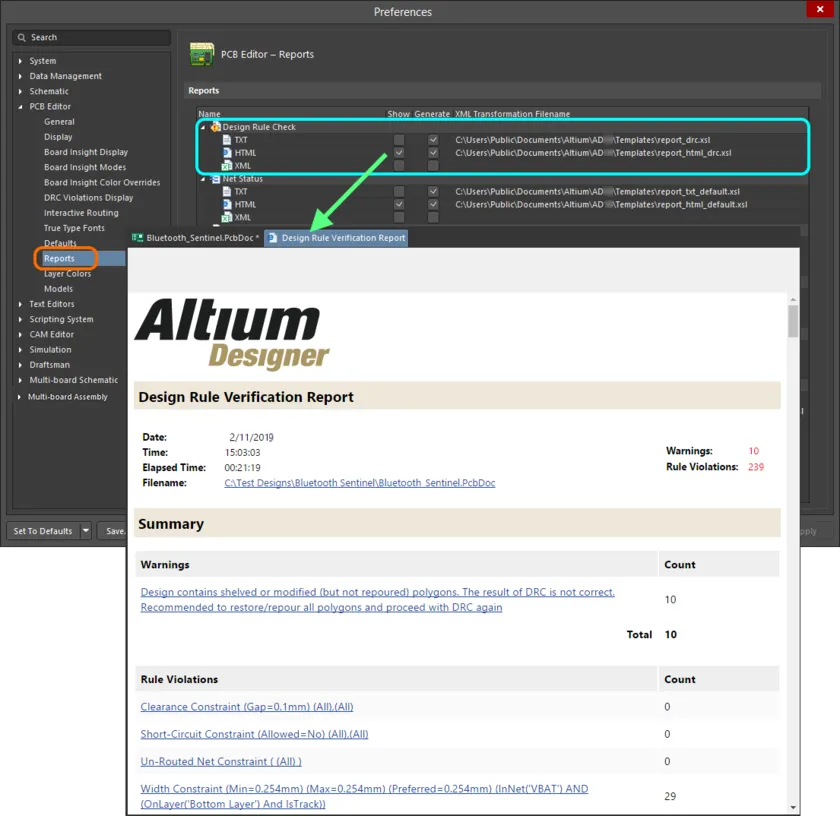

Enable rule types for batch checking in the Design Rule Checker dialog as required (refer back to the Configuring the DRC section). Various additional options are available when running a Batch DRC, including the ability to generate a report file. These options are accessed by clicking on the Report Options folder in the folder-tree pane of the dialog. Two key options (highlighted in the following image) are:

-

Create Report File - enable this option to generate a DRC report. Enable the Report PCB Health Issues sub-option to include the issues detected by the PCB Health Check Monitor into the generated report.

-

Create Violations - enable this option to have violations highlighted in the design space in accordance with defined violation display options. This option is also required to have violations appear listed in the Violations region of the PCB Rules And Violations panel.

Accessing options applicable to running a Batch DRC, and generating a DRC report.

Accessing options applicable to running a Batch DRC, and generating a DRC report.

A batch-mode DRC is initiated by clicking the Run Design Rule Check button at the bottom-left of the dialog. After the check has completed, all violations are listed as messages in the Messages panel. If you opted to do so, a DRC report will be created and automatically opened (if configured to do so) as the active document in the main design window. The report lists each rule that was tested as specified in the Design Rule Checker dialog. Rules that are not present in the design are not tested.

DRC Reports

Enabling the Create Report File option in the Design Rule Checker dialog will generate a DRC report upon execution of a Batch DRC. Options available on the PCB Editor - Reports page of the Preferences dialog allow specification of report format, and whether the report is automatically displayed after generation.

Generate a DRC report as part of the Batch DRC process.

Supported formats are:

-

TXT - generates the file Design Rule Check - <PCBDocumentName>.drc.

-

HTML - generates the file Design Rule Check - <PCBDocumentName>.html.

-

XML - generates the file <PCBDocumentName>.xml .

TXT and HTML format reports are generated into the folder specified in the

Output Path field on the

Project Options - Options dialog. The XML format file is generated into the same location as the parent project file.

The report lists each rule that was tested during the batch checking process as specified in the Design Rule Checker dialog. Each violation that was located is listed with full details of any reference information, such as the layer, net name, component designator, and pad number, as well as the location of the object.

In the HTML format report, click on the entry for an offending object to cross probe directly to that object in the design space. Note that the zoom level for this click action is configured on the System – Navigation page of the Preferences dialog.

Violation Display Options

Checking the design against specified design rules is one thing, but what happens when one or more of those rule are violated? Whether running Online DRC during design or manually running a Batch DRC, there needs to be some visual indication of where such rule violations are occurring. The PCB Editor includes powerful violation display options to indicate where violations exist in a clear, visual way.

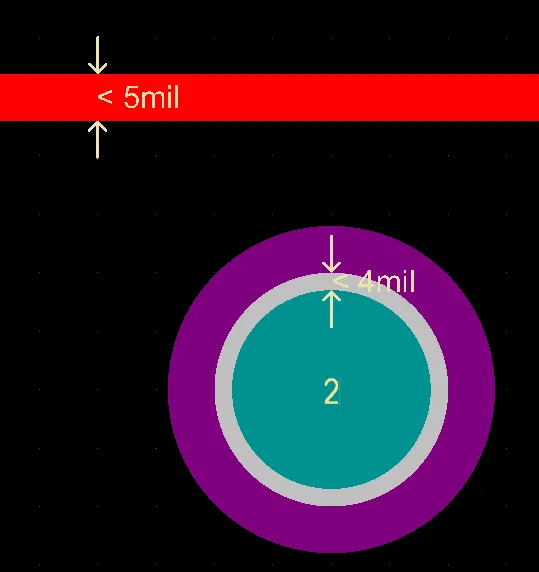

Custom Violation Graphics

Most design rules that can be included in either Online and/or Batch design rule checking have associated custom violation graphics - appearing within the design space when a particular rule is violated. These graphics provide a visually cleaner DRC landscape. When a particular design rule is violated, the associated custom violation graphics (where applicable) are only drawn on the layer(s) involved with that violation.

In some cases, the graphic shows not only where the violation is occurring, but also why - displaying the constraint value defined for the rule and indicating how the offending primitive(s) are either below or above this value.

Example illustrating the custom graphics used for width and minimum annular ring rule violations.

Example illustrating the custom graphics used for width and minimum annular ring rule violations.

Other graphics, including those used to represent violations of Net Antennae, Short-Circuit, Un-Routed Net, Room Definition, Layer Pairs and Vias Under SMD rules will be a graphic, as there is no definable constraint value to be displayed.

Additional examples of custom violation graphics. From left to right: Net Antennae violation; Short-Circuit violation; Un-Routed Net violation.

Additional examples of custom violation graphics. From left to right: Net Antennae violation; Short-Circuit violation; Un-Routed Net violation.

Violation Overlay

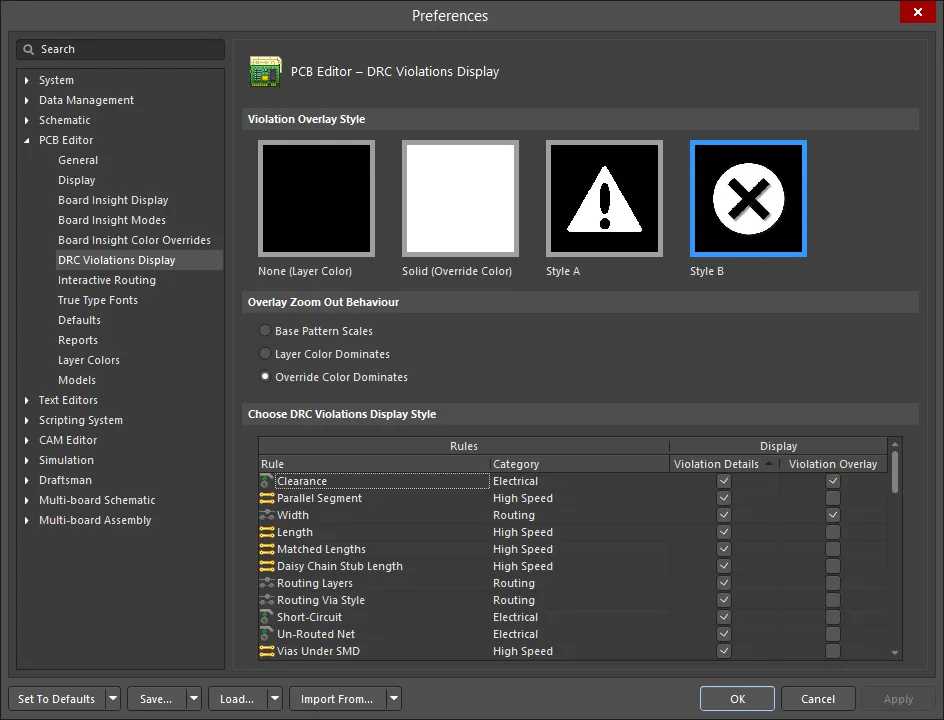

In addition to the custom violation graphics, a violations 'overlay' is available for setup and use. The overlay draws over design primitives. You have a choice of what pattern to display on the primitives from a selection of styles.

Use a violation overlay as an alternative to the custom violation graphics when displaying DRC violations.

Use a violation overlay as an alternative to the custom violation graphics when displaying DRC violations.

Using a combination of the two violation display types can prove useful in terms of providing a 'coarse' and 'fine' indication of violations. When zoomed out, the violation overlay can flag where a violation exists, then zoom in to view the detail delivered by the associated custom violation graphic.

Configuring Violation Display Preferences

Control over how DRC violations are displayed - using the custom violation graphics and/or a defined violation overlay - is specified on the PCB Editor - DRC Violations Display page of the Preferences dialog.

Configure how DRC violations are displayed in the design space - using custom graphics and/or a defined violation overlay - as part of your software preferences.

Options available allow you to:

-

Choose the style of violation overlay used using the Violation Overlay Style - error markers can be shown in one of the four following ways. Click to select your preferred style:

-

None (Layer Color) - error markers are displayed in the layer color, and therefore, are not visible.

-

Solid (Override Color) - error markers are displayed in the Error Marker layer color.

-

Style A - error markers are displayed as a warning triangle.

-

Style B - error markers are displayed as a dot with a cross inside.

-

Determine violation overlay display behavior when zooming out using the Overlay Zoom Out Behavior - error markers will do the following as you zoom out:

-

Base Pattern Scales - the error markers are scaled regardless of the zoom level (the type of marker is determined by the Violation Overlay Style selected above).

-

Layer Color Dominates - as you zoom out the error markers become a solid area of color in the layer color.

-

Override Color Dominates - as you zoom out the error markers become a solid area of color in the Error Marker layer color.

-

Choose the display style used, on a per-rule basis, in the Choose DRC Violations Display Style region. Enabling the Violation Details option for a rule type will use the associated custom violation graphics to display the DRC violations of that rule. Enabling the Violation Overlay option will display the violations using the specified overlay style. By default, the Violation Details display style is enabled for all rule types, and the Violation Overlay Style display is enabled only for Clearance, Width and Component Clearance rules.

Right-click within the grid to access a menu of commands to quickly enable or disable use of a violation display type for all rule types. Commands are also available to quickly enable the display of violations - detailed graphics or overlay styles - for only those rules currently being used in the design.

Defining Violation Coloring

To give further flexibility when displaying rule violations in the design space, the two violation display types - violation details (custom violation graphics) and violation overlay - have separate associated system colors. This allows you to differentiate between the two using different, distinct colors. Color assignment is performed in the System Colors section on the Layers & Colors tab of the View Configuration panel:

-

Violation Details – uses the Violation Markers system color (for waived violations using this display style, uses the Waived Violation Markers system color).

-

Violation Overlay – uses the DRC Error Markers system color (for waived violations using this display style, uses the Waived DRC Error Markers system color).

Specify different coloring for the two violation display types, and enable/disable their display as required.

Specify different coloring for the two violation display types, and enable/disable their display as required.

For the violation display type to be used, ensure that the visibility icon (to the left of the color swatches) is enabled (

), otherwise, the associated violation details or violation overlay will not be displayed.