上级页面:Altium NEXUS设计演示教程

主页面:PCB设计规则参考、设计规则检查(DRC)

PCB编辑器是一种规则驱动型设计环境——在此环境中,您可以定义多种可用于通过检查确保电路板完整性的设计规则。通常,您应在设计开始时设置设计规则。您可以通过在线DRC功能,监控启用的规则,并立即高亮显示任何检测到的设计违规行为。您还可以运行一个批DRC,以测试设计是否符合规则并生成一份报告,详细说明已启用的规则和任何检测到的违规行为。

在本教程的前半部分,我们一起学习了如何检查布线设计规则,如何根据电源网络添加新的宽度约束规则,以及电气间距和布线过孔样式规则。除此之外,当创建一个新电路板时,还将自动定义多项其他设计规则。

违规显示配置

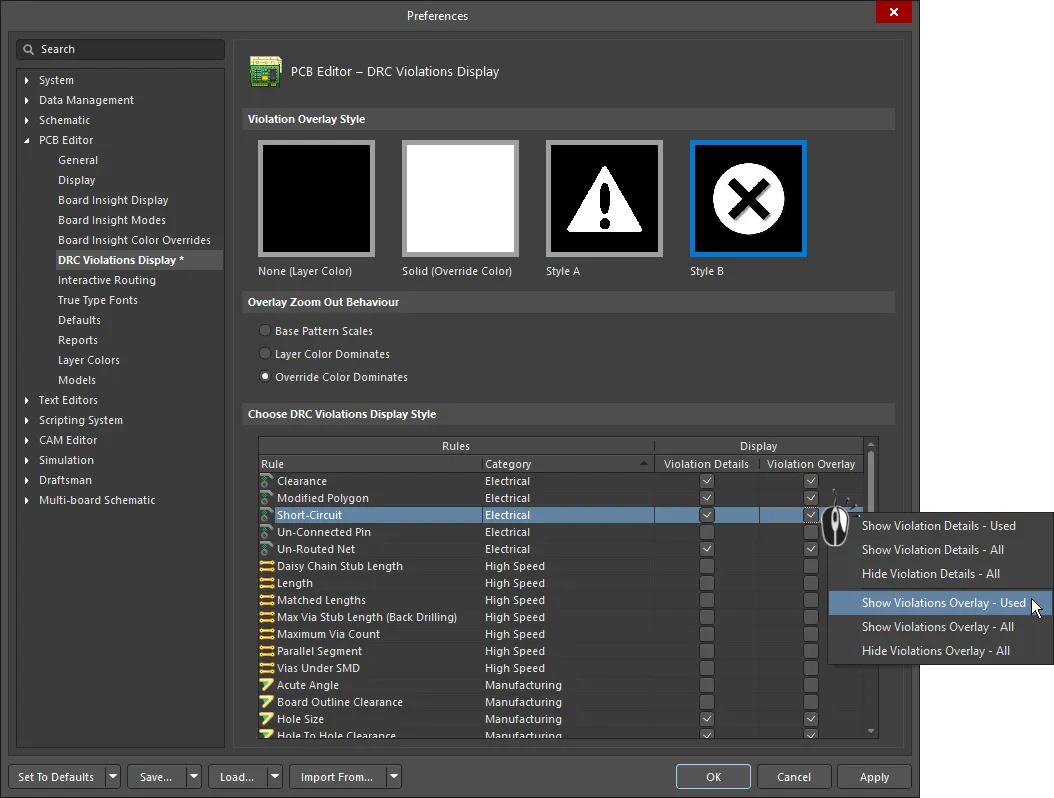

Preferences页面:PCB编辑器 - DRB违规显示

必须在进行违规检查前,了解违规是如何显示的。

Altium NEXUS拥有两种各具优势的设计违规显示技术。您可以在Preferences对话框的PCB Editor – DRC Violations Display页面,对显示技术进行配置。

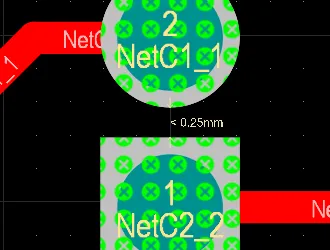

- 违规显示——以针对DRC Error Markers所选的颜色(在View Configuration面板中进行配置;按L键将其打开)高亮显示错误基元,进行违规识别。进行缩小操作时,其将默认以纯色显示基元,而进行放大操作时,其将切换为所选的Violation Overlay Style。默认选择Style B - 一个圆圈里有个叉。

-

违规详细信息——当您进一步放大时,将添加Violation Detail(如启用),详细显示错误性质。Violation Detail可包括:

- 违规地点信息。

- 必要时,将出现一个指示违规类型的图标;例如,细交叉线表示发生短路。

- 显示违反的规则设置的数值,例如,<0.25毫米。

即可以颜色叠加形式显示违规,亦可作为详细讯息显示,并使用不同符号,显示错误类型的不同细节。

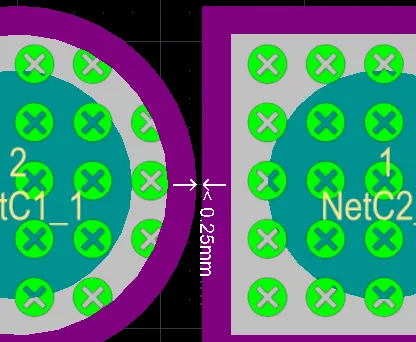

当您将此更改放大至所选的Violation Overlay Style(第二张图)时,违规将以纯绿色显示(第一张图);当您进一步放大时,将添加Violation Details(第三张图)。

准备运行Design Rule Check(DRC)

- 选择

» View Configuration(快捷键:L),并确认DRC Error可见性选项(System Colors部分)已启用,以显示DRC错误标记。

» View Configuration(快捷键:L),并确认DRC Error可见性选项(System Colors部分)已启用,以显示DRC错误标记。

- 确认已在Preferences对话框的PCB Editor – General页面启用Online DRC(Design Rule Checking)系统。保持Preferences对话框打开,并切换至对话框的PCB Editor – DRC Violations Display页面。

- 在Preferences对话框的PCB Editor – DRC Violations Display页面,配置违规则设计空间的显示方式。有两种各具优势的违规显示方式。

- 对于本教程,请右键单击Preferences对话框PCB Editor – DRC Violations Display页面的Choose DRC Violations Display Style区域,并选择Show Violation Details – Used,然后再次右键单击并选择Show Violation Overlay – Used,如上图对话框所示。

- 单击OK,以保存更改并将Preferences对话框关闭。此时,您即可检查设计是否存在错误。

所需规则将取决于设计的性质;没有哪一组规则能够适合所有设计。进行违规检查时,请牢记。首先要自行确定是否需要启用某项规则。如果您正在尝试弄清楚PCB Rules and Constraints Editor中的某项规则的功能,请单击规则约束区域内的任意位置,并按F1键,以显示关于具体规则的更多信息。

Rule Checker的配置

对话框页面: Design Rule Checker

通过运行Design Rule Checker,检查设计是否违规。运行Tools » Design Rule Check命令,以打开对话框。此对话框可用于在线和批量DRC配置。

DRC报告选项

DRC Rules to Check

运行Design Rule Check(DRC)

单击对话框底部的Run Design Rule Check按钮,以进行设计规则检查。单击按钮时,DRC将运行,然后:

- Messages面板将打开,并列出所有检测到的错误。

- 如果在对话框的Report Options页面启用了Create Report File选项,则Design Rule Verification Report将在一个单独文档标签中打开。本教程的报告见下文。

- 报告的上半部分将详细显示启用的待检查规则以及检测到的违规数量。单击某条规则,跳转至检测到的错误。

- 违规规则总结下方将显示每条违规的详细信息。

- 报告中实时显示相关链接。单击某项具体错误,以跳转返回电路板并在电路板上检查该错误。请注意,需要在Preferences对话框的System – Navigation页面中配置该单击动作的缩放比例。通过实验,确定合适的缩放比例。

报告的上半部分将详细显示启用的待检查规则以及检测到的违规数量。单击某条规则,跳转至检测到的错误。

报告的上半部分将详细显示启用的待检查规则以及检测到的违规数量。单击某条规则,跳转至检测到的错误。

报告的下半部分将显示每条违反的规则,以及错误中的对象列表。单击某个错误,以跳转至PCB上的对象。

Locating the Error Condition

定位错误状态

当您刚接触该软件时,一长串的违规最初可能会让您感到不知所措。管理此问题的一个好方法是在设计过程的不同阶段,禁用和启用Design Rule Check对话框中的规则。如果发现违规,则不建议禁用设计规则本身,而仅需禁用规则检查。例如,在电路板完全布线之前,您总是需要禁用Un-Routed Net检查。

了解错误状态

当发现某个错误后,您如何了解错误的偏差程度?作为设计人员,您需要了解此项基本信息,以确保能够决定如何以最好的方式解决此错误。

例如,如果规则表示阻焊层的最小允许间距为0.25毫米,而实际间距为0.24毫米,则情况不是很糟糕,而您或许可以通过调整规则设置接受该数值。但是,如果实际间距值为0.02,则此情况可能无法通过调整规则设置解决。

PCB编辑器包括三个便利的测量工具:Measure Distance、Measure Selected Objects和Measure Primitives;可在Reports菜单中,使用上述三个工具。

除实际测量距离外,还有多种可用于发现规则偏离程度的方法。您可以使用:

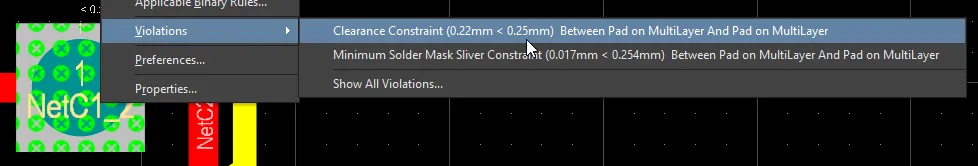

- 右键单击Violations子菜单,或者

- PCB Rules And Violations面板,或者

- Messages面板中包括的详细信息;实际值将与规定值一同详细说明(例如,0.175毫米 < 0.254毫米)。

Violations子菜单

右键单击Violations子菜单之前已在Existing Design Rule Violation部分描述。

如下图所示,Violations子菜单详细描述了实测状态与规则规定值之间的对比情况。

请右键单击某项违规,以检查违反了哪条规则及违规情况。

PCB Rules And Violations面板

面板页面:PCB Rules And Violations

您可以通过PCB Rules And Violations面板,定位并了解错误情况。

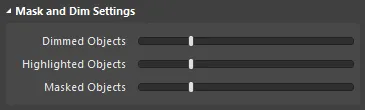

请注意,PCB Rules And Violations面板顶部有一个可用于选择Normal、Dim或Mask的下拉菜单。Dim和Mask为显示过滤器模式;在此模式下,相关对象以外的所有内容均将被隐藏,而仅以正常显示强度显示所选对象。Dim模式适用于过滤器,但是仅允许对所有设计空间对象进行编辑。Mask模式将滤除所有其他设计空间对象,而仅允许对未滤除的对象进行编辑。

隐藏显示量将由View Configuration面板View Options标签Mask and Dim Settings部分中的Dimmed Objects和Masked Objects滑块控制按钮控制。当您应用Mask模式或Dim模式时,请对这些滑块进行实验。

清除过滤器时,您可以单击PCB Rules And Violations面板顶部的Clear按钮,或者按下Shift+C快捷键。此项过滤功能在忙碌的设计空间非常有效,并且还可以用在PCB面板和PCB Filter面板中。

违规解决方法

作为一名设计人员,您必须了解解决每一种设计规则违规的最恰当方法。让我们从阻焊层错误开始,因为它们既具有相关性,亦有阻焊层设置更改的影响。

阻焊层最小间距违规

设计规则参考:阻焊层最小间距

阻焊层是指涂敷在电路板外表面,为铜提供防护绝缘覆盖的漆状薄层。在阻焊层上为元件开孔,并将导线焊到铜上。上述开孔将作为对象,显示在PCB编辑器中的阻焊层上(请注意,阻焊层将在底片中定义——在实际阻焊层中,您看到的对象将变为孔)。

在制造过程中,可以使用不同技术涂覆阻焊层。成本最低的方法是,通过阻焊层将其丝印到电路板表面上。为了解决层对齐问题,阻焊层开孔尺寸通常将超过焊盘;例如,默认设计规则中,扩展值为4密尔(约0.1毫米)。

还有其他阻焊层涂覆技术,可提供优质的层对准度和更加准确的形状定义。如果使用这些技术,则阻焊层的扩展量将更小,甚至为零。缩小阻焊层开孔,将降低出现阻焊层间距或丝印层与阻焊层间距错误的概率。

阻焊层间距错误。紫色表示各焊盘周围的阻焊层扩展量。

如果不考虑用于制造成品电路板的制造技术,则无法解决阻焊层错误。

例如,如果其为用于高附加值产品的复杂多层电路板,则很有可能应用优质的阻焊层技术,以减小或消除阻焊层扩展量。然而,简单的双面电路板(例如,本教程中所用电路板)更加倾向于作为低成本产品进行制造,因此需要使用低成本的阻焊层技术。这意味着,通过减小整个电路板的阻焊层扩展量,解决阻焊层间距错误,并不总是一种合适的解决方案。

类似于PCB设计的许多方面,在解决上述问题时,需要以一种集中的方式进行深思熟虑的权衡,以将其影响降到最低。

请在尝试检查和解决阻焊层错误前,启用阻焊层显示。如果不可见,则按下L键,以打开可启用该层的View Configuration面板。

解决Solder Mask Sliver违规

解决此类违规时,您可以:

- 增大阻焊层开孔,以彻底消除晶体管焊盘之间的阻焊,或者

- 减小可接受的最小间距宽度,或者

- 减小阻焊层开孔,以将间距增加到可接受宽度。

做出此项设计决定时,您需要充分考虑您将要使用的元件知识以及制造和装配技术。通过在阻焊层上开孔,以彻底消除晶体管焊盘之间的阻焊层间距,意味着在这些焊盘之间产生焊桥的可能性更大,而减少阻焊层开孔仍会留下可能可接受或不可接受的间距,并且还可能造成掩模与焊盘之间出现对准度问题。

对本教程而言,您应组合使用选项二和选项三,根据该电路板上使用的设置,将最小间距宽度降至一个合适的数值,并同时减小阻焊层的扩展量,但是仅适用于晶体管焊盘。

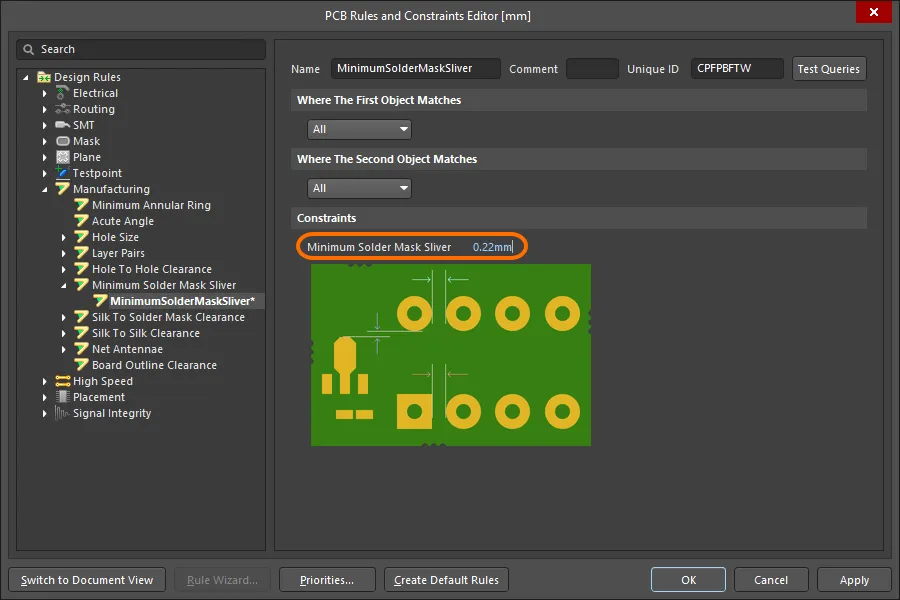

- 第一步是减小允许的间距宽度。为此,请打开PCB Rules and Constraints Editor,然后在Manufacturing部分,找到并选择现有的Minimum Solder Mask Sliver规则(即,MinimumSolderMaskSliver)。

-

在此设计中,焊盘间距可选用0.22毫米(约8.7密尔);请在规则的Constraints区域,将Minimum Solder Mask Sliver值设置为0.22毫米。

- 下一步是仅针对晶体管添加一条阻焊层扩展规则,以将阻焊层扩展量降为零。将阻焊层降为零,意味着阻焊层中的开孔尺寸与焊盘相同,以确保焊盘之间阻焊层间距的最小宽度等于焊盘之间的间距(0.22毫米)。在PCB Rules and Constraints Editor对话框左侧的选项树中单击Mask,以显示当前Solder Mask Expansion规则;其中应该有一条名为SolderMaskExpansion的规则。

- 通过双击,选择该规则并显示其设置;其将指定扩展值为0.102毫米(4密尔)。由于其仅适用于违规的晶体管焊盘,因此您无需编辑该数值;相反,您应该创建一个新数值。

- 添加一条新的Solder Mask Expansion规则时,请右键单击左侧选项树中的现有规则,并通过上下文菜单选择New Rule。将创建一条名为SolderMaskExpansion_1的新规则;单击该规则,以显示其设置。

-

按照如下所示,编辑规则设置:

- Name –

SolderMaskExpansion_Transistor

- Where the Object Matches – 在下拉菜单中选择Footprint,然后在出现的第二个下拉菜单中选择ONSC-TO-92-3-29-11(晶体管封装名称)

- Expansion top / bottom –

0mm

- 单击Apply,以接受更改并保持PCB Rules and Constraints Editor打开。

间距违规

设计规则参考:间距约束

有两种方式解决该间距约束:

- 通过减小晶体管封装焊盘的尺寸,增加焊盘之间的间距,或者

- 通过配置规则,允许晶体管封装焊盘之间采用更小的间距。

由于0.25毫米的间距相当宽松,而实际间隔非常接近于此值(0.22毫米),因此在此情况下,最好进行规则配置以允许采用更小的间距。为此,您可以在现有Clearance Constraint设计规则中进行间距配置,如下图所示。

丝印层间距违规

设计规则参考:丝印层间距

最后一个需要解决的错误是丝印层间距违规。丝印层间距违规通常是由标号太靠近相邻元件的轮廓造成的。您的设计可能没有任何此类违规——是否存在此类违规,取决于您放置的临近元件之间的间距忙,或者您是否已重新定位标号。单击、按住并拖动某个标号——除标号发生移动的元件中的对象以外,所有对象均将变暗;将该标号移动到一个新位置。

标号移动将受当前捕捉栅格的约束。如果当前网格间距过大,则按下Ctrl+G键,并输入一个新的栅格值。

将引起丝印层违规的标号重新定位。

解决违规后,运行一次Design Rule Check

- 本地保存PCB文件。

- 打开Design Rule Checker对话框(Tools » Design Rule Check),并确保在Report Options页面启用Create Report File选项。

- 单击 Run Design Rule Check 按钮。

- 将生成一份新报告并在一个单独标签中打开。确保其不包含任何违规。

- 如果存在违规,则返回PCB文档并解决违规,然后再次生成报告。

-

从项目中清除生成的DRC报告(此报告将在设计发布过程中生成)——在Projects面板上,从Generated\Documents子文件夹中找到报告文件,右键单击文件并选择Remove from Project命令。在此打开的Remove from project对话框中,选择Delete file选项。

使用永久删除选项,从项目中清除Design Rule Check报告文件。

- 将PCB和项目保存到Workspace中。

- 关闭PCB文件。

务必确保在生成输出前,有一份清洁的Design Rule Verification Report。

非常好!各位学员,您已经完成PCB布局并且已经可以配置输出文档和发布项目了!