主页面: 与原理图相关的更多信息

电子设计时常包含重复电路段(例如,立体声放大器,或64通道调音台)。此类设计的实现完全依赖于“多通道设计”功能集的支持。

视频多路复用器的两个解码器通道使用多通道设计结构意味着解码器通道仅需捕捉(画)一次电路原理图。

在多通道设计中,您仅需对重复电路进行一次捕捉,然后指示软件根据需要次数进行重复即可。当设计自动编译时,它会在内存中扩展,所有元件和连接均会根据用户定义的通道命名方案重复所需的次数。

您捕捉到的逻辑设计从来不是真正意义上的平面设计,源数据始终以多通道原理图的形式存在。当您将其传输至PCB布局时,物理元件和网络会自动步进所需次数。您可以完全访问可用于在原理图和PCB间切换的标准交叉探测和交叉选择工具。此外,PCB编辑器中还有一个格式复制工具。使用该工具,您可以将一个通道的布局和布线复制到所有其他通道,并轻松移动和重新调整整个通道。

动态编译

相关文章:编译和验证设计

设计连接模型将在每次用户操作后通过动态编译进行增量更新。项目编译过程将自动完成,用户无需进行任何手动操作。对于设计项目,自动编译过程将执行三项功能:

- 实例化设计层次结构。

- 在所有设计图纸之间建立网络连接。

- 构建设计的内部“统一数据模型”(UDM)。

自动编译可确保用户做出的任何设计变更将立即体现在“导航器”和“项目”面板中。

项目的编译模型被称为“统一数据模型”(UDM)。UDM包含每个设计元件的详细描述,以及它们相互连接的方式。

如需实现动态编译,您必须启用

“高级设置”对话框中的Schematic.DynamicCompiler选项(该选项默认启用)。

如需检查UDM和编译器设置之间的逻辑、电气和绘图误差,您必须首先验证项目。你可以通过从主菜单中选择“项目»验证项目”命令,或通过右键单击“项目”面板中的项目入口并从上下文菜单中选择“验证项目”命令来访问该命令。

“编译器”检测到的任何违规均将在“消息”面板中以警告和/或错误的形式列出。“编译器”将使用“项目选项”对话框的“错误报告”和“连接矩阵”选项卡(根据项目类型)上定义的选项检查源文档是否存在违规。

在Altium NEXUS 20.0之前的软件版本中,用户必须手动编译项目以构建“统一数据模型”。自Altium NEXUS 20.0起,软件会在每次用户操作后通过动态编译对设计数据模型进行增量更新(即,创建所谓的“动态数据模型”(DDM))。在动态编译中,项目将自动完成编译,用户全程无需进行任何手动操作。通过动态编译,设计连接模型将在每次用户操作后得到增量更新。

统一数据模型

为了理解多通道设计,您首先需要了解设计数据的托管方式。“统一数据模型”(UDM)是本软件的一个基本元素。在自动编译项目时,您需要创建一个单一聚合模型,这一步是设计流程的核心所在。然后,您可以使用本软件内部的众多编辑器和服务来访问、操纵模型内部的数据。统一数据模型经构建能容纳来自设计方方面面的信息(包括元件及其互连),而非将单独的数据存储运用于各类设计域。

“统一数据模型”使所有编辑器均可访问所有设计数据,并有助于交付诸如多通道设计等复杂功能。

UDM通过与层次式设计系统相结合,可提供多通道设计功能。“通道”是“图表符”内的电路——在该“图表符”下,可以有一张单一图纸,也可以有包含其他子图纸的完整项目结构分支。您还可以在通道内创建通道。在两层多通道设计中,上层通道被称为内存库,下层通道则被称为通道。

鉴于内存中已有现成可用于PCB的完整描述存在,所以您可以重复一段电路,但前提是,您必须有系统化方法来处理重复对象,例如,元件位号标识符和网络。系统化命名在“项目选项”对话框的“多通道”选项卡中定义,具体如下所述。

创建多通道设计

当设计中的一段电路重复出现时,该设计属于多通道设计。多通道设计在图表符级通过以下方式创建:

- 放置多个引用相同子原理图的“图表符”;或

- 配置单一“图表符”以按照所需次数重复引用的子原理图。

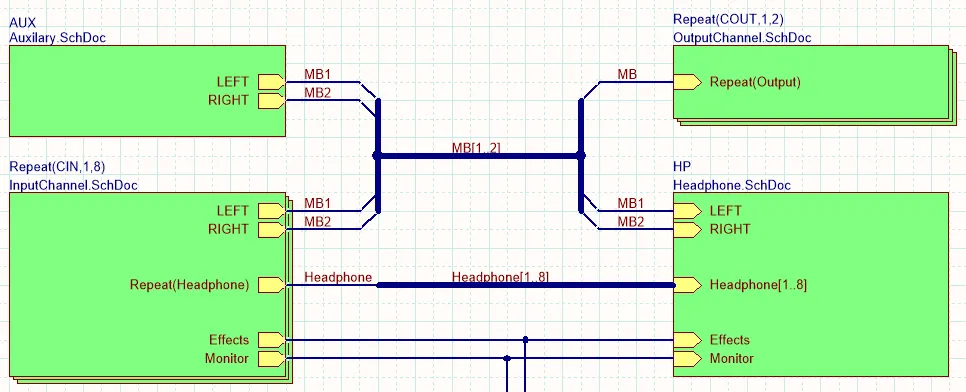

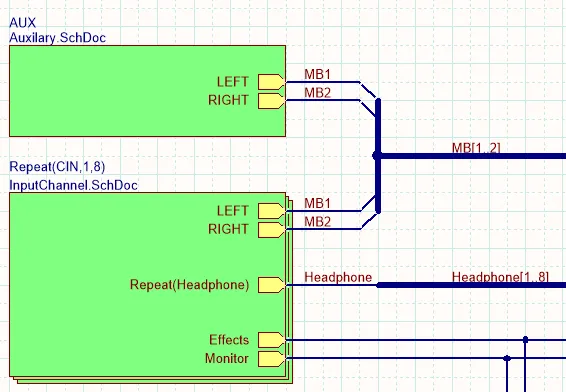

图一——四个“图表符”均引用相同子图纸(PortIO.SchDoc)。图二——使用“重复”关键字重复InputChannel.SchDoc八次,重复OutputChannel.SchDoc两次。

上图显示了创建多通道设计的两种方法。在图一中,四个“图表符”均引用相同子图纸(PortIO.SchDoc)。在图二中,通过“图表符”的“位号标识符”字段中的“重复”关键字,重复InputChannel.SchDoc八次,重复OutputChannel.SchDoc两次。

通过应用标准命名方案解析项目中重复的元件位号标识符和网络名称。例如,一种命名方案是为重复的元件和网络标识符(“网络标签”和“端口”)添加通道索引,具体如下图高亮部分所示。

请注意打开项目时出现在原理图底部的选项卡。其中,“编辑器”选项卡包含您捕捉的逻辑设计。本软件还将显示其他编译选项卡(COUT1和COUT2),它们代表即将传输至PCB编辑器的物理设计。每个物理通道都会有一个对应的选项卡。

显示逻辑视图选项卡以及传输至PCB的每个物理通道对应选项卡的编译项目。请注意重复位号标识符和网络标识符的管理方式。

通道命名方案在“项目选项”对话框的“多通道”选项卡上定义。

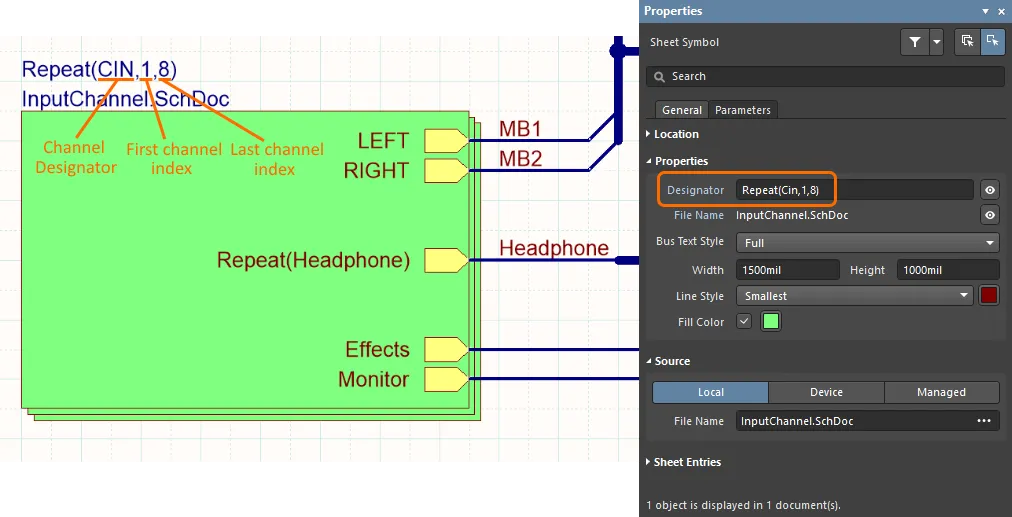

重复关键字

诚如上文所述,用户可以通过放置多个引用相同子图纸的图表符,或通过在“图表符”的“位号标识符”字段中输入“重复”关键字来重复通道。使用“重复”关键字时,“图表符”以一组堆栈“图表符”的形式绘制。

“重复”语句定义了通道位号标识符和通道数量。请注意“图表符”是如何被绘制为一组堆栈符号,以表示重复通道。

每个通道均通过一个来自“图表符位号标识符”的通道位号标识符识别。通过放置多个“图表符”实现设计通道化时,通道位号标识符是为每个“图表符”定义的“位号标识符”值。如果使用“重复”关键字进行设计通道化,则通道位号标识符是由“重复”关键字定义的ChannelIdentifier+ChannelIndex。

使用“重复”关键字时,“位号标识符”字段的语法如下:

Repeat(<ChannelIdentifier>,<ChannelIndex_1>,<LastChannelIndex_n>)

在“项目选项”对话框的“选项”选项卡上启用“

图表符新建索引”选项时,任何数位或数字均可用作重复“图表符”的第一个或最后一个索引(包括0);最后一个索引必须始终大于第一个索引,并且不允许使用负数。

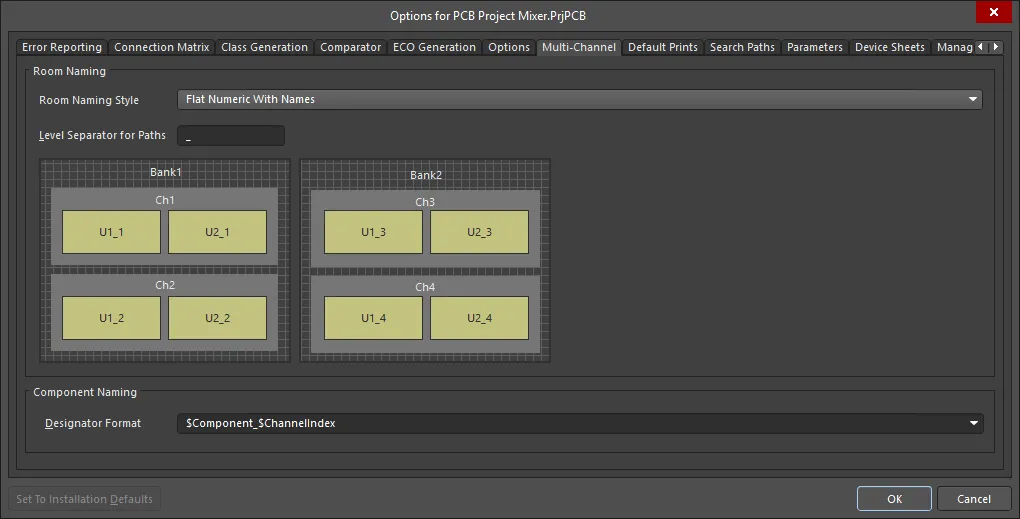

多通道命名

一次捕捉重复使用的概念(多通道设计)是在本软件统一数据模型(UDM)的基础上实现的。重复元件使用系统化命名方案命名,该方案在“项目选项”对话框的“多通道”选项卡上配置,具体如下所示。

该对话框的上半部分用于控制Room命名,下半部分用于控制Room内的元件命名。在Room级,有2种平行式命名样式和3种层次式命名样式。通常如果设计在通道内创建通道,则您仅需选择层次式命名样式;否则,建议使用更加简短且更易于理解的平行式Room命名样式。

对于元件命名,使用$Component$ChannelAlpha或$Component_$ChannelIndex选项可以获得最简短且最容易理解的元件名称。另外,也可以使用可用关键字定制位号标识符命名方案。

重复元件(和网络)通过应用系统化命名方案进行管理。该方案在“项目选项”对话框的“多通道”选项卡上选择。

- 除元件外,“元件命名”方案还可用于唯一地标识每个通道内的网络。该方案用于重命名网络标识符(包括“网络标签”和“端口”)。

- 这些名称在原理图上的显示将在下文“显示编译名称”部分中进一步讨论。

Room的作用

Room是用于定义电路板上区域的PCB设计对象,可以通过以下两种方式使用:

- 包含对象——虽然Room像多边形对象一样放置,但它实际上是作为“放置”设计规则创建的。Room在其定义中指定了必须包含其中的对象——通常是元件。当Room移动时,Room内的所有元件也会随之移动。

- 确定其他设计规则的范围——以及自身充当规则使用。Room还可以用于确定其他设计规则的范围。例如,一个布线宽度设计规则定义了一类网络的布线宽度,而具有Room范围的更高优先级设计规则可以指定应用于Room内该类网络的不同宽度。

Room与多通道设计配合默契。本软件可以在设计从原理图编辑器传输至PCB编辑器时,根据“项目选项”对话框的“类生成”选项卡上的选项,自动为每个“图表符”创建一个Room。除了对该通道内的元件进行聚类外,Room还可以用于对其中的元件进行命名。Room及其在电路板设计过程中的作用将在本文“多通道PCB设计”部分进一步讨论。

如果您偏好使用平行式元件编号系统,则您可以通过执行“板级标注”替换系统化命名方案。它之所以被称为“板级标注”,是因为元件位号标识符仅适用于必将成为PCB的完整编译设计(物理设计)。

多通道设计中的连接

对于多通道设计,将“网络标识符范围”设置为“自动”、“层次”或“绝对层次”。鉴于本软件在编译设计时使用层次结构模型来实例化内存中的通道,因此多通道设计必须具有层次结构。

对于连接到重复通道的网络,本软件必须支持两种不同的连接要求。网络将是:

支持水平取决于用于定义通道的方法(多个“图表符”,或通过“重复”关键字)。如果设计使用多个“图表符”(每个通道有一个单独的“图表符”),则网络连接采用显式连接,由设计人员放置的导线定义。

该设计使用“重复”关键字创建多通道。

如果设计使用“重复”关键字,则适用以下连接规范。

| 将网络传递至所有通道 |

如果网络需要在所有通道上可用,则仅需将其画线至“图纸入口”即可,具体如上图中的连接到“InputChannel.SchDoc图表符”的显示器网络所示。网络“特效”、“MB1”和“MB2”亦将在所有通道上可用。总线中的网络将以相同的方式处理。当总线连接到“图纸入口”时,该总线中的每个元素在所有通道上均可用。 |

| 将网络传递至特定通道 |

如需从总线将单一网络分配到每个通道,请在“图纸入口”中使用“重复”关键字,具体如上图中的耳机总线所示(其中“图纸入口”的名称为“重复”(耳机))。遇此情形,网络“耳机1”将连接到通道“CIN1”,“耳机2”将将连接到通道“CIN2”,依此类推。如果已使用“重复”关键字创建通道,则无法将单一网络仅传递至一个通道。如有需要,您必须为每个通道放置一个单独的“图表符”。 |

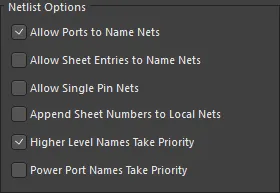

网络命名方式

最终,每个网络在PCB上仅有一个名称(一个PCB网络不能有两个名称)。本软件将自动解析具有多个名称的网络,使其在项目中仅有一个名称——您必须在多通道设计中配置命名选项以确保网络标签对您而言具有意义。网络命名选项位于“项目选项”对话框的“选项”选项卡的“网表选项”部分。

如需在多通道设计中设置上述选项,建议启用“高层次名称优先”选项,并将“网络标签”放置在连接到通道化子图纸的所有网络上。

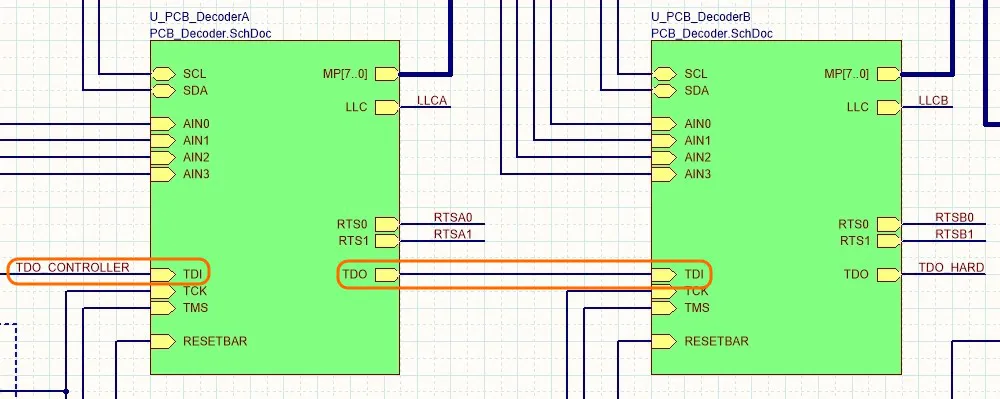

请思考下图中的示例。请注意,两个“图表符”均指向图纸PCB_Decoder.SchDoc;因此,该电路有2个通道,分别标示为U_PCB_DecoderA和U_PCB_DecoderB。

“图表符”包含一个被称为TDI的“图纸入口”(即,JTAG边界扫描链中的“测试数据输入”)。来自DecoderA的TDO(“测试数据输出”)随后连接至链中下一台设备的TDI(该设备位于DecoderB通道中)。

通过放置引用相同原理图(PCB_Decoder.SchDoc)的两个“图表符”创建两个解码器通道。

打开项目后,原理图视图底部出现通道选项卡U_PCB_DecoderA和U_PCB_DecoderB。上述选项卡显示了将传递给PCB编辑器的物理设计。在下图中,捕捉的解码器电路原理图显示在左下方的“编辑器”选项卡中,后跟该原理图的两个物理通道(U_PCB_DecoderA和U_PCB_DecoderB)。

在原始捕捉原理图中,设计人员将网络标记为TDI(图一)。请注意本软件如何根据网络名称的层次在DecoderA选项卡(图二)中应用更高层次网络名称(根据设置,在该设计中优先)。DecoderB未定义更高层次名称,因此根据在“项目选项”对话框的“多通道”选项卡上定义的命名规则(“元件命名”方案用于识别每个通道内的元件和网络),原始网络名称TDI在该通道内被标识为TDI_2(图三)。

PCB_Decoder.SchDoc原理图:图一——捕捉的原理图;图二和图三——两个通道的编译视图。

显示编译名称

多通道设计中的网络跟踪和分析容易令人困惑,这是因为一方面必须更改名称以识别重复网络,但另一方面又必须确保名称的唯一性。为了解决这个问题,我们提供多个控制编译对象名称显示的选项,其中包括元件“位号标识符”、“网络标签”和“端口”。此外,我们还为“图号”和“文档编号”提供显示控制选项。当您准备生成打印类型输出时,此类选项将发挥重要作用。

编译对象名称的显示在“优选设置”对话框的“原理图——编译器”页面中配置,具体如下图所示。

配置编译对象名称的显示(上标对元件位号标识符很有帮助)。

通常,您会希望显示位号标识符和“网络标签”,而显示“端口”则有助于诊断问题。此外,“图号”和“文档编号”亦很重要,必须正确配置。您可以在“设计标注”部分找到有关元件和图纸编号相关信息的链接。

如果选择“必要时显示上标”选项,则当前文档视图将纳入来自不可见视图的对象标识符作为上标。请根据您的偏好进行配置。

多通道设计的通道2(CIN2)视图。请注意原始逻辑原理图的位号标识符和网络名称作为上标显示的方式。

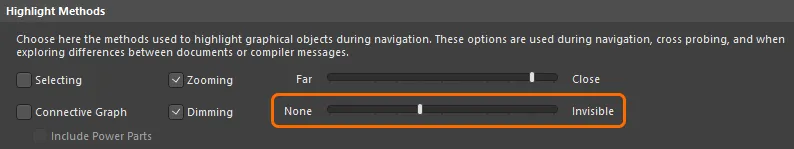

想知道为什么某些原理图元素在通道(物理)选项卡中变暗?默认以标准显示强度显示可在通道选项卡中编辑的对象,而不可编辑的对象则变暗。在“优选设置”对话框的“系统——导航”页面中设置调光。使对象变暗的好处是它有助于防止您尝试执行不受支持的编辑操作,例如,在通道选项卡中移动“网络标签”。根据需要设置“调光”级。

解决多个网络名称错误

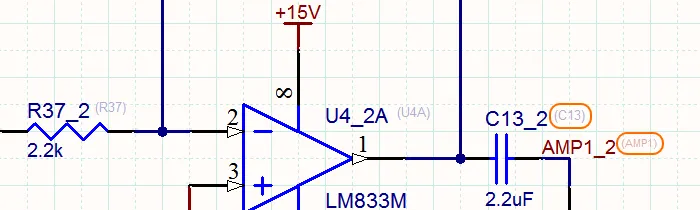

原理图编辑器的错误检查选项默认标记具有多个名称的网络的每个实例。当您有意更改名称时,可能会发生这种情况(例如,当网络输入一个图表符,但您希望在该图纸中使用不同名称时)。下图显示了一些相关示例,其中,在顶层图纸上“左”输出和“右”输出被绑定到一条总线中,但它们在“图纸入口”中被称为“左”和“右”。

使用总线是因为它允许两个输出通道由带有“重复”关键字的单个图表符表示。如果左通道和右通道使用单独的导线,则设计人员需要为“左”输出通道和“右”输出通道放置单独的图表符(均指向同一子原理图图纸),然后通过画线将每个输出分别与其输出图表符连接。

您必须指示软件如何处理多个网络标识符。为此,您需要:

- 在“项目选项”对话框的“错误报告”选项卡中,将“网络有多个名称”错误检查设置为“不报告”。这一选项并非首选,因为它会在整个设计过程中阻止对该错误条件的所有检查。或者,您也可以,

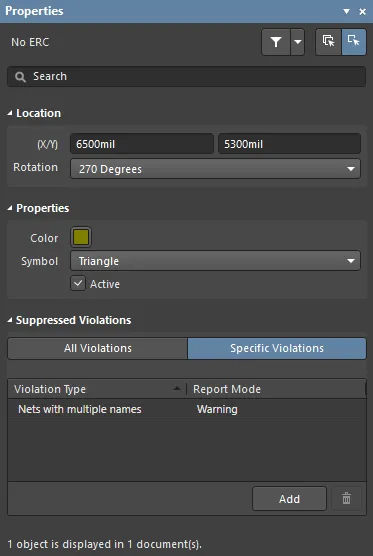

- 在受影响网络上放置一个“特定无ERC指令”。具体做法是右键单击“消息”面板中的“错误/警告”,并为该违规命令选择“放置特定无ERC标记”。这样做将使您进入“无ERC对象放置”模式,光标上将附带一个预先配置且随时可以放置在出错网络上的“特定无ERC”标记。放置标记后,双击配置样式和颜色。

请注意用橙色圈出的小三角形;这是一个特定的“无ERC标记”,用于禁用网络“MB1”和网络“MB2”上的“重复网络名称”错误。

设计标注

设计输入的一个关键是对设计进行标注(即,为每个元件和每个原理图分配唯一标识符)。在多通道设计中,设计输入分两个阶段进行。首先,必须对您放置的元件和绘制的图纸进行编号;然后,必须对通过重复通道实例化的元件和图纸进行编号。

► 了解有关“标注元件”的更多信息。

► 了解有关“图纸编号”的更多信息。

多通道PCB设计

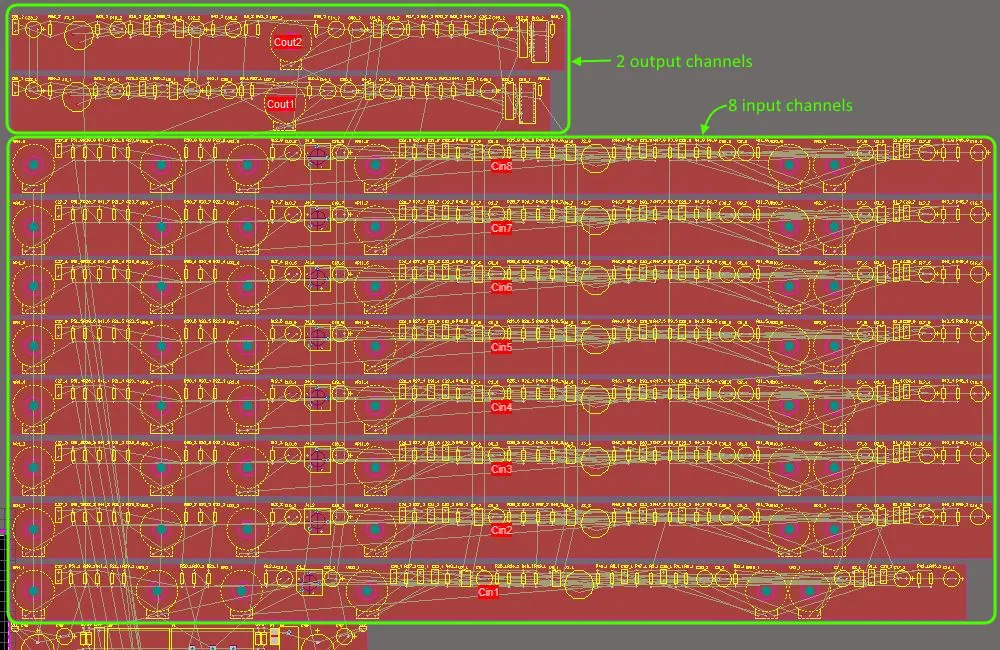

将设计从原理图编辑器传输至PCB编辑器时,如果在“项目选项”中启用了“Room创建”,则每张图纸中的元件均会聚集在一个PCB放置Room内。

在多通道设计中使用Room的一大优势是PCB编辑器支持将布局和布线从一个Room(通道)复制到其他Room(通道)。此外,Room还可以像单一对象一样移动,从而简化PCB上的通道排列过程。

设计完成后,八个输入和两个输出通道从原理图编辑器传输至PCB编辑器(红色区域是Room)。

PCB Room的作用

Room是用于定义电路板上区域的PCB设计对象,可以通过以下两种方式使用:

- 包含对象——虽然Room像多边形对象一样放置,但它实际上是作为“放置”设计规则创建的。Room在其定义中指定了必须包含其中的对象——通常是元件。当Room移动时,Room内的所有元件也会随之移动。

- 确定其他设计规则的范围——以及自身充当规则使用。Room还可以用于确定其他设计规则的范围。例如,一个布线宽度设计规则定义了一类网络的布线宽度,而具有Room范围的更高优先级设计规则可以指定应用于Room内该类网络的不同宽度。

Room与多通道设计配合默契。本软件可以在设计从原理图编辑器传输至PCB编辑器时,根据“项目选项”对话框的“类生成”选项卡上的选项,自动为每个“图表符”创建一个Room。除了对该通道内的元件进行聚类外,Room还可以用于对其中的元件进行命名。

实用Room操作命令

- Design » Rooms - 该子菜单有许多用于定义和修改Room的实用命令。

- Design » Rooms » Copy Room Formats - 使用该命令将一个Room(通道)的布局和布线复制到其他Room(通道)。

- Design » Rooms » Move Room - 可以通过单击并按住Room,将其移动至光标下方没有其他设计对象的任何位置。光标将对齐到最近的元件焊盘或Room顶点(以较近者为准)。当您无法在不单击设计对象的情况下单击并按住Room时,请使用该命令。

- Edit » Select » Room Connections - 使用该命令选择起始于焊盘并在Room内结束的所有铜段。

元件链接方式

Each schematic component links to its PCB component through a Unique Identifier (UID). The UID is assigned when the schematic component is placed on the sheet and is then assigned to the PCB component when the design is transferred to the PCB editor. This scheme would be adequate for a simple design but is not capable of supporting a multi-channel design, where the same schematic component is repeated in each physical channel (so the PCB components would have the same UID).

To cater for this, the UID for the PCB component is created by combining the UID of the parent Sheet Symbol with the UID of the schematic component. The syntax of the PCB UID changes slightly, depending on how the multi-channel design has been created.

For a multi-channel design created by placing multiple Sheet Symbols that all reference the same schematic sheet, then each Sheet Symbol can provide a unique ID, so the PCB UID has the format:

\SheetSymbolUID\SchComponentUID

For a multi-channel design created using the Repeat keyword, there is only 1 Sheet Symbol UID available, so the PCB UID also includes the ChannelIndex, in the format:

\ChannelIndex+SheetSymbolUID\SchComponentUID

Component links are managed via the Edit Component Links dialog (Project » Component Links command in the PCB editor). When changes are applied in this dialog, the PCB UIDs are updated to match the schematic UIDs.

在PCB上显示位号标识符

在多通道设计中,位号标识符串可能难以定位,这是因为它们可能很长。除了选择生成短名称的命名选项外,您也可以选择仅显示原始逻辑元件名称。例如,C30_CIN1将显示为C30。如选择该选项,则您需要在电路板上添加一些其他符号,以指示单独的通道(例如,在元件丝印层上的每个通道周围绘制一个框)。

您可以在PCB编辑器“属性”面板的“其他”部分(“视图»面板»属性”)中,选择在PCB上显示“逻辑”或“物理”位号标识符。如果您选择在多通道设计中显示元件的逻辑位号标识符,则这些位号标识符将显示在PCB上以及生成的任何输出中(例如,印制成品和Gerber输出)。但是,在生成“材料清单”时将始终使用唯一的物理位号标识符。

► 了解有关“标注元件”的更多信息。

如果您偏好使用平行式元件编号系统,则您可以通过执行“板级标注”替换系统化命名方案。它之所以被称为“板级标注”,是因为元件位号标识符仅适用于必将成为PCB的完整编译设计(物理设计)。

“板级标注”存储在.Annotation文件中。该文件将每个逻辑指位号标识符映射到分配的物理位号标识符。由于该文件是项目的一部分,系统会提示您对其进行保存。

参数化多通道层次式设计

复用设计(例如,将您当前项目上的“图表符”链接到您公司的首选电源原理图)所面临的一大挑战是不同设计所使用的元件值并不总是固定的。

参数化层次式设计正好能够解决这个问题——它允许您将元件值的规范从原理图图纸移动至引用该图纸的图表符中。此项功能还可以与多通道设计完美配合,使您能够在每个通道中使用不同的元件值。请注意,参数化层次式设计要求每个通道均有自己的图表符,因为这是存储元件值的地方。

例如,图形均衡器可以使相同电路重复多次,各个通道间的唯一区别是所使用的元件值不同。因此,电容器可以在不同通道中分别取值0.12µF、0.056µF和0.033µF。实现不同取值很简单,您只需在引用每个通道的“图表符”中指定相关值即可。借助该功能,您将彻底告别需要创建大量只有元件值不同的相似原理图的烦恼。

参数化元件的定义方式是:首先声明元件值为上述图表符的参数,然后在目标元件上引用该参数。下图左侧显示了图形均衡器的顶层图纸,旁边是“1KHz图表符”的参数。该图还显示了较低层次捕捉原理图和经过编译的1KHz通道(通过下方选项卡选择)。

每个通道具有不同电容和电阻值的图形均衡器;实际元件值在“图表符”中定义,因此仅需捕捉一个较低层次原理图即可。

每个“图表符”参数亦使用较低层次图纸上的原理图元件中的参数值进行定义,具体如下图所示。每个“图表符”参数值均被传递至相关原理图元件,然后再映射到元件的“注释”字段。请注意,如果直接使用一个“值”参数(而非元件的“注释”参数)显示原理图元件的值,则仅需将“图表符”参数映射到元件的“值”参数(值= C2_Value)并使其可见即可。

因为“值”参数的值为=C2_Value,编译器将自动在更高层次的“图表符”中查找实际元件值。

参数化层次结构并不仅限于元件值。您还可以参数化地引用任何元件参数,以及原理图图纸上的其他对象文本标签,但基本连接元素(例如,元件ID、“端口”对象和文档文件名)除外。如果您从较高层次图表符引用参数,则系统将搜索层次结构,直至找到匹配参数为止。

下载参考设计\Parametric Hierarchy\AudioEqualizer.PrjPcb,查看正确配置“图表符”和“元件”参数的示例。

如果您在下载参考设计时遇到问题: