Parent page: More about Schematics

It's the components and how they connect to each other that creates your unique, electronic circuit. In the schematic you create the logical representation of your design by connecting the component pins together, to design the printed circuit board you place the physical components and create the same connectivity with tracks.

Physical and Logical Connectivity

Copy Link

Copied

On the schematic you can create that connectivity by drawing a wire from one component to another - this is referred to as physical connectivity.

You can also connect one pin to another by placing a short Wire and a Net Label on each component pin - when the design is compiled the software identifies these two net-sections and connects them to form a single net - this type of connectivity is referred to as logical connectivity.

Physical connectivity allows a reader to follow each wire as they study the circuit, but lots of Wires can result in a dense and busy schematic. On the other hand, Net Labels reduce the amount of wiring, but instead the reader must scan the sheet to find all potential connections. As the designer you are free to decide which connectivity model best suits your design, including a mixture of both techniques.

Place wires to create physical connectivity, or use net labels to create logical connectivity.

As well as creating logical connectivity within a schematic sheet, there are also objects for creating logical connectivity between schematic sheets. The way this connectivity is created will depend on how you structure your schematic, either as a flat design, or as an hierarchical design, more about this below.

There are number of different net identifiers that can be used to connect between sheets.

Objects Used to Create Connectivity

Copy Link

Copied

The schematic editor includes the following objects that are used to create connectivity, collectively these objects are referred to as net identifiers.

| Net Identifier |

Function |

| Bus |

Used to bundle a set of nets, for example Data[0..7]. Nets must be named sequentially using a specific naming scheme (eg Data0, Data1,... Data7), and this naming then dictates the Bus name, for example Data[0..7]. |

| Bus Entry |

Graphical device provided to support ripping 2 different nets from opposite sides of a Bus line, without creating a short between the 2 nets. Not required in other situations. |

| OffSheet Connector |

Used to connect a net from one schematic sheet to another sheet (not within the same sheet). Only supports horizontal connectivity (flat designs). OffSheet Connectors have limited functionality when compared to Ports. |

| Net Label |

A net identifier used to create connectivity to other Net Labels with the same name, on the same schematic sheet. The net is automatically named by the Net Label. Net Labels can be placed on component pins, wires and buses. Note that Net Labels do not connect between sheets, unless the project options are configured to use a Net Identifier Scope of Global. |

| Pin |

Pins are placed in the schematic symbol editor, to represent the physical pins on the component. Only one end of the pin is electrically active, which is sometimes referred to as the hot end of the pin. |

| Pin, hidden |

During component creation, a component pin can be hidden and a net name assigned to it. Hidden power pins with a net assigned are automatically added into the net of that name. Use this feature to automatically netlist hidden component power pins. Hidden pins can be exposed on the schematic if necessary, for example if they need to be connected to different power supply nets. |

| Port |

Used to connect a net from one schematic sheet to another. Connectivity can be vertical in a hierarchical design, or horizontal in a flat design (vertical and horizontal designs are explained below). Port names are used to name nets if the Allow Ports to Name Nets option is enabled in the Options for Project dialog, in this situation Ports will also connect within a schematic sheet. |

| Power Port |

Creates connectivity to every other power port of the same name, throughout the schematic project, regardless of the design structure. The net is automatically named by the Power Port. This net can be localized to a specific schematic sheet if required. |

| Sheet Entry |

Placed within a Sheet Symbol, to create connectivity to a Port of the same name on that Sheet Symbol's child sheet. Sheet Entries are used as net names if the Allow Sheet Entries to Name Nets option is enabled in the Options for Project dialog. |

| Signal Harness |

Used to bundle any combination of nets, buses and lower-level signal harnesses. |

| Wire |

A polyline electrical design primitive that is used to form electrical connections between points on a schematic. A Wire is analogous to a physical wire. |

Different types of net identifiers that have the same name do not automatically connect to each other, it depends on how the net naming options are configured. These options are discussed below.

How The Design Structure Affects the Connectivity

Copy Link

Copied

Related article: Multi-sheet and Multi-channel Design

If the design does not fit onto a single schematic sheet, it can be spread over multiple sheets. There are two distinct models for organizing and creating connectivity in a multi-sheet schematic: either as a flat design, which you can think of as one large schematic sheet that has been cut up into a number of smaller sheets; or as a hierarchical design, where the sheets are linked in a grandparent-parent-child type structure.

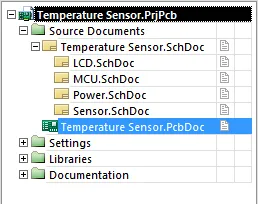

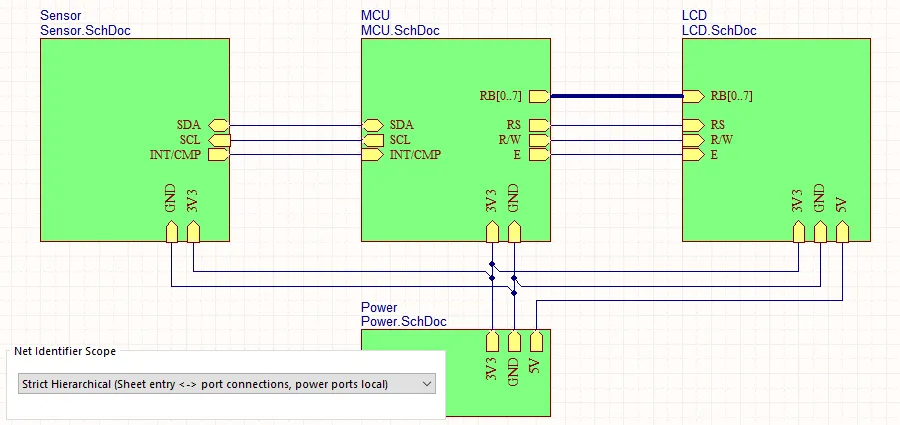

Multi-sheet designs are implemented by placing a Sheet Symbol on the parent sheet, which represents and links to the child sheet, as shown in the image below.

Sheet Symbols represent (and link to) lower-level sheets. In a flat design this structure can only be one level deep, in a hierarchical design there is no limit to the depth.

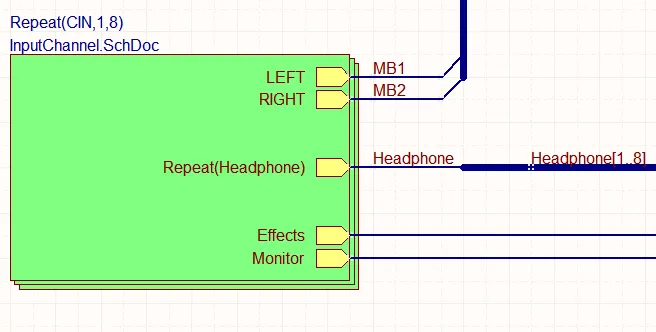

So just what determines if a design is flat or hierarchical? It is The Net Identifier Scope that defines how you want the sheet-to-sheet connectivity to be created. This is set in the Options tab of the Options for Project dialog.

A project can contain only one top sheet, all other source documents must be referenced by sheet symbols. No sheet symbol may reference the sheet it's on, or any sheet higher up the ladder, as this will create an irresolvable loop in the structure.

Flat Design

Related article: Multi-sheet and Multi-channel Design

A design is referred to as a flat design when the connectivity is created directly from one sheet to another sheet, it does not pass through Sheet Symbols on the parent sheet. In a flat design the sheet symbols simply represent (and reference) the child sheets. All sheets in the design appear at the same level in the Projects panel, because there is no hierarchy. Both of the images below show a flat design.

Flat designs are simpler to create. A flat design can include a top sheet with a Sheet Symbol for each child sheet, but this is optional as this top sheet is not used to create sheet-to-sheet connectivity. For a small design which only has two or three schematic sheets in it, you might decide that a top sheet does not add any value. Once the sheet count gets higher, a top sheet can help the reader understand the functionality of the circuit design from the way that the logical blocks (Sheet Symbols) are arranged on the sheet.

The same design, shown without a top sheet (left) and with a top sheet (right) - both are examples of a flat design.

In a flat design, the connections between the sheets can be created by Ports, Offsheet Connectors, Power Ports and Net Labels, as shown in the image earlier with the magnifying glass. The recommended approach is to use Net Labels within each sheet and Ports to connect between sheets. Ports offer more features than Off-Sheet Connectors, including the ability to add Port Cross References, which adds a SheetName[GridReference] to each port, referring to a matching port on another sheet, as shown in the image below.

There is no limit to the number of sheets in a flat design.

Port Cross References have been added next to each Port, indicating the target sheet and grid reference for the matching Port.

A design is flat when the connectivity is directly from one sheet to another - this connective behavior is defined by setting the Net Identifier Scope to Automatic, Flat or Global. Note that if you choose to use a mixture of Ports and Net Labels to create sheet-to-sheet connectivity, you cannot use the Automatic option, in this situation you must manually set the Net Identifier Scope to Global.

Hierarchical Design

Main article: Multi-sheet and Multi-channel Design

A design is referred to as hierarchical when the sheet-to-sheet connectivity is from a Sheet Symbol, down to the child sheet referenced by that Sheet Symbol. At the net level, the connectivity is created between a Sheet Entry in that Sheet Symbol, and a Port with the same name as the sheet entry, on the child sheet. This type of connectivity is also referred to as vertical connectivity, since the sheet-to-sheet connectivity that is created is only up and down, between a parent sheet and its child sheet.

In an hierarchical design, the net-level connectivity is from a Sheet Entry on the parent sheet, down to a matching Port on the child sheet.

Hierarchical design has two major strengths.

- The first is the ability to show the reader the functionality of the design in the way that the schematic sheets have been structured and presented as logical blocks (Sheet Symbols). The top level schematic presents the design as a set of high-level functional blocks, with the arrangement of the blocks reflecting their place in the traditional left-to-right, input-to-output, flow of the overall circuit. These blocks can be further broken down into smaller blocks if required, allowing the lowest-level schematics that carry the components to have a relatively simple structure, with a low component count. Because each sheet is relatively simple the measured sheet size can be kept small, a big advantage when it comes to printing the schematic.

- The other major advantage is that it is generally much easier to trace a signal through a hierarchical design, as the reader only needs to match a Sheet Entry on the parent sheet to the Port on the child sheet, and can trace the signal along the wiring within each sheet.

There is extra work in building up a hierarchical design - the Sheet Symbols require Sheet Entries, and the top sheet must be wired to carry the signals from one Sheet Symbol to another. The software includes a tool to help keep the Sheet Entries synchronized with the child-sheet Ports (Design » Synchronize Sheet Entries and Ports for all Sheet Symbols, or Right-click » Sheet Symbol Actions » Synchronize Sheet Entries and Ports for a single Sheet Symbol). It also includes tools to help break a larger design down into small chunks (Right-click » Refactor » Move Selected Sub-circuit to Different Sheet). To learn more about these restructuring and refactoring tools, refer to the Design Refactoring page.

A hierarchical design can be any depth, and include any number of schematic sheets.

A design is hierarchical when the sheet-to-sheet connectivity is only between Sheet Entries on the parent sheet and matching Ports on the child sheet - this connective behavior is defined by setting the Net Identifier Scope to Automatic, Hierarchical or Strict Hierarchical.

Multi-channel Design

Main article: Multi-sheet and Multi-channel Design

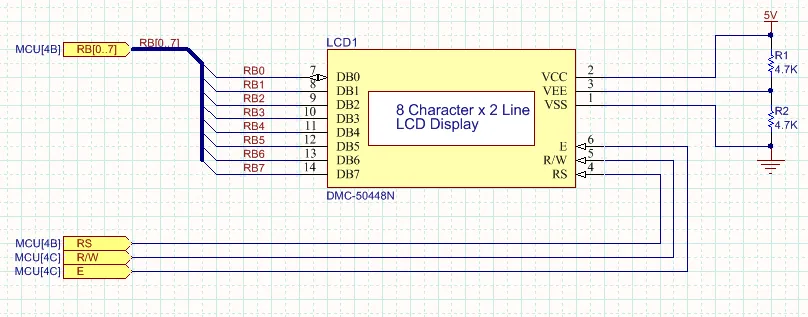

It is not unusual for an electronic design to include repeated sections of circuitry. It might be a stereo amplifier, or it might be a 64 channel mixing desk. This type of design is fully supported in Altium Designer, by a feature-set known as multi-channel design. In a multi-channel design you capture the repeated circuit once, then instruct the software to repeat it: by either placing multiple Sheet Symbols that all reference the same child schematic; or by configuring a single Sheet Symbol to repeat the referenced child schematic the required number of times. When the design is compiled it is expanded out in memory, with all components and connectivity repeated the required number of times, in accordance with the user-defined naming scheme.

On the left there are 4 Sheet Symbols, all referencing the same child sheet (PortIO.SchDoc). On the right the InputChannel.SchDoc is repeated 8 times by the Repeat keyword.

The logical design that you capture is never actually flattened, it always remains as a multi-channel schematic. When you transfer it to PCB layout the physical components and nets are stepped out the required number of times, and you have full access to the cross-probing and cross-selecting tools available for Working Between the Schematic and the Board. There is also a tool in the PCB editor to replicate the placement and routing of one channel across all other channels, with the ability to easily move and re-orient an entire channel. Refer to the multi-channel design article to learn more about multi-channel design.

A multi-channel design must be hierarchical because the software uses this structural model to instantiate the channels in memory when the design is compiled.

For a multi-channel design, set the Net Identifier Scope to Automatic, Hierarchical or Strict Hierarchical.

The duplication of components and nets is resolved by the software, using the naming scheme selected in the Multi-channel tab of the Options for Project dialog.

Setting the Net Identifier Scope

Dialog page: Options for Project

When you compile your project, the software uses the current setting of the Net Identifier Scope to work out how to establish connectivity between the schematic sheets. The Net Identifier Scope is configured in the Options tab of the Options for Project dialog (Project » Project Options).

Select the Net Identifier Scope mode to suit the structure of your design.

The behavior of the Global, Flat and Hierarchical options are shown in the images below.

Simple examples of how the connectivity is created for each of the 3 main modes: Global is shown on the left, then Flat, then Hierarchical.

As well as the 3 options mentioned above (Global, Flat, Hierarchical), there is also an Automatic option. Generally it is better to leave the Scope set to Automatic, Altium Designer will select the most appropriate of the 3 options based on the structure of the sheets and the presence/lack of Ports and Sheet Entries.

When set to Automatic, the software automatically selects which of the 3 main net identifier modes to use, based on the following criteria:

- If there are sheet entries on the top sheet, then Hierarchical is used.

- If there are no sheet entries, but there are ports present, then Flat is used.

- If there are no sheet entries and no ports, then Global is used.

The Strict Hierarchical mode localizes all power ports to each sheet, in this mode you must wire all the power (and ground) nets onto each child sheet using Ports and Sheet Entries. You can also do this for selective sheet(s) by not using the Strict Hierarchical mode, but still placing Sheet Entry(s) + Port(s) for the power net(s) you wish to localize.

How Nets are Named

Copy Link

Copied

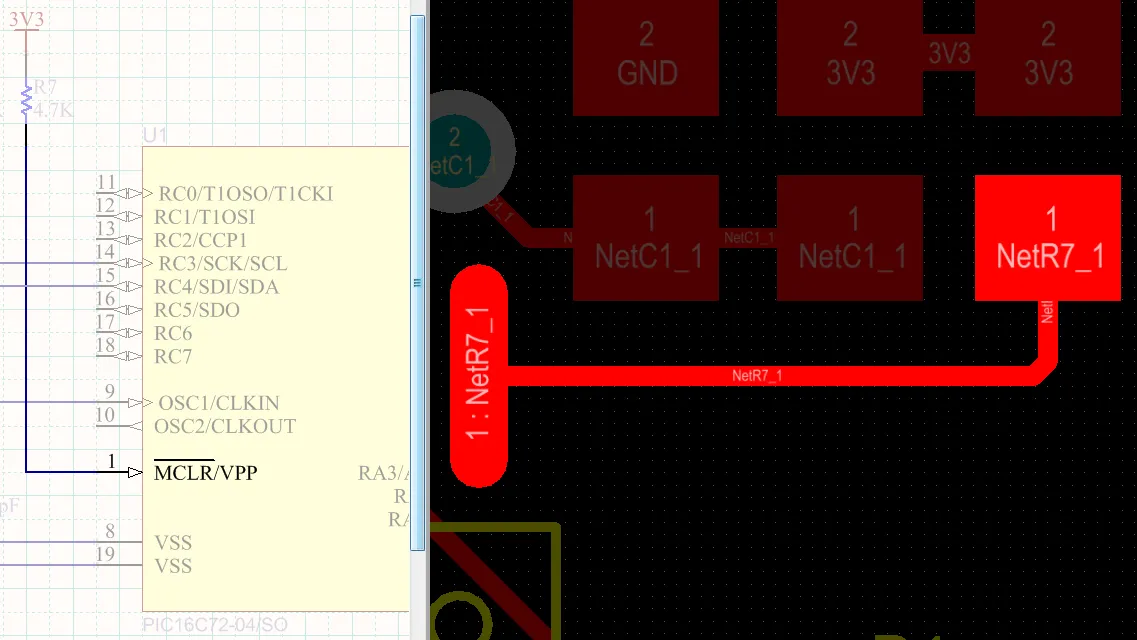

Each time you place a wire between component pins, you are creating connectivity. Every net in the design is given a name, if you have not placed a net identifier that can be used to name the net, then the software names that net based on one of the pins in the net, for example NetR7_1, as shown in the image below. If the component designator is changed at some stage, then when the design is recompiled that system generated net name is also changed and these changes must be passed between the schematic and PCB to keep everything in sync.

Nets without a net identifier are assigned a system-generated name, based on one of the pins in the net.

Net Labels always name the net they are attached to.

For other net identifiers, they name the net if the appropriate option is enabled in the Netlist Options section of the Options tab of the Options for Project dialog.

Different types of net identifiers do not automatically connect with each other. For example, a Port called Reset will not connect to a Net Label called Reset, even if the Allow Ports to Name Nets option in the Options for Project dialog is enabled. They must be connected by a wire.

Multiple Net Identifiers on a Net

You cannot have multiple Net Labels with different names on the same net within a schematic sheet, this situation will be detected and flagged as an error when the project is compiled. However, it is legitimate to have multiple net identifiers on a net on different sheets that the net appears on.

This ability allows the designer to:

- Change the name of a net at different levels in the hierarchy to better reflect its function on that sheet.

- Reuse a child schematic sheet without needing to rename nets on it.

The default setting is to assume that multiple net identifiers are not allowed, if they are detected during compilation then a warning will be given. If you require them for your design, then you will need to either:

- change the setting of the Nets with Multiple Names error check in the Error Reporting tab of the Options for Project dialog; or,

- suppress specific warnings by placing a Specific No ERC Marker on each warning. Note that Specific No ERC Markers can be placed by right-clicking on a warning listed in the Messages panel, and their shape and color can be changed if required.

Options for Controlling the Naming of the Nets

Dialog page: Options for Project

Ultimately, each net can only have one name on the PCB (one PCB net cannot have two names), and each net name should only be used once on the PCB (you should not have two different PCB nets with the same name). The software automatically resolves nets with multiple names to have just a single name when the project is compiled, but it may not be the name you expect. There are a number of options available to control how the name is chosen, in the Netlist Options section of the Options tab of the Options for Project dialog. Refer to the Options for Project dialog page for more details on each of the options.

A good approach to setting these options is to enable the Allow Ports to Name Nets and the Higher Level Names Take Priority options. Combine these with sensible usage of Net Labels on significant nets on each sheet, to ensure that all of the important nets, including those that traverse sheets, get named, and that the names assigned on the higher-level schematics are used down on the lower-level schematics.

When there are multiple net naming options enabled, the precedence for naming nets is as follows:

- If the Power Port Names Take Priority option is off, the order is: Net Labels, Power Ports, Ports, Pins.

- If the Power Port Names Take Priority option is on, the order is: Power Ports, Net Labels, Ports, Pins.

Two Separate Nets that have the Same Name

Copy Link

Copied

Another net naming issue that can arise is when the same net name has been used on different schematic sheets, to label different nets. This will be detected during compilation by the Duplicate Nets error check. You cannot transfer a design to the PCB with this condition present, those 2 separate nets will be merged into a single PCB net during design transfer.

This situation can be resolved by enabling the Append Sheet Numbers to Local Net option in the Options tab of the Options for Project dialog. With this option enabled, all local nets have the value of the SheetNumber parameter appended to their name, as shown in the images below.

Since the net label Input has been used on multiple sheets, the Append Sheet Numbers to Local Net option has been enabled to prevent a Duplicate Nets error.

The effect of this can be seen by clicking on the complied sheet tab (right image), note that _2 has been appended to the net name.

The Append Sheet Numbers to Local Net option will only work if each schematic sheet has been assigned a unique SheetNumber. The SheetNumber parameter is assigned in the Parameters tab of the Document Options dialog for each schematic sheet. As an alternative to manually assigning a unique number to each schematic sheet, run the Number Schematic Sheets command, which opens the Sheet Numbering for Project dialog. This can be used to assign unique SheetNumbers (a simple numeric value for each sheet) and DocumentNumbers (typically used for a company-assigned document numbering), to all sheets.

Intentionally Connecting Two Nets

Copy Link

Copied

There are situations when you need to intentionally connect two different nets. This is not a simple naming issue, it is when two nets need to be shorted as a design requirement. An example could be when you need to connect an Analog ground and a Digital ground in a controlled way.

This is achieved by connecting the 2 nets through a Net Tie component. A Net Tie component is nothing more than a controlled short circuit. On the schematic, the Net Tie component has two (or more) pins, with each pin connected to the nets to be shorted. Note that the pins are not wired to each other on the schematic, but they are connected together within the PCB footprint.

A Net Tie component being used to route a single clock to two FPGA clock pins, on the PCB the pads (shown as hatched) in the Net Tie footprint are shorted with a track (shown as an outline).

On the PCB side, the footprint has the same number of pads as the schematic symbol has pins, with copper between them. The software automatically ignores short circuits created within a Net Tie PCB component, so a DRC error is not created.

In this situation, each net retains its own name throughout the schematic and on the PCB.

When creating the Net Tie symbol and footprint, set the Component Type to either Net Tie, or Net Tie in BOM.

Power Nets

Copy Link

Copied

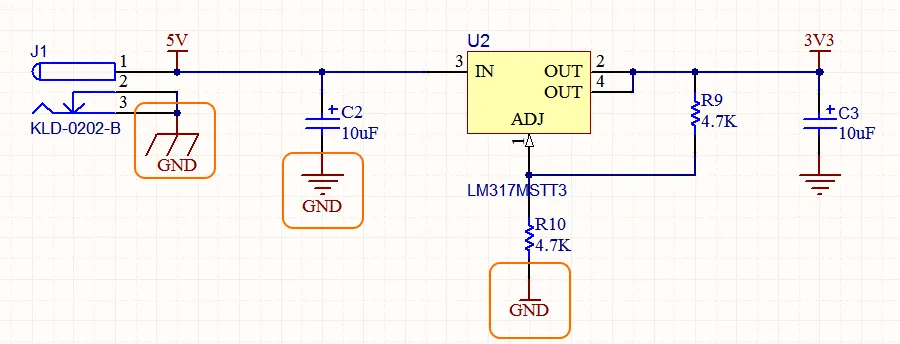

The default behavior of the settings is to assume that power nets are global, that is, you want them to be available on every schematic sheet. To access a power net, you simply place a Power Port with the required net name, then wire the components to that power port.

It's the net name that determines what net a power port is connected to, not the Style of the symbol - the 3 highlighted power ports all connect to the GND power net.

Localizing a Power Net - Globally

As mentioned previously, power nets can be be localized to each schematic sheet in an hierarchical design, by selecting the Strict Hierarchical option for the Net Identifier Scope. This approach localizes all power nets on every sheet, so they must be manually wired together, using the same approach as signal nets. If they are not wired together, when the design is compiled there will be a Duplicate Net Name error for each power net present on each schematic sheet. You will also need to adjust the Connection Matrix settings to allow Ports to be connected to Power Ports.

If the Net Identifier Scope is set to Strict Hierarchy then every power net must be wired to every sheet that they are used on.

Localizing a Power Net - Individually

A specific power net can also be localized on a specific sheet by wiring the Power Port to a Port on that schematic sheet.

Here the 3V3 power net has been localized for just this sheet, so must also be manually wired on the parent sheet. The GND and 5V nets remain as global power nets.

Power Nets and Hidden Power Pins

Another feature that helps manage power nets and component power pins is the ability to automatically connect hidden component pins to the specified net. This feature is designed for use with multi-part components, where you do not want to create an extra part for the power pins, or display them in one of the parts.

The image below shows a 54HC244, the instance on the left is how it normally presents, the instance on the right is the same part, except it has the hidden pins displayed. The pins are hidden and the net name defined as a property of the pin, during component creation in the schematic library editor. Typically the pins are assigned to Part 0 (zero), as the pins in Part 0 are automatically added to all parts.

This HC244 has hidden power pins, which have been displayed on the instance on the right. Edit the pin to make it hidden and assign the net it is to connect to.

Hidden pins can be displayed on the schematic sheet by enabling the Show All Pins on Sheet (Even if Hidden) option in the properties dialog. During component creation, use the View » Show Hidden Pins option to display them in the schematic library editor.

If hidden pins are displayed on the schematic sheet they will no longer automatically connect to the specified power net, so must be wired manually.

Enabling the display of hidden pins on the schematic.

If you are using components with hidden power pins, it is important to be aware of the net names assigned to those hidden pins. If the net names are incorrect, you must either edit the pins and change the names, or display the hidden pins and wire them to the correct power nets.

Bundling Multiple Nets

Copy Link

Copied

A common challenge in a large design is keeping the nets manageable. Not only from the perspective of the designer creating the connectivity, but also from the perspective of the reader that has to interpret and understand the schematic. This is particularly important when connecting between sheets, as this is when both the designer and the reader can most easily get confused.

This can be helped by bundling nets into Buses, or Signal Harnesses.

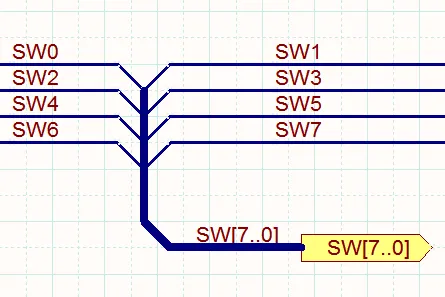

Working with Buses

Buses are used to bundle a series of sequential nets, for example an address bus or a data bus. Their core requirement is that each net in the bus is named with a common base name, followed by a numeric identifier, as shown in the images below. For example, the nets Control1, Control2 and Control3 can be bundled into the bus Control[1..3]. Buses cannot be used to bundle an unrelated set of nets, such as the nets Enable, Read and Status, Signal Harnesses are used to do this.

To create a valid bus, it must include all of these elements (as shown in the images below):

- A Net Label on each of the individual nets

- A Net Label on the Bus line

- A Port named the same as the Bus, if it is leaving this sheet

All of the elements shown in the image above must be included to create a valid Bus. Bus Entries only need to be used if you want to rip different bus elements from both sides of the Bus.

Buses are not transferred to the PCB, instead a Net Class can be created for each schematic Bus, or if required, for each Bus section. A bus section is created by specifying a bus which is actually a section of a larger bus, for example D[15..8], from the bus D[15..0]. If this option is enabled then the PCB will include a Net Class for the entire bus, as well as each section that has been defined. Enable the required options in the Class Generation tab of the Options for Project dialog.

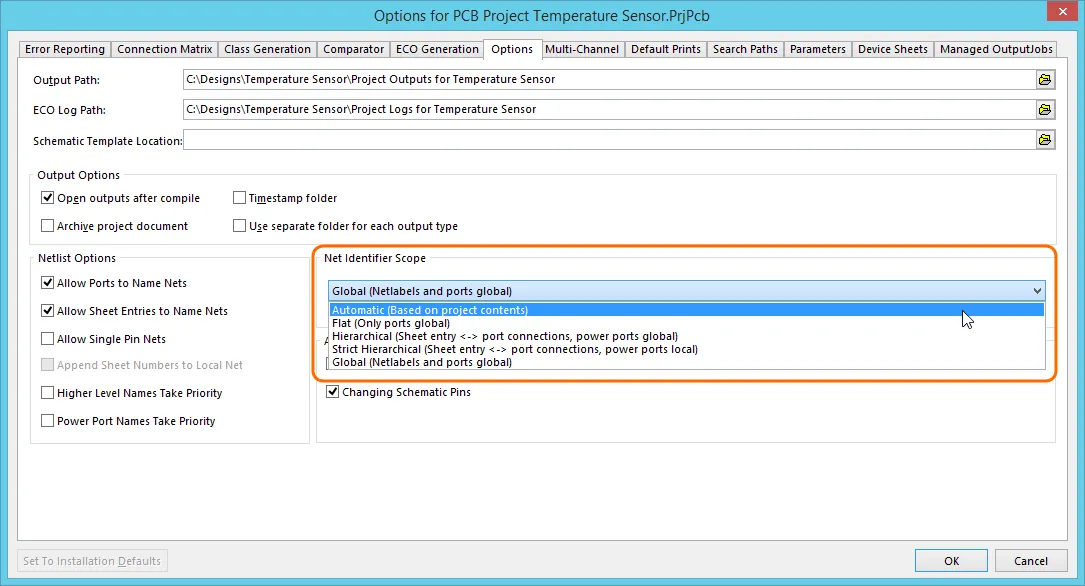

Working with Signal Harnesses

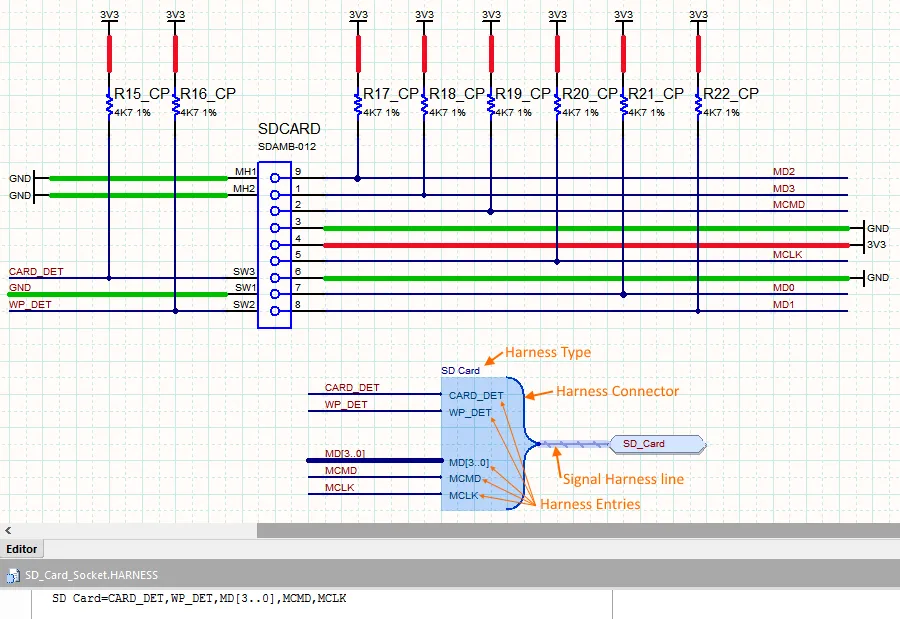

Signal harnesses are highly flexible as they can be used to bundle any number of nets, buses and lower-level harnesses. As their name implies, they are analogous to a wiring harness, where any arrangement of wires can be bundled and routed through an electronic or electrical product. They are more complex to create and manage, but the reward is that they can greatly simplify the presentation of a schematic and enhance its readability.

Signal harnesses are used to bundle any combination of nets, buses and lower-level signal harnesses.

The elements that make up a complete signal harness include:

- Harness Connector - Think of a Harness Connector as a funnel, it gathers all of the signals that connect into this harness through the included Harness Entries. A key property of the Harness Connector is the Harness Type, this identifies the harness and is used to bind together the various elements that make up the signal harness, including the connected Ports / Sheet Entries.

- Harness Entries - Each signal (net, bus or signal harness) that you want to be part of this signal harness, enters the Harness Connector through a Harness Entry. The Harness Entry include a Harness Type property, this is only used when you are nesting signal harnesses - signifying that this Harness Entry has a lower-level signal harness connected to it.

- Signal Harness line - This is the bus-like line that is placed to carry the signal harness across the sheet.

- Harness Type - A Harness Type is a set of Harness Entries. Each detected Harness Type is defined in a Harness Definition File, as described below. The Harness Type and its associated Harness Entries are essentially names of the containers that carries the nets, not the names of the nets themselves. To check the Harness Type value, hover the cursor over the object, for example the Port, Sheet Entry, or Harness Connector (the project must be compiled).

- Harness Definition File - The software manages signal harnesses by recording the Harness Entries that are in each signal harness (Harness Type), in an ASCII Harness Definition File. The image below shows the syntax of a Harness Definition File, there is a line in the file for each Harness Type, which details the Harness Entries within that harness. A Harness Definition File is automatically created (and managed) for each schematic sheet that has Harnesse Connectors on it, you can find them in the

\Settings folder in the project tree, as shown in the image below. The Harness Definition file can be opened by clicking the  button, located down the bottom right of the schematic. If your design has had changes that impact the signal harnesses, the Harness Definition files should update automatically whenever the project is compiled. If not, they can be regenerated by right-clicking on the Project file in the Projects panel and running the Regenerate Harness Definitions command.

button, located down the bottom right of the schematic. If your design has had changes that impact the signal harnesses, the Harness Definition files should update automatically whenever the project is compiled. If not, they can be regenerated by right-clicking on the Project file in the Projects panel and running the Regenerate Harness Definitions command.

- Port + Sheet Entry - Like a Net or Bus, a Signal Harness can leave a sheet via a Port, and then connect to the higher level sheet through a matching Sheet Entry. Note that the software automatically changes the color of the Ports and Sheet Entries to show they are carrying a Signal Harness if the Sheet Entries and Ports use Harness Color option is enabled in the Schematic - Graphical Editing page of the Preferences dialog. Note also that the Port and Sheet Entry objects include a Harness Type property, this value is set automatically as you touch the Port to the Signal Harness line when you are placing the Port. For the Port on the schematic sheet where the Harness is defined (the Harness Connector is present) the Harness Type is automatically defined and is not editable. For a Port or Sheet Entry placed on a higher-level schematic sheet it will be blank and editable, typically there is no need to manually set this. The assigned Harness Type can be checked at any time by hovering the cursor over the Port/Sheet Entry.

Harnesses definitions are stored in Harness Definition files, in the image above there are two signal harnesses defined: 1WB_Write_Read and JTAG.

If you suspect that there are connectivity issues caused by errors in the Harness definitions, run the Tools » Harness Definition Problem Finder command from the schematic editor menus. The Harness Definition Resolver dialog will open, use this dialog to examine any conflicts that are present in the harness definitions. Click the Details button in the dialog to get more information on the selected conflict.

You can also regenerate the Harness Definition files by right-clicking on the Project file in the Projects panel and running the Regenerate Harness Definitions command.

Nested Signal Harnesses

Copy Link

Copied

As mentioned, as well as a net or a bus, you can also wire a signal harness into a signal harness, creating what is referred to as nested signal harnesses. This situation is identified at the Harness Entry, which has its Harness Type property set to the value of the incoming signal harness.

As well as nets and buses, a signal harness can carry other signal harnesses.

Compiling the Design

Copy Link

Copied

Related article: Compiling and Verifying the Design

Throughout this article there are many references to compiling the design. So what is compiling and why does the design need to be compiled?

The schematic editor is essentially an intelligent drafting tool, not a wiring tool. When you connect two pins with a wire you are drafting your design intentions, not creating an actual net. That net is not created until you compile the project. There are many advantages to this approach, with the biggest being that the compiled model of the design sits outside of the individual editors. This compiled model of the project is referred to as the Unified Data Model (UDM). The UDM includes detailed descriptions of every component in the design, and how they are connected to each other.

When you compile the project:

- The connectivity within each sheet is created

- The sheet-to-sheet connectivity is then created, based on the chosen Net Identifier Scope

- The Unified Data Model is created, displaying the component and connective details in the Navigator panel

- The enabled error checks are run.

The Unified Data Model

A fundamental element of the software is the Unified Data Model (UDM). When the project is compiled, a single, cohesive model is created, which sits central to the design process. Data within the model can then be accessed and manipulated using the various editors and services within the software. Rather than using a separate data store for each of the various design domains, the UDM is structured to accommodate all information from all aspects of the design, including the components and their connectivity.

The Unified Data Model makes all of the design data available to all of the editors, and helps deliver sophisticated features like multi-channel design.

So how do you interact with the unified data model, for example to trace a net through the design? You do that through the Navigator panel.

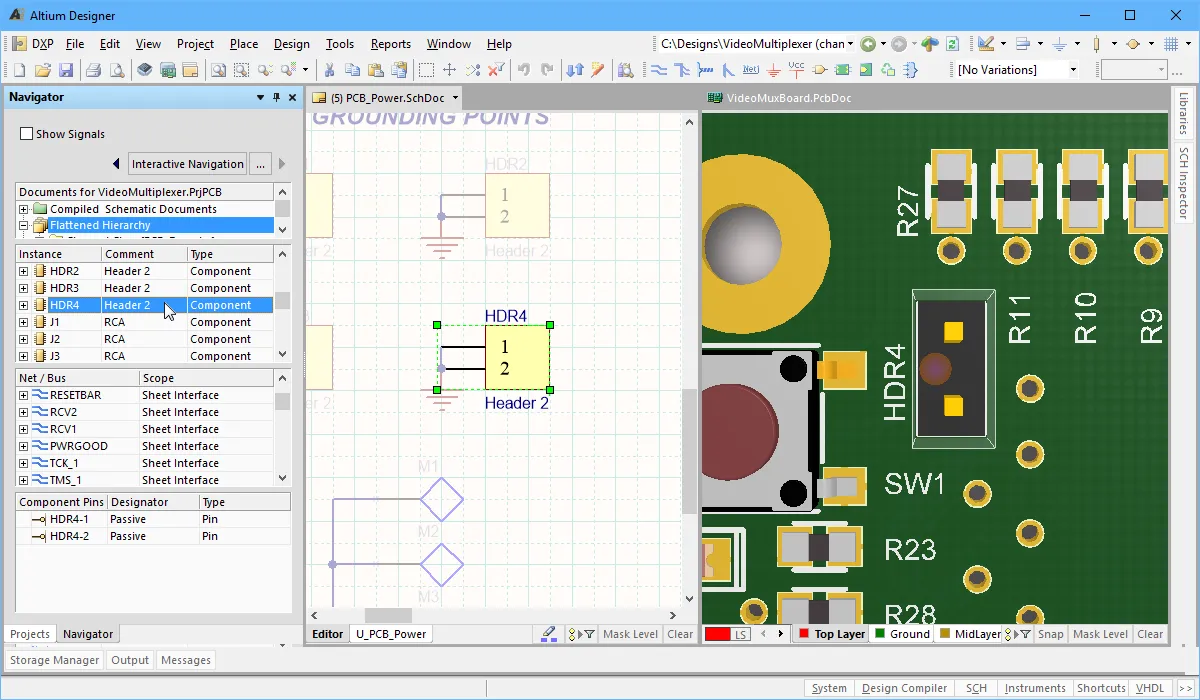

Examining the Connectivity

Reference article: Navigator panel

If the design is large and spread over many sheets, it can become difficult to follow and verify the connectivity in the design. To help with this, the Navigator panel is used. The panel gives a view of the entire, compiled design, so will be blank until the project is compiled (Project » Compile PCB Project).

The basic approach to using the panel is to:

- Set the browsing behavior by clicking the

button at the top of the panel to open the Preferences dialog and enable your preferred Highlight Methods. Alternatively, right-click on the object of interest in the panel, and use the menu options to configure the navigation behavior.

button at the top of the panel to open the Preferences dialog and enable your preferred Highlight Methods. Alternatively, right-click on the object of interest in the panel, and use the menu options to configure the navigation behavior.

- Set the scope of your browsing in the first section, to browse the entire design select

Flattened Hierarchy.

- Click on a component in Instance section of the list to jump to that component.

- Click on a net or bus in the Net /Bus section to jump to that net or bus.

Click on a component or net in the Navigator panel to locate that component or net, and trace the connectivity through the design. Right-click to access display options.

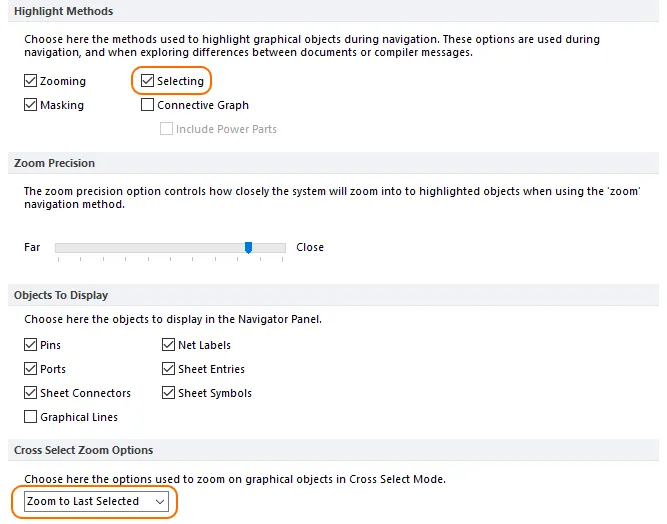

Navigating Components on the Board

As you click to locate a component on the schematic, you can also locate that same component on the PCB. To do this, you must enable the Selecting option in the Highlight Methods, and also the Zoom to Last Selected option in the Cross Select Zoom Options on the System - Navigation page of the Preferences dialog.

If these options are enabled, as you click on a component in the Navigator, it will be displayed on the schematic and the PCB.

Now as you click on a component in the Navigator, it will display that component on both the schematic and the PCB, as shown in the image below.

Navigate to a component on the schematic and the PCB at the same time.

Connectivity in the Board Design Space

Copy Link

Copied

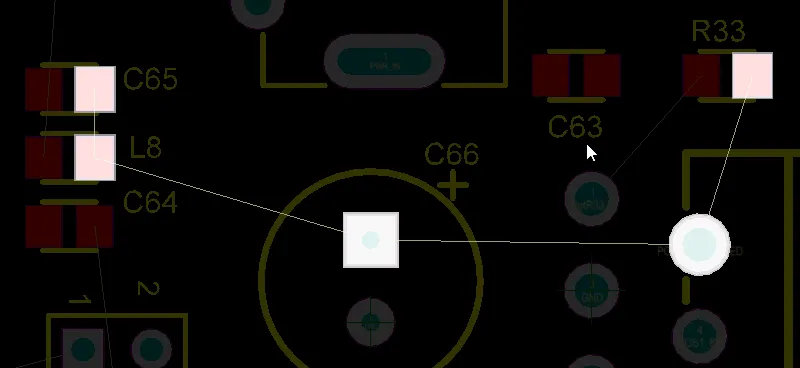

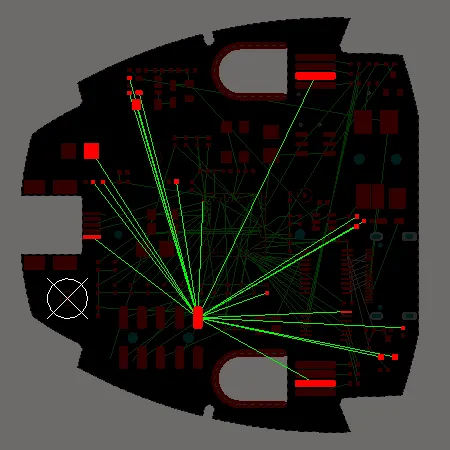

In the PCB editor, the connectivity between the nodes in a net is represented by a series of point to point connection lines, which are collectively referred to as the ratsnest. The connection lines are displayed on a special System layer, called Default Color for New Nets, which can be displayed/hidden in the Board Layers and Colors tab of the View Configuration dialog.

Within an individual net, the connection lines join all of the nodes in that net. The pattern, or order they connect, is called the Net Topology, which is discussed below.

The nodes in the net are connected by connection lines.

Connection lines are displayed as thin, solid lines. The connection lines are an excellent aid during component placement, to help locate and orient components that are connected to each other. To help reduce visual clutter, as you move a component all connection lines are hidden, except the connection lines connected to that component.

Use the connection lines to help locate and orient the components.

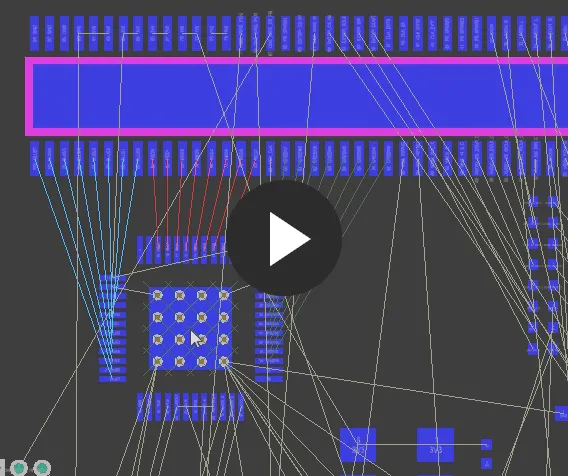

As well as being a helpful guide during component placement, the connection lines are also a valuable guide during interactive routing and autorouting. Because the connectivity is monitored and updated as you work, you can route to any point on a net to complete a connection, you do not have to route up to the pad that the connection line ends on.

Net Topology

The pattern, or order that the nodes in the net are connected to each other is called the net topology. Net topology is controlled by the applicable Routing Topology design rule, which defaults to a topology of Shortest. Shortest means the nodes in the net are connected to each other in a pattern that gives the shortest overall connection length for that net. This overall length is monitored as you move a component, and the pattern of the connection lines will change dynamically to keep the overall length shortest. This can be observed in the animation shown above, where the lines connecting downward from the bottom of the moving component jump as the component is being moved - this happens each time one of the connected pads moves closer to another pad in their net.

Applying a Pre-defined Topology

Reference article: Routing Topology design rule

Additional Routing Topology design rules can be created to configure a net (or net class ) to use a different topology. To demonstrate this, in the images shown below the default topology rule is shown on the left, and that same net with a new routing topology of Starburst having been applied is shown on the right. In a Starbust topology the connections radiate from the pad with an Electrical Type of Source (the default type for all pads is Load).

For the default topology, the connection lines are placed to give the shortest overall connection length. In the Starburst topology the connection lines all radiate from a Source pad.

Applying a Custom Topology

Reference article: From-To Editor

Within an individual net, the connection between two nodes is referred to as a From-To. To control the path of the connection lines down at the individual pin-to-pin level, you can manually define From-Tos within a net, effectively creating a custom net topology.

From-Tos are defined by setting the PCB panel to From-To Editor mode. The process of defining a From-To is select 2 nodes in the net, and click the Add From To button. To clearly identify From-Tos in the workspace, they are shown as a dashed line instead of a solid line.

A From_To has been defined between 2 pads, note how the From-To line is displayed as dashed rather than solid.

For a detailed description of defining From-Tos, refer to the From-To Editor article.

Managing the Display of the Connection Lines

Reference article: View Configuration dialog

The connection lines are a valuable aid to help with placing and orienting the components, and to guide you during routing. However, their presence can also create a lot of visual cluttter. To help with this, the PCB editor includes the following features to help the designer manage the display of connection lines:

- Hide/show all of the connection lines by toggling the display state of the Default Color for New Nets System layer, in the Board Layers and Colors tab of the View Configuration dialog.

- Selectively hide/show connection lines, using the commands in View » Connections sub-menu (press the N shortcut to pop this menu up). All of the available commands have accelerator keys, making it an efficient method of performing such tasks as hiding all connection lines (N, H, A), then displaying the connection lines for a specific net (N, S, N).

- When in single layer mode (Shift+S), display only the connection lines that connect to component pads that are on that layer. Control this using the Show All Connections in Single Layer Mode option in the View Options tab of the View Configuration dialog.

- For a connection line whose start and end pads are on different layers, display each connection line using a combination of the start and end layer colors. Control this using the Use Layer Colors For Connection Drawing option in the View Options tab of the View Configuration dialog.

- Assign color to the connection lines in a net, or a set of nets, to help easily identify them. This is discussed below.

- Mask or Dim all nets, except the ones you are interested in. Set the PCB panel to Nets mode, then choose either Dim (fade other objects but allow editing of faded objects) or Mask (fade other objects and only allow editing of un-faded objects) in the drop down, then click on a net (or Net Class). All objects will be faded, except those belonging to the chosen net(s), making it easy to see and work with the objects in that net.

- While moving a component, you can temporarily disable the re-optimization and display of connection lines by pressing the N shortcut.

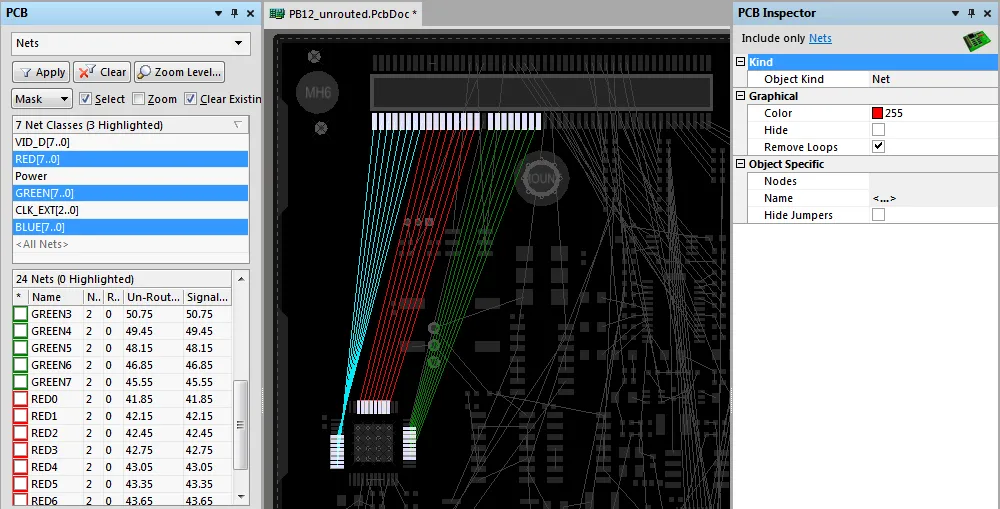

Assigning Color to the Connection Lines

Main articles: Connection object

The color of the Default Color for New Nets System layer is the color assigned to the connection lines in each net, when the net is first created in the PCB editor during transfer from the schematic editor. To change the color of the connection lines for a net that already exists in the PCB editor, you can edit it for a specific net by double-clicking the net name in the PCB panel. For multiple nets, select them in the PCB panel and use the PCB Inspector panel to edit the color of them all (set the panel to Include only Nets). For the example shown in the image below, the Net Class was selected in the panel, then the color changed in the PCB Inspector panel for all nets in that class.

Give meaning to role of the different nets by changing the color of their connection lines. In this image all other nets are masked, hover to see the difference when there is no mask applied.

Component Positioning Guide

As you move a component around in the workspace, a thick green or red line will be displayed, traveling from a point within the component, to a location on the board. This line is called the Optimal Placement Vector, its function is to give an indication of whether the new location is better (green) or worse (red) than the previous location.

The vector has two distinct properties: its proposed target location; and its color.

To determine the locations for each end of the vector, the feature uses the centroid of the polygonal shape defined by the locations of the end points of the connection lines. There are 2 centroids of interest, one defined by the ends of the connection lines terminating on the component you are moving (the component centroid), the second defined by the other ends of that set of connection lines (the target location centroid).

The Optimal Placement Vector is drawn between these 2 centroids, with the component end highlighted by a dot. Because it is a relative indicator, when you first click to start moving a component the vector is always drawn in green. The 2 centroids are continuously re-calculated as you move the component, because the connection lines can move from one pad to another as they are automatically re-optimized to maintain the applicable net topology for the moving component. Because of this net re-optimization, the target end of the OPV can jump around as the component is moved. If the centroids move apart and the OPV becomes longer, it may change to red. If the centroids move closer together and the OPV becomes shorter, it may change to green.

The length of the vector is not the only condition used to set the color, the color of the OPV is also affected by the overall length of the connection lines attached to the moving component. If moving the component results in the overall length of the connection lines increasing, then the OPV becomes red. Alternatively, if moving the component results in the overall length of the connection lines decreasing, then it becomes green.

Although the vector length is increasing, it remains green because the overall length of the connection lines is getting shorter.

When the component is rotated, the connection lengths increase so the OPV becomes red.

Remember that the OPV is a relative guide, each time you place the component, that new location becomes the starting point for calculations the next time you move that component.