Parent page: PCB Placement & Editing Techniques

Pad and Via Summary

Pads are used to provide both mechanical mounting and electrical connections to the component pins

Pads are used to provide both mechanical mounting and electrical connections to the component pins

A pad is a primitive design object. Pads are used for fixing the component to the board and for creating the interconnection points from the component pins to the routing on the board. Pads can exist on a single layer, for example, as a Surface Mount Device pad, or they can be a three-dimensional through-hole pad, having a barrel-shaped body in the Z-plane (vertical) with a flat area on each (horizontal) copper layer. The barrel-shaped body of the pad is formed when the board is drilled and through-plated during fabrication. In the X and Y planes, pads can have a circular, rectangular, octagonal, or rounded rectangular shape. Pads can be used individually as free pads in a design, or more typically, they are used in the PCB Library editor, where they are incorporated with other primitives into component footprints.

A via that spans and connects from the top layer (red) to the bottom layer (blue), and also connects to one internal power plane (green).

A via is a primitive design object. Vias are used to form a vertical electrical connection between two or more electrical layers of a PCB. Vias are three-dimensional objects and have a barrel-shaped body in the Z-plane (vertical) with a flat ring on each (horizontal) copper layer. The barrel-shaped body of the via is formed when the board is drilled and through-plated during fabrication. In the X and Y planes, vias are circular, like round pads. The key difference between a via and a pad is that as well as being able to span all layers of the board (top to bottom), a via can also span from a surface layer to an internal layer or between two internal layers.

Vias can be one of the following types:

- Thru-Hole – this type of via passes from the Top layer to the Bottom layer and allows connections to all internal signal layers.

- Blind – this type of via connects from the surface of the board to an internal signal layer.

- Buried – this type of via connects from one internal signal layer to another internal signal layer.

Via types that can be used in the design are defined in the Layer Stack Manager. To learn more, refer to the Blind, Buried & Micro Via Definition page.

Direct Placement of Pads and Vias

Pads and vias are available for placement in both the PCB and the PCB Footprint editors. Vias are typically placed automatically during the interactive or automatic routing processes but can be placed manually if required. Manually placed vias are referred to as 'free' vias. After launching the pad or via placement command, the cursor will change to a crosshair, and you will enter placement mode.

- Position the cursor then click or press Enter to place a pad/via.

- Continue placing further pads/vias or right-click or press Esc to exit placement mode.

A pad/via will adopt a net name if it is placed over an object that is already connected to a net.

During placement, press the Alt key to constrain the direction of movement to the horizontal or vertical axis depending on the initial direction of movement.

Free pads on the Multi-layer layer can be changed into vias. A free pad is one that is not part of a parent component object. Changing free pads to vias can be useful when manually converting imported Gerber files back into PCB format. Select all free pads that you wish to convert in the design space and choose the Tools » Convert » Convert Selected Free Pads to Vias command from the main menus. The free pads will be converted to vias with the same hole size. The highest value found across all available XY size pairs for the pad (corresponding to the pad size on different layers) will be used for the via's diameter.

Also, vias can be changed into free pads. Changing vias to free pads can be useful when importing PADS-PCB and PADS 2000 files, where vias are used to connect to power and ground layers. This allows proper connection to internal power planes, using editable pads. Select all vias that you wish to convert in the design space and choose the Tools » Convert » Convert Selected Vias to Free Pads command from the main menus. The vias will be converted to free pads of the same style (Simple, Top-Middle-Bottom, or Full Stack) and with the same hole size. The via's diameter size is used for the pad's XY sizing on the applicable layers. The shape of the pad will be set to Round.

Graphical Editing

Pads and vias cannot have their properties modified graphically other than their location.

- To move a free pad and also move the connected tracks, click, hold and move the pad. The connected routing will remain attached to the pad as it is moved.

- To move a free pad without moving the connected tracks in the PCB or PCB Library Editor, select the Edit » Move » Move command, then click, hold, and move the pad.

If you click and drag a selection rectangle around component pads, they will not select as they are actually child objects of the component. To sub-select just the pads, hold Ctrl as you click and drag the selection window.

If a via is being moved with the routing to create more routing or component space, it can be more efficient to re-route than move routing. The software includes a feature called Loop Removal. With this feature enabled, you route along a new path (starting and ending somewhere along the original routing), as soon as you right-click to exit the interactive routing mode the old routing (loop) is removed, including any redundant vias.

Non-Graphical Editing via the Properties Panel

This method of editing uses the associated mode of the Properties panel to modify the properties of a Pad/Via object.

Pad Properties

The Pad mode of the Properties panel

Properties

- Component – this field is shown in the PCB editor only when the selected Pad is a constituent part of a PCB Component and displays the designator of the parent PCB component. Select the clickable Component link to open the Component mode of the Properties panel for the parent component.

- Designator – this field displays the current pad designator. If the pad is part of a component, the designator is usually set to the corresponding component pin number. Free pads can include a designator or the field can be left empty. If the designator begins or ends with a number, the number will auto-increment when placing a series of pads sequentially. Edit the value in this field to change the pad designator.

- Layer – this field displays the layer to which the pad is currently assigned. Pads can be assigned to any available layer. To change the assigned layer, click the field and select a layer from the drop-down list.

- Net – use to choose a net for the pad. All nets for the active board design will be listed in the drop-down list. Select No Net to specify that the pad is not connected to any net. The Net property of a primitive is used by the Design Rule Checker to determine if a PCB object is legally placed. Alternatively, you can click on the Assign Net icon (

) to choose an object in the design space – the net of that object will be assigned to the selected pad(s).

) to choose an object in the design space – the net of that object will be assigned to the selected pad(s).

- Electrical Type – this field displays the current electrical status of the pad. This status is only relevant for component pads and sets the transmission line characteristics for these pads. Pads can be designated as a Load, Source or Terminator. The Source and Terminator settings are used when a net requires one of the Daisy chain routing topologies. Click the field to change the electrical type from the drop-down list.

- Propagation Delay – this field lists the propagation delay, which is the amount of time it takes for the head of the signal to travel from the sender to the receiver.

- Pin Package Length – the Pin Package Length is automatically included in the Signal Length calculations that are displayed in the PCB panel. Set the PCB panel to Nets mode to examine (or edit) the value of the Pin/Pkg Length for the pins in the chosen net.

- Jumper – this field provides a jumper connection identification number (range of 1 – 1000) to the pad when you are using a jumper connection on the PCB. A jumper connection uses a wire to physically connect pads on a PCB, and does not use tracks or electrical objects on the board. The Jumper value tells the software which pads to treat as 'connected'. A jumper connection can only be created among the pads within a component footprint. The pads used must use the same Jumper value and must also share the same net. A jumper connection is shown as a curved connection line in the PCB Editor. Use the scroll arrows or directly enter the desired jumper connection identification number.

- Template – displays the current template for the pad. Use the drop-down to select another template. If there is an associated Library, that library will be displayed. Click the

button to unlink a template from an associated Pad/Via Template library.

button to unlink a template from an associated Pad/Via Template library.

- (X/Y)

- X (first field) – this field shows the current X position of the center of the pad relative to the current origin. Edit the value in the field to change the position of the pad relative to the current origin. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space), and are used if the unit is not specified.

- Y (second field) – this field shows the current Y position of the center of the pad relative to the current origin. Edit the value in the field to change the position of the pad relative to the current origin. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space), and are used if the unit is not specified.

The

icon to the right of this region must be displayed as

(unlocked) in order to access the

X and

Y fields. Toggle the lock/unlock icon to change its lock status. When locked, no edits can be made to the location

- Rotation – the pad's angle of rotation (in degrees), measured counterclockwise from zero (the 3 o'clock horizontal). this field to change the rotation of the pad. Minimum angular resolution is 0.001°.

Pad Stack Information

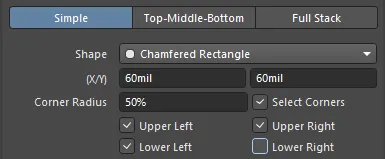

- Simple/Top-Middle-Bottom/Full Stack – choose the desired pad stack mode for a through-hole pad (i.e. when

Multi-Layer is selected as the pad's Layer). For other layers, the options of the Simple mode are applicable.

- Simple – select to choose a simple layered pad. You can define the pad shape attributes that are common for all layers of this pad.

- Shape – this field shows the current pad shape. Standard pad shapes (

Round, Rectangular, Octagonal, Rounded Rectangle, and Chamfered Rectangle) can be manipulated by changing the X and Y settings to produce asymmetrical pad shapes. Select Custom Shape to define a pad of a non-standard shape.

- (X/Y) – displays the current X (horizontal) and Y (vertical) size of the pad. The values set the size of the pad and can accept values of 1 to 10000mil. The X and Y size can be set independently to define asymmetric pad shapes. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified. This option is available only if

Round, Rectangular, Octagonal, Rounded Rectangle, or Chamfered Rectangle is selected as Shape.

- Corner Radius – this displays the corner radius of a pad. Pad radius is represented as a percentage of half of the shortest side of the pad. This option is accessible only if

Rounded Rectangle or Chamfered Rectangle is selected as Shape.

- Select Corners - enable this option to select the desired corners to round or chamfer (depending upon the Shape that you chose). The corner options will appear only when this option is enabled. This option is available only if

Rounded Rectangle or Chamfered Rectangle is selected as Shape.

- Outline Vertices – check the box to show a grid table of vertices for the custom shape pad's region from where the vertices of the region can be added, edited, and removed. This option is available only if

Custom Shape is selected as Shape.

- Edit Shape – click the button to interactively edit the custom shape pad's region in the design space. This button is available only if

Custom Shape is selected as Shape.

- Thermal Relief – check the box to enable thermal relief to reduce heat conductivity. Once checked, click

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

-

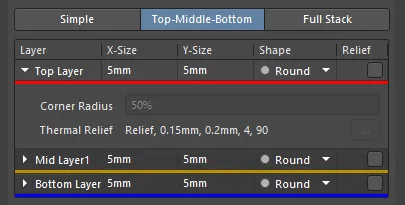

Top-Middle-Bottom – select to choose a Top-Middle-Bottom layered pad object. You can define X and Y sizes and shape attributes for top, middle and bottom layers for this pad object.

- Layer – lists the signal layers for which parameters can be configured. Click in a cell to access the Corner Radius and Thermal Relief properties for the selected layer.

- X-Size/Y-Size – displays the current X (horizontal) and Y (vertical) size of the pad. The values set the size of the pad and can accept values of 1 to 10000mil. The X and Y size can be set independently to define asymmetric pad shapes. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

- Shape – this field shows the current pad shape. Standard pad shapes (

Round, Rectangular, Octagonal, Rounded Rectangle, Octagonal Finger, and Rounded Finger) can be manipulated by changing the X and Y settings to produce asymmetrical pad shapes. Select Custom Shape to define a pad of a non-standard shape.

- Relief – check the box to configure the thermal relief, different from that defined in an applicable Polygon Connect Style design rule, using the Thermal Relief option.

- Corner Radius – this displays the corner radius of a pad. Pad radius is represented as a percentage of half of the shortest side of the pad. This option is available only if

Rounded Rectangle or Rounded Finger is selected as Shape.

- Outline Vertices – check the box to show a grid table of vertices for the custom shape pad's region from where the vertices of the region can be added, edited, and removed. This option is available only if

Custom Shape is selected as Shape.

- Edit Shape – click the button to interactively edit the custom shape pad's region in the design space. This button is available only if

Custom Shape is selected as Shape.

- Thermal Relief – displays the current parameters of the thermal relief for the selected layer. Once the Relief option for this layer is checked, click

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

-

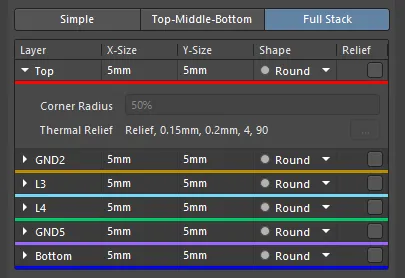

Full Stack – select to choose a Full Stack layered pad object. You can define X and Y sizes and shape attributes for all layers of this pad object.

- Layer – lists the signal layers for which parameters can be configured. Click in a cell to access the Corner Radius and Thermal Relief properties for the selected layer.

- X-Size/Y-Size – displays the current X (horizontal) and Y (vertical) size of the pad. The values set the size of the pad and can accept values of 1 to 10000mil. The X and Y size can be set independently to define asymmetric pad shapes. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

- Shape – this field shows the current pad shape. Standard pad shapes (

Round, Rectangular, Octagonal, Rounded Rectangle, Octagonal Finger, and Rounded Finger) can be manipulated by changing the X and Y settings to produce asymmetrical pad shapes. Select Custom Shape to define a pad of a non-standard shape.

- Relief – check the box to configure the thermal relief, different from that defined in an applicable Polygon Connect Style design rule, using the Thermal Relief option.

- Corner Radius – this displays the corner radius of a pad. Pad radius is represented as a percentage of half of the shortest side of the pad. This option is available only if

Rounded Rectangle or Rounded Finger is selected as Shape.

- Outline Vertices – check the box to show a grid table of vertices for the custom shape pad's region from where the vertices of the region can be added, edited, and removed. This option is available only if

Custom Shape is selected as Shape.

- Edit Shape – click the button to interactively edit the custom shape pad's region in the design space. This button is available only if

Custom Shape is selected as Shape.

- Thermal Relief – displays the current parameters of the thermal relief for the selected layer. Once the Relief option for this layer is checked, click

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

- Offset From Hole Center (X/Y) – enter a value to offset the pad landing area from the center of the pad hole.

- Round/Rect/Slot – choose the desired hole shape. The preview above and options below update accordingly. This and the following options are available for a through-hole pad only (i.e. when

Multi-Layer is selected as the pad's Layer).

- Round – specifies a round hole shape (the default) for the hole size of a pad. Separate drill files (NC Drill Excellon format 2) are generated for each hole kind, as well as for plated and non-plated holes. There are up to six different drill files for these types.

- Rect – specifies a rectangle (punched) hole for this pad. Rectangle holes can be plated or unplated. Separate drill file (NC Drill Excellon format 2) are generated for each hole kind, as well as for plated and non-plated holes. There are up to six different drill files for these types.

- Slot – specifies a round-ended, slotted hole for this pad. Slotted holes can be plated or unplated. Separate drill file (NC Drill Excellon format 2) are generated for each hole kind, as well as for plated and non-plated holes. There are up to six different drill files for these types.

- Hole Size – this field displays the current hole size for the pad. The value specifies the diameter of the hole (as a round, square or slotted shape) in mils or mm to be drilled in the pad during fabrication. For SMD pads or edge connectors, this should be set to zero. The hole size can be set from 0 to 1000mil and can be set larger than the pad to define (copper-free) mechanical holes. Edit the value in this field to change the pad hole size. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

-

Tolerance – setting hole tolerance attributes can help determine the fits and limits of your board. Specify the minimum (-) and maximum (+) tolerances for the hole.

Component datasheets list a tolerance with plus/minus to accommodate variations in aging, wear, temperature, plating, material, machining, and so forth. As holes are drilled, drill bits wear and get smaller, or the drill may vibrate or wiggle slightly in a hole, causing a slightly larger hole. Mounting holes are then plated, and the plating may be thicker or thinner for each batch or position on the board. You also have to account for thermal expansion or shrinkage of the Printed Circuit Board PCB substrate as it is being processed. Therefore, hole tolerance is critical in the design process to accommodate all tolerance, drill wear or wobble, and plating variations.

- Length – displays the length for the hole of the pad. The value specifies the length of the hole in mm or mil, to be NC-routed in the pad during fabrication. The hole size can be set from 0 to 1000mil and can be set larger than the pad to define (copper-free) mechanical holes.

Edit the value in this field to change the length. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified. This option is not available if Round is selected.

- Rotation – displays the current hole's counterclockwise rotation in degrees. Edit this field to change the rotation. Minimum angular resolution is 0.001°. This option is not available if Round is selected.

- Plated – this option determines whether or not the pad has a plated hole. A checkmark in this field sets the pad as a plated hole pad. If both plated and non-plated pads exist in a design, the non-plated holes will be set to use different tools from the plated holes in the NC drill files.

Pad Features

Top Side / Bottom Side – select the desired option for the pad counterhole on the top/bottom side of the board. Available options: None, Counterbore, Countersink. These options are available for a round through-hole pad only (i.e. when Multi-Layer is selected as the pad's Layer and Round is selected as the pad's hole shape).

Paste Mask Expansion

- Rule – select to have the paste mask expansion for the pad follow the defined value in the applicable Paste Mask Expansion design rule.

- Manual – select to override the applicable design rule and specify the paste mask expansion value for the pad. You can then enter the desired paste mask expansion measurement or disable use of paste mask for the pad. The value can be defined as either an absolute value (mil/mm) or percentage of the pad area. When entering an absolute value, include the units when entering a value whose units are not the current default. Default units are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

Solder Mask Expansion

- Rule – select to have the solder mask expansion for the pad follow the defined value in the applicable Solder Mask Expansion design rule.

- Manual – select to override the applicable design rule and specify the solder mask expansion value for the pad.

- Top/Bottom – enter the top/bottom layer solder mask expansion value. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified. This field is accessible only if Tented is not enabled. The Bottom field is accessible if the

icon to the right of this region is set to

icon to the right of this region is set to  . When the icon is in its

. When the icon is in its  state, the value of the bottom layer solder mask expansion will be the same as for the top layer.

state, the value of the bottom layer solder mask expansion will be the same as for the top layer.

- Tented – check if it desired for any solder mask settings in the solder mask expansion design rules to be overridden, which results in no opening in the solder mask on the top/bottom layer of this pad and is therefore tented. Disable this option and this pad is affected by a solder mask expansion rule or specific expansion value.

- From Hole Edge – when enabled, the Solder Mask opening will follow the shape of the hole. The mask is therefore independent of pad shape and size and is scaled from both the hole size and shape. For example, a pad with a square hole will create a square mask opening that matches the hole dimensions, as well as the assigned expansion value. Also note that a pad's expansion mask opening size will track any changes in the hole size.

Testpoint

- Fabrication/Assembly – these options allow you to specify pads (thru-hole or SMD) to be used as testpoint locations in fabrication and/or assembly testing. Enable Top for this pad to be defined as a top layer testpoint. Enable Bottom for this pad to be defined as a bottom layer testpoint.

Via Properties

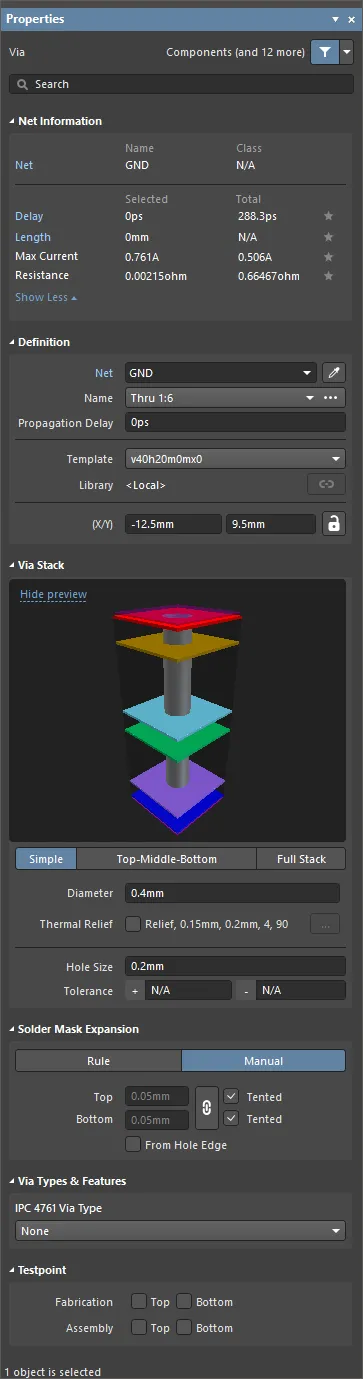

The Via mode of the Properties panel

Definition

- Component – this field is shown in the PCB editor only when the selected Via is a constituent part of a PCB Component and displays the designator of the parent PCB component. Select the clickable Component link to open the Component mode of the Properties panel for the parent component.

- Net – use to choose a net for the via. All nets for the active board design will be listed in the drop-down list. Select No Net to specify that the via is not connected to any net. The Net property of a primitive is used by the Design Rule Checker to determine if a PCB object is legally placed. Alternatively, you can click on the Assign Net icon (

) to choose an object in the design space - the net of that object will be assigned to selected via(s).

) to choose an object in the design space - the net of that object will be assigned to selected via(s).

- Name – when one or more via is/are selected, the via names are displayed by clicking the drop-down, which lists all of the via spans defined in the Layer Stack. All vias used on the board must be one of the via spans defined in the Layer Stack.

- Propagational Delay – this field lists the propagation delay, which is the amount of time it takes for the head of the signal to travel from the sender to the receiver.

- Template – displays the current template for the via. Use the drop-down to select another template. If there is an associated Library, that library will be displayed.

- Library – displays the via template contained in the current library. If a via is placed from a Pad Via Library (*.PvLib), it will include the name of that library in this field. Once placed, the

icon becomes enabled, which indicates that the properties of the placed via are defined in the Library, and are no longer editable. If the

icon becomes enabled, which indicates that the properties of the placed via are defined in the Library, and are no longer editable. If the  icon is not enabled, the contents can still be edited.

icon is not enabled, the contents can still be edited.

- (X/Y)

- X (first field) – this field shows the current X position of the center of the via relative to the current origin. Edit the value in the field to change the position of the via relative to the current origin. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

- Y (second field) – this field shows the current Y position of the center of the via relative to the current origin. Edit the value in the field to change the position of the via relative to the current origin. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

The

icon to the right of this region must be displayed as

(unlocked) in order to access the

X and

Y fields. Toggle the lock/unlock icon to change its lock status.

Via Stack

- Simple – select to choose a simple via.

- Diameter – enter the required diameter of the via. The via diameter is the same on all layers.

- Thermal Relief – check the box to enable thermal relief to reduce heat conductivity. Once checked, click

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

- Top-Middle-Bottom – select to choose different diameters for the top layer, all internal signal layers, and Bottom Layer.

- Displayed Layer(s) – click on a displayed layer to configure vias for that layer. The selected layer is highlighted.

- Diameter – click the drop-down then enter the required diameter of the via for the selected layer.

- Relief – check the box to configure the thermal relief, different from that defined in an applicable design rule, using the Thermal Relief option.

- Thermal Relief – check the box to enable thermal relief to reduce heat conductivity. Once checked, click

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

- Full Stack – select to choose a Full Stack via object.

- Displayed Layer(s) – click on a displayed layer to configure vias for that layer. The selected layer is highlighted.

- Diameter – click the drop-down then enter the required diameter of the via for the selected layer.

- Relief – check the box to configure the thermal relief, different from that defined in an applicable design rule, using the Thermal Relief option.

- Thermal Relief – check the box to enable thermal relief to reduce heat conductivity. Once checked, click

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

to open the Polygon Connect Style dialog in which you can choose the style of the connection: Relief Connect, Direct Connect, or No Connect.

- Hole Size – this field displays the current hole size for the via. The value specifies the diameter of the hole (as a round, square or slotted shape) in mils or mm to be drilled in the via during fabrication. The hole size can be set from 0 to 1000mil and can be set larger than the via to define (copper-free) mechanical holes. Edit the value in this field to change the via hole size. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified.

-

Tolerance – setting hole tolerance attributes can help determine the fits and limits of your board. Specify the minimum (-) and maximum (+) tolerances for the hole. There is no default hole tolerance value in Altium Designer.

Component datasheets list a tolerance with plus/minus to accommodate variations in aging, wear, temperature, plating, material, machining, and so forth. As holes are drilled, drill bits wear and get smaller, or the drill may vibrate or wiggle slightly in a hole, causing a slightly larger hole. Mounting holes are then plated, and the plating may be thicker or thinner for each batch or position on the board. You also have to account for thermal expansion or shrinkage of the Printed Circuit Board PCB substrate as it is being processed. Therefore, hole tolerance is critical in the design process to accommodate all tolerance, drill wear or wobble, and plating variations.

Solder Mask Expansion

- Rule – select to have the solder mask expansion for the via follow the defined value in the applicable Solder Mask Expansion design rule.

- Top

- Tented – check if it is desired for any solder mask settings in the solder mask expansion design rules to be overridden, which results in no opening in the solder mask on the top layer of this via and is therefore tented. Disable this option and this via is affected by a solder mask expansion rule or specific expansion value.

- Bottom

- Tented – check if it is desired for any solder mask settings in the solder mask expansion design rules to be overridden, which results in no opening in the solder mask on the bottom layer of this via and is therefore tented. Disable this option and this via is affected by a solder mask expansion rule or specific expansion value.

- Manual – select to override the applicable design rule and specify the solder mask expansion value for the via.

- Top – enter the top layer solder mask expansion value. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified. This field is accessible only if Tented is not enabled.

- Tented – check if it is desired for any solder mask settings in the solder mask expansion design rules to be overridden, which results in no opening in the solder mask on the top layer of this via and is therefore tented. Disable this option and this via is affected by a solder mask expansion rule or specific expansion value.

- Bottom – enter the bottom layer solder mask expansion value. The value can be entered in either metric or imperial; include the units when entering a value whose units are not the current default. Default units (metric or imperial) are determined by the Units setting in the Other region of the Properties panel in Board mode (accessed when no objects are selected in the design space) and are used if the unit is not specified. This field is accessible only if the

icon to the right of this region is set to

icon to the right of this region is set to  and the Tented option is not enabled. When the icon is in its

and the Tented option is not enabled. When the icon is in its  state and the Tented option is not enabled, the value of the bottom layer solder mask expansion will be the same as for the top layer.

state and the Tented option is not enabled, the value of the bottom layer solder mask expansion will be the same as for the top layer.

- Tented – check if it is desired for any solder mask settings in the solder mask expansion design rules to be overridden, which results in no opening in the solder mask on the bottom layer of this via and is therefore tented. Disable this option and this via is affected by a solder mask expansion rule or specific expansion value.

- From Hole Edge – when enabled, the Solder Mask opening will follow the size of the hole. The mask is therefore independent of via size and is scaled from the hole size. Also note that a via's expansion mask opening size will track any changes in the hole size.

Via Types & Features

- IPC 4761 Via Type – use the drop-down to select a via type according to the IPC 4761 standard, Design Guide for Protection of Printed Board Via Structures.

- Grid – appears when a via type other then

None is selected in the IPC 4761 Via Type drop-down. Select the board Side and type in a Material for the features available according to the selected via type.

Testpoint

- Fabrication/Assembly – these options allow you to specify vias to be used as testpoint locations in fabrication and/or assembly testing. Enable Top for this via to be defined as a top layer testpoint. Enable Bottom for this via to be defined as a bottom layer testpoint.

Testpoints

Related Documentation: Assigning Testpoints on the Board

The software provides full support for testpoints, allowing pads (thru-hole or SMD) and vias to be specified for use as testpoint locations in fabrication and/or assembly testing. A pad/via is nominated for use as a testpoint by setting its relevant testpoint properties – should it be a fabrication or assembly testpoint, and on which side of the board should it be used as a testpoint. These properties can be found in the Testpoint region of the Properties panel.

To streamline the process and alleviate the need for setting the testpoint properties manually, the software provides a method to automatically assign testpoints based on defined design rules and using the Testpoint Manager (Tools » Testpoint Manager). This automated assignment sets the relevant testpoint properties for the pad/via in each case.

Solder and Paste Mask Expansions

Solder and paste masks are created automatically at each pad site on the Solder Mask and Paste Mask layers, respectively. The shape that is created on the mask layer is the pad shape, expanded or contracted by the amount specified by the Solder Mask and Paste Mask design rules set in the PCB editor or as specified in the Properties panel.

Pads with the solder mask displayed.

When you edit a pad, you see the settings for the solder mask and paste mask expansions. While these settings are included to give you localized control of the expansion requirements of a pad, you will not normally need them. Generally, it is easier to control the paste mask and solder mask requirements by defining the appropriate design rules in the PCB editor. Using design rules, one rule is designed to set the expansion for all components on the board, then, if required, you can add other rules that target any specific situations, such as all instances of a specific footprint type used on the board, or a specific pad on a specific component, etc.

To set the mask expansions in the design rules:

- Confirm that the Rule option is selected in the Paste Mask Expansion and/or Solder Mask Expansion regions of the Properties panel.

- In the PCB editor, select Design » Rules from the main menus and examine the Mask category design rules in the PCB Rules and Constraints Editor dialog. These rules will be obeyed when the footprint is placed in the PCB.

To override the expansion design rules and specify a mask expansion as a pad attribute, select Manual in the Paste Mask Expansion and/or Solder Mask Expansion sections of the Properties panel and type the required value(s).

Partial and complete tenting of vias can be achieved by defining an appropriate value for Solder Mask Expansion. This expansion constraint can either be defined on a via-by-via basis in the Properties panel or by defining appropriate Solder Mask Expansion design rules. By setting the expansion value to a suitable value, you can achieve the following:

- To partially tent a via – covering the land area only, set the Expansion to a negative value that will close the mask right up to the via hole.

- To completely tent a via – covering the land and hole, set the Expansion to a negative value equal to or greater than the via radius.

- To tent all vias on a single layer, set the appropriate Expansion value and ensure that the scope (Full Query) of a Solder Mask Expansion rule targets all vias on the required layer.

- To completely tent all vias in a design, in which varying via sizes are defined, set the Expansion to a negative value equal to or greater than the largest via radius. When tenting an individual via, options are available to follow the expansion defined in the applicable design rule or to override the rule and apply a specified expansion directly to the individual via in question.

Pad Specifics

Pad Designators

Pads can be labeled with a designator (usually representing a component pin number) of up to 20 alphanumeric characters in length. Pad designators will auto-increment by one during placement if the initial pad has a designator ending with a numeric character. Change the designator of the first pad, prior to placement, from the Properties panel.

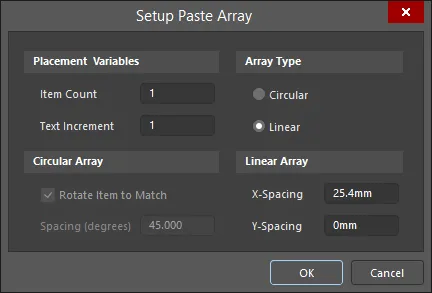

To achieve alpha increments, e.g,. 1A, 1B, or numeric increments other than 1, use the Setup Paste Array dialog accessed by pressing the Paste Array button in the Paste Special dialog (Edit » Paste Special).

Paste Array Feature

By setting the designator of the pad prior to copying it to the clipboard, you can use the Setup Paste Array dialog to automatically apply a designation sequence during pad placement. By using the Text Increment field in the Setup Paste Array dialog, the following pad designator sequences can be placed:

- Numeric (1, 3, 5)

- Alphabetic (A, B, C)

- Combination of alpha-numeric (A1 A2, 1A 1B, A1 B1, or 1A 2A, etc.)

To increment numerically, set the Text Increment field to the amount by which you want to increment. To increment alphabetically, set the Text Increment field to the letter in the alphabet that represents the number of letters you want to skip. For example, if the initial pad has a designator of 1A, set the field to A, (first letter of the alphabet) to increment designators by 1. If you set the field to C (third letter of the alphabet), the designators will become 1A, 1D (three letters after A), 1G, etc.

Jumper Connections

Jumper connections define electrical connections between component pads that are not physically routed with primitives on the PCB. These are especially useful on single-layer boards where a wire is used to jump over tracks on the one physical layer.

Pads within a component can be labeled with a Jumper value from within the Properties panel. Pads that share the same Jumper and electrical net tell the system that there is a legitimate, although physically unconnected, connection between them.

Jumper connections are shown as curved connection lines in the PCB Editor. The Design Rules Checker will not report jumper connections as unrouted nets.

Via Specifics

Defining the Via Properties

While the layer-spanning (Z-plane) requirements of each via type are defined on the Via Types tab of the Layer Stack Manager, the size properties of the via are defined by:

Configuring the Routing Via Style Design Rule

Main page: Defining, Scoping & Managing PCB Design Rules

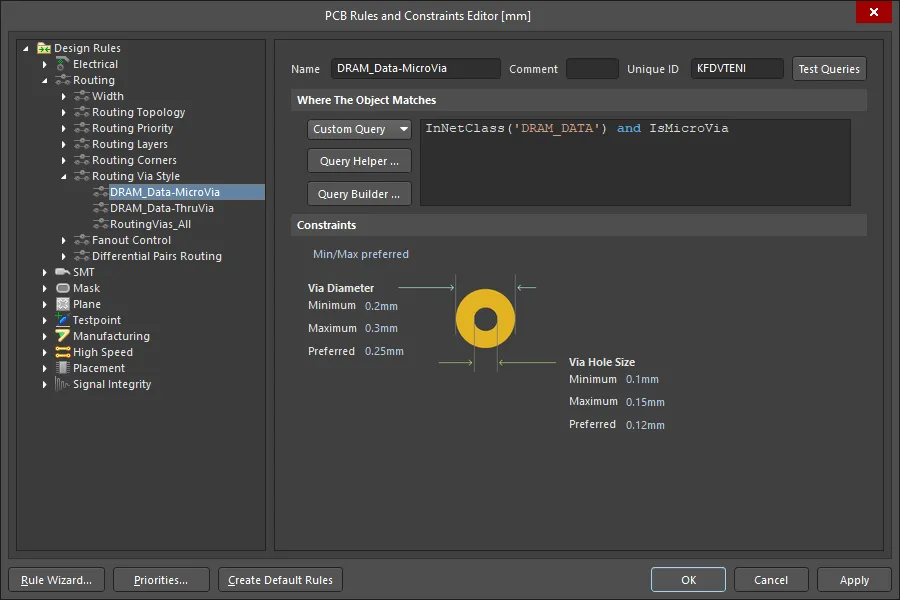

Vias that are placed during interactive routing, ActiveRouting, or autorouting, have their size properties controlled by the applicable Routing Via Style design rule. To help target vias in the design rule, there is a set of via-related query keywords that you can use in the rule scope (Where the Object Matches), these are detailed below.

When you perform a layer change as you route, the software looks at the start and stop layers for this layer change, and chooses an allowed Via Type from the Layer Stack Manager. It then identifies the highest priority applicable Routing Via Style design rule and applies the via size settings from the Constraints section of that rule, to the via about to be placed.

For example, you might have a set of DRAM_DATA nets that require µVias for the TopLayer - to - S2 layer transition and the S2 - to - S3 layer transition and a drilled thru-hole via for all other layer transitions (which is also different to the via required by other nets). This can be handled by creating two Routing Via Style design rules to target these DRAM_DATA nets. An example of a suitable µVia design rule is shown below, hover the cursor over the image to show the thru-hole design rule.

Design rules can be scoped to apply to specific types of vias.

When a via is placed in free space, it is not possible for the software to apply a routing style design rule during placement. In this situation, the default via will be placed.

Query Keywords

To simplify the process of scoping Routing Via Style design rules, the following via-related query keywords are available:

| Via Type Query |

Returns |

| IsVia |

All via objects, regardless of the Via Type. |

| IsThruVia |

All vias that span from the top layer to the bottom layer. |

| IsBlindVia |

All vias that start on a surface layer and end on an internal layer that are not a µVia. |

| IsBuriedVia |

All vias that start on an internal layer and end on another internal layer that are not a µVia. |

| IsMicroVia |

All vias that have the µVia option enabled, and connect adjacent layers. |

| IsSkipVia |

All vias that have the µVia option enabled, and span 2 layers. |

Use the Mask feature in the Query Helper to find available via-related keywords. Press F1 when a query keyword is selected in the list for help with that keyword.

Via Placement during Interactive Routing

When you change layers during interactive routing, the software will automatically insert a via. The via that is chosen depends on:

- The available Via Type(s) for the layers being spanned in the layer change.

- The applicable Routing Via Style design rule for the Via Type selected for that layer change.

To change layers during interactive routing:

- Press the * key on the numeric keypad to step to the next signal layer.

- Use the Ctrl+Shift+WheelRoll combination to step up or down through the layers.

Stacked µVias being placed during a layer change from L1 to L4. The Interactive Routing mode of the Properties panel displays the Via Type (s) that will be placed; press 6 to cycle through the possible via stacks; press 8 to display a list of possible via stacks.

Controlling the Via Placed during Interactive Routing

- As you change routing layers the software automatically chooses the most suitable Via Type to suit that layer span.

- If there are multiple Via Types/combinations (via stacks) that can be used - press the 6 shortcut key to interactively cycle through all via stacks available for that layer change, press the 8 shortcut to display a list. Via stacks are presented in the order: use µVia(s), use Skip µVia, use Blind via, use Thruhole via. Stacked vias can be placed if the layer change is more than one layer, and suitable Via Types are defined. The proposed Via Type(s) are detailed on the Status bar and in the Heads Up display, for example [µVia 1:2, µVia 2:3, µVia 3:4], as shown in the image above.

- The last-used via stack is retained as the default for the next net you route. The default via stack is retained for the current editing session only.

- The via size properties are specified by the applicable Routing Via Style design rule, strategies for defining a suitable Routing Via Style design rule are discussed above.

- To interactively change the via's size as a layer-change is being performed, press the 4 shortcut. This will cycle through the Via Size modes:

Rule Minimum; Rule Preferred; Rule Maximum; User Choice; with the current Via-Size mode being displayed on the Heads Up display and the Status bar (as shown in the image above). If User Choice is selected, press Shift+V to open the Choose Via Sizes dialog, and select a preferred via size. The list of available via sizes displayed in the dialog is taken from the list of vias already used in the design, inspect these in the Pad and Via Templates mode of the PCB panel.

- A side view of the proposed Via Type(s) is shown in the Properties panel, as shown above.

- To place a via and continue routing on the same layer, press the 2 shortcut.

- To place a via and suspend routing of this connection, press the / shortcut on the numeric keypad.

- If the net being routed is to connect to an internal power plane, press the / key (on the numeric keypad) to place a via connecting to the appropriate power plane. This will work in all track placement modes except Any Angle mode.

- Press Shift+F1 as you route for a menu of all in-command shortcuts.

Working with Stacked Vias

- Stacked vias that form a continuous connection can be worked with as if they are a single via, click and drag on the stack to move them all, with the attached routing.

- Click once to select the uppermost Via in the stack. If the mouse is not moved, subsequent single-clicks will select each of the other Vias in the stack, in turn.

- Ctrl+Click and drag to move only the selected Via with its attached routing.

- To select all Vias in a stack, click once to select one, then press Tab to extend that selection to include all Vias in that stack.

Configuring the Display of Vias

There are a number of display features available to help you work with vias.

Via Colors

Via colors are configured in the View Configuration panel. The copper ring of the via is shown in the current Multi-Layer setting in the Layers section. The via hole color is shown in the Via Holes setting in the System Colors section. You can also disable the display of holes by toggling the  for the desired setting(s).

for the desired setting(s).

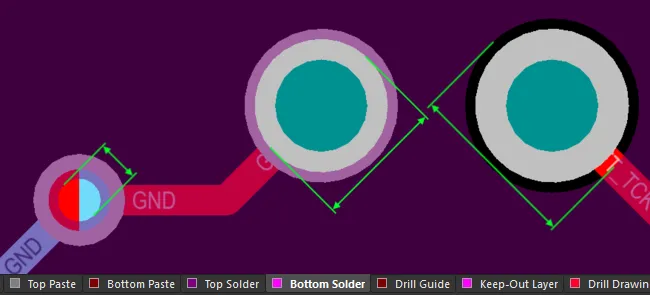

A thru-hole via is shown on the first image. The via on the second image is a blind via; the hole is shown in the start and end layer colors.

Vias and the Solder Mask

The default presentation of layers in the PCB editor is to always show the Multi-Layer as the topmost layer. That can make it difficult to accurately view the contents of the solder mask layers especially when a pad or via uses a negative mask expansion since the solder mask layer contents will disappear under the multi-layer object. You can change this by changing the layer drawing order on the PCB Editor – Display page of the Preferences dialog. Set the current layer to be drawn as the top-most layer.

By changing the layer drawing order to show the Current Layer on top, when you make the Top Solder the current layer, the mask openings are accurately presented as shown in the image below. The green arrows show the size of the solder mask opening for a via on the left, a pad where the mask opening is contracted in the center, and a pad where the opening is expanded on the right.

Configure the display settings to be able to examine the solder mask openings.

Display of Stacked Vias

If there are stacked vias, the displayed numbers are the start and end layers of all vias in the stack. Hover the cursor over the image below to show the vias in 3D, on the right of the image is a stack of three vias.

The spanned layers can be displayed in the vias. Hover the cursor to show the vias in 3D.

The spanned layers can be displayed in the vias. Hover the cursor to show the vias in 3D.

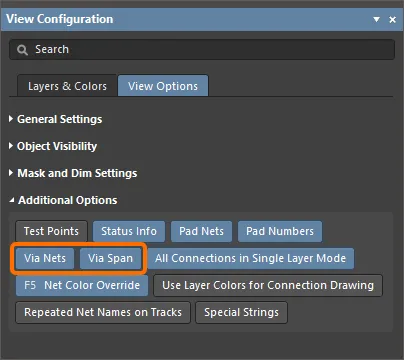

Other Via Display Settings

To display the via net name and layer numbers in the via span, enable the Via Nets and Via Span options respectively in the Additional Options region on the View Options tab of the View Configuration panel.

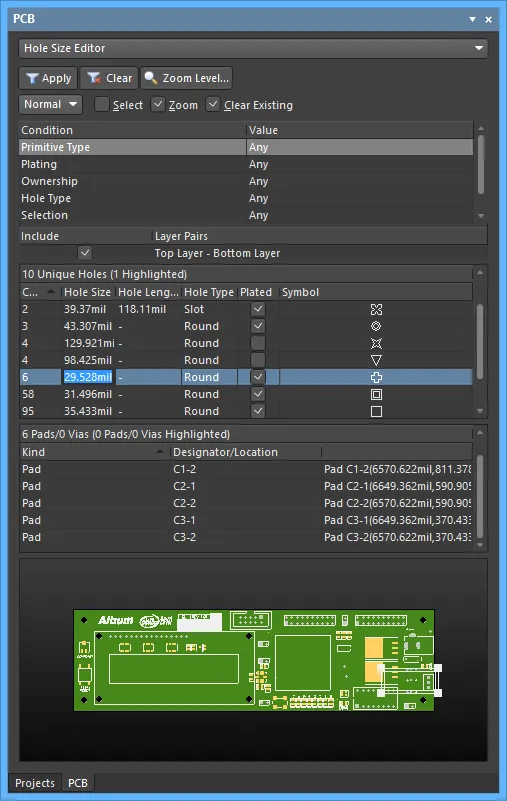

Browsing Pad and Via Holes

In the PCB panel’s Hole Size Editor mode, its three main regions change to reflect (in order from the top):

- The general filtering for hole types and their status, with a sub-section for the layer drill-pairs currently defined for the board.

- Unique Holes arranged in groups as determined by size and shape.

- Individual Pads/Vias that constitute each group of hole objects.

The panel sections show the cumulative filtering applied to hole types, styles and status.

The groups of holes can be collectively edited in the Unique Holes region of the panel by entering values in the appropriate column cell. You can enter a numeric value to change the current hole size for pads and vias in the Hole Size column.

Editing the hole size for the selected group of six matching hole styles.

You can also change the corresponding Hole Length, Hole Type, and Plated entries for holes where applicable.

Changing the hole type for the selected group of six matching hole styles.

Individual pad/via objects belonging to the selected holes group are listed in the lower Pad/Via section of the PCB panel. Right-click on an object in the list then select Properties (or double-click on the entry directly) to open the associated mode of the Properties panel for that primitive where its properties can be viewed and edited.

Support for Back Drilling

The Hole Size Editor mode of the PCB panel can also be used to examine pads and vias that are targeted for back drilling. Back drill layer pairs are displayed in the Layer Pairs list denoted by the addition of the text [BD].

When a back drill hole size is selected, the objects have their Kind displayed as Backdrill. Use this ability to quickly locate and examine back drilled holes. Note that back drill settings cannot be edited in the panel.

Back Drill Report

To generate a report of all back drill events, right-click in the Unique Holes list then select Backdrill Report from the context menu.

The report details each back drill event, including the location, drill size and drill depth.

Support for Counterholes

The Hole Size Editor mode of the PCB panel can also be used to examine pads with counterhole features enabled. When the PCB design has pad objects with counterhole (counterbore/countersink) features enabled for one or both sides, the associated Counterholes Top and/or Counterholes Bottom groups are displayed in the Layer Pairs list. The Counterhole Depth and Counterhole Angle columns can be displayed in the Unique Holes region of the panel. Note that counterhole settings cannot be edited in the panel.

Information about counterholes in the design is displayed in the PCB panel’s Hole Size Editor mode.