High Speed Design Rule Types Available for PCB Layout in Altium Designer

The design rules of the High Speed category are described below.

The High Speed category of design rules.

Parallel Segment

Default Rule: not required

This rule specifies the distance two track segments can run in parallel, for a given separation.

Constraints

Default constraints for the Parallel Segment rule

- Layer Checking - specifies where the two track segments to be checked should reside:

- Same Layer - the track segments for the targeted nets are both on the same layer

- Adjacent Layers - the track segments for the targeted nets are on adjacent layers.

- For a parallel gap of - specifies the parallel gap that should exist between two track segments before they can be considered for test. Parallel track segments with a gap of this value or less will be tested.

- The parallel limit is - specifies the maximum permissible parallel length of two track segments (on different nets), when the parallel gap constraint is observed over the entire length.

Rule Application

Online DRC and Batch DRC.

Note

This rule detects parallel track segments that are within the parallel gap setting, then adds all segment lengths that are in those nets. When the sum of these segment lengths exceeds the parallel limit, a DRC violation is flagged. A simple example is shown below.

Length

Default Rule: not required

This rule specifies the minimum and maximum lengths of a net.

Constraints

Default constraints for the Length rule

- Length Units - choose this option to define the length as a distance.

- Delay Units - choose this option to define the length as a time (how long the signal takes to travel along that length of route).

- Minimum - the value for the minimum permissible length of the net.

- Maximum - the value for the maximum permissible length of the net.

Rule Application

Interactive length tuning, automatic length tuning, online and batch DRC.

Note

The PCB editor can add accordion sections to nets to increase their lengths. The Interactive Length Tuning commands in the Route menu provide a variety of tuning shapes and allow you to selectively place the tuning accordions in accordance with the applicable Length design rule (as well as any applicable Matched Length design rule). Alternatively, select a set of nets and tune all selected net lengths automatically, using the Route » Automatic Length Tuning command. Refer to the Length Tuning page to learn more about the interactive and automatic length tuning commands.

Matched Lengths

Default Rule: not required

This rule specifies the allowable difference in net lengths. This rule is essential in a high-speed design, where the challenge is not just about how long it takes the signals to arrive (which is determined by their overall length), but how important it is that the specified signals arrive at the same time. Depending on the signal switching speeds, the function of the signal, and the materials used in the board, the allowed difference could be as much as 500mils, or as little as 1mil.

The set of nets being targeted is defined by the scope of the rule (as defined by its full query), with the reference length (the longest net in the set) being determined by the rule scope, in combination with the Constraints settings. Other targeted nets will pass the rule if their Current Length is:

(LongestLength - tolerance) ≤ CurrentLength ≤ LongestLength

Constraints

Default constraints for the Matched Lengths rule. Roll the mouse over the image to compare the two modes of operation available.

- Length Units - choose this option to define the length as a distance.

- Delay Units - choose this option to define the length as a time (how long the signal takes to travel along that length of route).

- Tolerance - specifies a length tolerance when comparing each net with the longest net in the set. Any net whose length does not lie within the specified tolerance is deemed to be too short and will have track added to it should the Equalize Net Lengths command be run.

-

Source Target - this drop-down is only available when an xSignal class (or all xSignals of the design) is used as the rule scope. Select an xSignal from the drop-down to use its length as a target for other xSignals scoped by the rule. When an xSignal is selected as a source target, other targeted xSignals will pass the rule if their Current Length is:

(TargetLength - tolerance) ≤ CurrentLength ≤ (TargetLength + tolerance) - Group Matched Lengths - choose this option to check lengths between all nets targeted by the rule scope.

- Within Differential Pair Length - choose this option to check lengths between the nets in each differential pair targeted by the rule scope. Refer to the Notes section to learn more.

Rule Application

Interactive length tuning, automatic length tuning, online and batch DRC.

Notes

- The PCB editor can add accordion sections to nets to equalize their lengths. The Interactive Length Tuning commands in the Route menu provide a variety of tuning shapes and allow you to selectively place the tuning accordions in accordance with the applicable Matched Length design rule (as well as any applicable Length design rule). Alternatively, select a set of nets and tune all selected net lengths automatically, using the Route » Automatic Length Tuning command. Refer to the Length Tuning page to learn more about the interactive and automatic length tuning commands.

- When scoping a Matched Net Length rule for interactive tuning purposes:

- For individual nets - define a class containing the nets that you wish to tune (Net, Differential Pair or xSignal class), and scope the rule to target that class. The length tuning tool will then find the longest net in that set of target nets and give you a valid range for the target nets of:

(LongestLength - tolerance) ≤ CurrentLength ≤ LongestLength. - For differential pair nets - if there are multiple differential pairs and the design requires pair-to-pair matched net lengths, you will create two Matched Net Length rules. The first rule defines the pair-to-pair length matching requirements, and has the Constraint set to Group Matched Lengths. The second rule is to ensure the nets within each differential pair are within tolerance and have the Constraint set to Within Differential Pair Length. When this Constraint option is used, the software will detect all differential pairs targeted by the rule scope, and then compare the +ve and -ve members of each pair against each other.

- For individual nets - define a class containing the nets that you wish to tune (Net, Differential Pair or xSignal class), and scope the rule to target that class. The length tuning tool will then find the longest net in that set of target nets and give you a valid range for the target nets of:

- When there are multiple rules applied to an object, the standard approach used by the PCB editor is to apply the highest priority rule. This is not the case for Matched Length design rules, where multiple rules can legitimately be applied to an object. For example, it is common to define tighter matching within say, an 8-bit bus, and at the same time require that several 8-bit busses all match as well, with a larger tolerance. In this situation, the priorities of these two rules are ignored.

Daisy Chain Stub Length

Default Rule: not required

This rule specifies the maximum permissible stub length for a net with a daisy chain topology.

Constraints

Default constraints for the Daisy Chain Stub Length rule

Maximum Stub Length - the value for the maximum stub length allowed.

Rule Application

Online DRC and Batch DRC.

Vias Under SMD

Default Rule: not required

This rule specifies whether vias can be placed under SMD pads.

Constraints

Default constraints for the Vias Under SMD rule

Allow Vias under SMD Pads - specifies whether vias can be placed under the pads of a Surface Mount Device (SMD).

Rule Application

Online DRC, Batch DRC, interactive routing, and autorouting.

Notes

- This rule applies only to pad objects defined on a single copper Layer (not Multi-Layer).

- The scope of the rule (Where the Object Matches) defines which SMD pad objects are targeted by this instance of the rule. When a pad falls within the rule's scope (is detected by the rule), the pad is then checked to see if it complies with the Allow Vias under SMD Pads constraint setting defined by this rule.

- The rule is to allow / not allow vias under SMD pads. If vias are allowed, the rule does not check if the via is only partially under the SMD pad, or the properties of that via.

- If there are multiple vias under an SMD pad where they are not allowed, only the first via detected during rule checking is flagged. Once this violation is cleared, the next violating via is flagged, and so on.

-

To selectively allow vias under SMD pads, globally disallow vias under any SMD pad, then define one or more rules to selectively allow them under specific pads, as shown in the image below. To achieve this, create:

- A general, lower priority rule targeting All SMD pad objects. The Allow Vias under SMD Pads constraint is disabled for this rule, not allowing vias under any SMD pads. (show rule)

- One (or more) higher priority rules then selectively define which SMD pads are allowed to have vias under them. This is achieved using rule scopes that target SMD pads, such as HasFootprint, InComponentClass, and InPadClass.

Multiple rules have been defined to only allow vias under the pads: in a class of pads, all pads in a class of components, and all pads in a specific footprint. - The Allow Vias under SMD Pads rule cannot check that a specific via is being used under an SMD pad, it only detects if a via is allowed / not allowed under the specified SMD pad. To check that a via under an SMD pad has specific qualities, such as being a MicroVia, or is using a specific PadViaTemplate, use a set of Same-Net Clearance Constraint rules. As with the Allow Vias Under SMD rule, this approach also requires a lower priority rule to not allow a Via Under an SMD pad, combined with higher priority rules that then selectively allow vias under SMD pads, based on their properties. The image below shows:

- A general, lower priority Same-Net rule that specifies a suitable via to SMD pad (and hole) clearance (detects all vias under any pad). (show rule)

- A rule to allow zero clearance (and zero hole clearance) between SMD pads and MicroVias that use a specific PadVia template. (show rule)

- A rule to allow zero clearance (and zero hole clearance) between SMD Pads and vias that are IPC4761 Type 7 compliant. (show rule)

Multiple rules have been defined to only allow zero clearance between vias (and via holes) and SMD pads for: MicroVias using a specific PadVia Template, or IPC4761 Type 7 compliant vias.

Maximum Via Count

Default Rule: not required

This rule specifies the maximum number of vias permitted for each individual net in the current design.

Constraints

Default constraints for the Maximum Via Count rule

Maximum Via Count - the maximum number of vias permitted in each individual net falling under the defined scope of the rule.

Rule Application

Online DRC and Batch DRC.

Max Via Stub Length (Back Drilling)

Default Rule: not required

A stub is the length of via or pad barrel that protrudes beyond the last-used signal layer that the via/pad connects on. Back drilling will be applied to suitable vias/pads in nets targeted by this rule, in accordance with the enabled side-of-board Layer checkboxes, and the back drill pairs defined on the Back Drills tab of the Layer Stack Manager.

As well as being used to define which vias/pads are to be considered for back drilling, during design rule checking this rule tests for via and pad stubs longer than the specified Max Stub Length, for all nets targeted by this rule (regardless of whether back drilling has been applied to that via or pad). This rule also specifies how much larger the drill size must be for vias and pads that are back drilled.

Constraints

Default constraints for the Max Stub Length rule

- Max Stub Length - the maximum length of stub allowed. This setting is used to test for remaining stubs of this length or longer, it does not define the drill depth used for back drilling.

- Top Layer - back drill vias/pads, in targeted nets, from the top side of the board.

- Bottom Layer - back drill vias/pads, in targeted nets, from the bottom side of the board.

- Back Drill Oversize - the radial increase in size of the drill used for back drilling, over the original via/pad hole size.

- Tolerance - allowable +ve and -ve tolerance allowed on this drill size, enter both as a positive number.

Rule Application

Batch DRC.

Return Path

Default Rule: not required

This rule specifies a continuous signal return path along the designated reference layer above or below the signals targeted. The return path can be created from fills, regions, and polygon pours placed on a signal layer or plane layers.

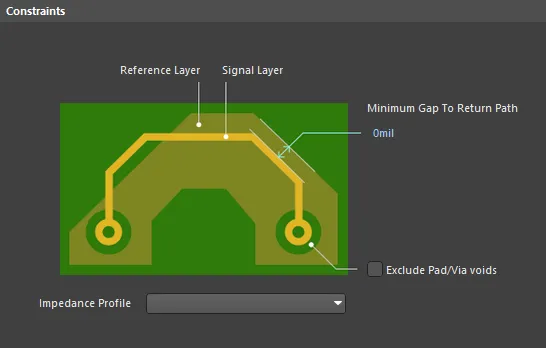

Constraints

Default constraints for the Return Path rule

- Exclude Pad/Via Voids - when enabled, openings in the return path created by the clearance around pads and vias that belong to the targeted net(s), are not flagged as violations.

- Minimum Gap to Return Path - indicates the minimum gap from the conductor edge to the outer edge of the return path. The check is applied along the entire length of the conductor. An error will be flagged if the gap is equal to or less than the Minimum Gap to Return Path value (default value is 0 mm).

- Impedance Profile - select the applicable impedance profile for the nets targeted by this rule. The profile specifies which layer(s) provide the return path for the targeted signals. Once the layer stack has been selected, the available signal layers and their respective reference layers, will be shown in the grid region of the dialog.

Rule Application

Batch DRC.