The PCB is designed and formed as a stack of layers. In the early days of printed circuit board (PCB) manufacturing, the board was simply an insulating core layer clad with a thin layer of copper on one or both sides. Connections are formed in the copper layer(s) as conductive traces by etching away (removing) unwanted copper.

A single-sided PCB is shown on the left, typical of early PCB design. On the right is a rigid-flex PCB, where rigid sections are connected via flexible sections of PCB.

Fast forward to today, where almost all PCB designs have multiple copper layers. Technological innovation and refinements in processing technology have led to a number of revolutionary concepts in PCB fabrication, including the ability to design and manufacture flexible PCBs. By joining rigid sections of PCB together via flexible sections, complex, hybrid PCBs can be designed that can be folded to fit into unusually shaped enclosures.

In printed circuit board design, the layer stack defines how the layers are arranged in the vertical direction or Z plane. Since it is fabricated as a single entity, any type of board, including a rigid-flex board, must be designed as a single entity. To do this, the designer must be able to define multiple PCB layer stacks and assign different layer stacks to different zones of the rigid-flex design.

Learn more about Rigid-Flex Design

The Layer Stack Manager

The definition of the PCB layer stack is a critical element of successful printed circuit board design. No longer just a series of simple copper connections that transfer electrical energy, the routing of many modern PCBs is designed as a series of circuit elements or transmission lines.

Achieving a successful, high-speed PCB design is a process of balancing the material selection and layer stackup and assignment against the routing dimensions and clearances required to achieve suitable single-sided and differential routing impedances. There are also numerous other design considerations that come into play when designing a modern, high-speed PCB, including layer-pairing, careful via design, possible back drilling requirements, rigid/flex requirements, copper balancing, layer stack symmetry, and material compliance.

The Layer Stack Manager combines all these layer-specific design requirements into a single editor.

To open the Layer Stack Manager select Design » Layer Stack Manager from the main menus of the PCB editor.

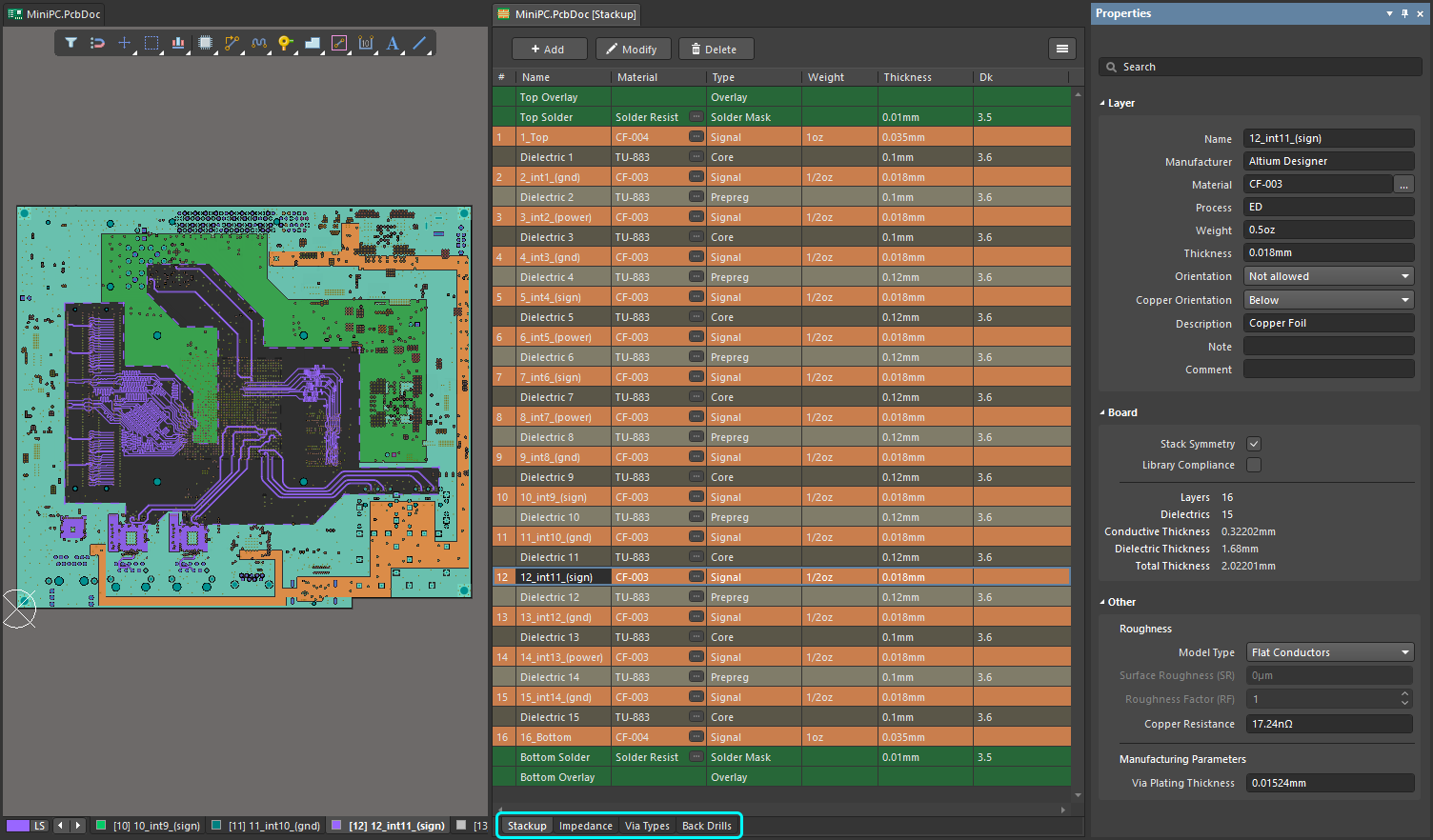

All aspects of layer stack management are performed in the Layer Stack Manager.

The Layer Stack Manager is used to:

-

Add, remove, and order the signal, plane, and dielectric layers.

-

Select the Material properties from the Materials Library, or configure them manually.

-

Add additional user-defined fields to the Layer Stack.

-

Configure the allowed Via Types, defining which layers each Via Type spans.

-

Configure the Impedance profiles, when controlled impedance routing is being used.

-

Configure advanced features, including rigid-flex design, printed electronics, and back drilling.

The Layer Stack Manager opens in a document view, in the same way as a schematic sheet, the PCB, and other document types. It can be left open while the board is being worked on, allowing you to switch back and forth between the board and the LSM. All of the standard view behaviors, such as splitting the screen or opening on a separate monitor are supported.

Note that a

Save action (

File » Save to PCB, shortcut:

Ctrl+S) must be performed in the

Layer Stack Manager before changes are reflected in the PCB.

The functionality is divided over a number of tabs displayed across the bottom of the Layer Stack Manager:

Stackup Tab - add, remove and configure the layer properties of all layers

The Stackup tab details the fabrication layers. Layers are added, removed and configured in this tab. For a rigid-flex design, layers are also enabled and disabled in this tab.

► Configuring the Stackup in the Properties panel

A maximum of 32 signal layers and 16 plane layers can be added. If required, plane layers can be split any number of times, and split-within-split areas defined: learn more.

Impedance Tab - configure the Impedance Profile requirements

This tab is used to define impedance profiles, which can then be used with routing design rules.

-

Click on the Impedance Tab at the bottom of the Layer Stack Manager to configure the Impedance Profile requirements. Once the impedance profiles have been configured, the required profile can then be selected in the Routing Width or

![]() Differential Pairs Routing design rules.

Differential Pairs Routing design rules.

-

Click

(or the Add Impedance Profile button if no profiles have been added yet) to add a new

(or the Add Impedance Profile button if no profiles have been added yet) to add a new ![]() Impedance Profile, then define the required Type, Target Impedance and Target Tolerance in the Properties panel. The Description is optional.

Impedance Profile, then define the required Type, Target Impedance and Target Tolerance in the Properties panel. The Description is optional.

-

The next step is to define which layers the currently selected profile will be available on. The grid is divided into two zones: the layers in the stackup are displayed on the left, and on the right are the layers that the currently selected impedance profile will be available on. Use the layer checkbox in the Impedance Profile region to make that layer available for the selected impedance profile.

-

When you select an enabled layer in the Impedance Profile region, all layers in the layer stack are faded, except those being used to calculate the impedance for that selected signal layer (show image

![]() ).

).

-

Once the layer has an Impedance Profile assigned, edit that layer's reference layer(s) in the Top Ref and Bottom Ref columns. Note that reference layer(s) can be of Type Plane or Signal.

-

The impedance calculators support forward and reverse impedance calculations. If you enter the Target Impedance, the Width will change automatically (forward calculation), or enter the Width and the Target Impedance will change automatically (reverse calculation).

-

For a differential impedance calculation, lock either the Width or Trace Gap by clicking the appropriate

button. The unlocked variable will then be calculated as the Target Impedance value changes. Alternatively, edit the unlocked variable to change the Target Impedance.

button. The unlocked variable will then be calculated as the Target Impedance value changes. Alternatively, edit the unlocked variable to change the Target Impedance.

-

The Etch Factor =

Thickness/[(W1-W2)/2] (hover the cursor over the ? in the panel to display the formula)

-

The impedance calculator supports multiple adjacent dielectric layers. These layers can have different dielectric properties.

-

For a stripline structure, the dielectric height is calculated as the distance between copper layers (see H2 on the image

![]() ).

).

-

The differential impedance calculator supports an asymmetric stripline structure.

-

Single and differential coplanar structures are supported by the Simbeor impedance calculator.

-

All calculations use a frequency of 1 GHz.

-

To improve calculation speeds, impedance profiles are calculated in separate threads (when available).

Via Types Tab - define the allowed Z-plane layer-spanning requirements of the vias

The Via Types tab is used to define the allowed Z-plane layer-spanning requirements of the via(s) used in the design. The diameter and hole size (X&Y properties) of the vias placed in the design continue to be controlled by the default preferences if the via is placed manually or the applicable Routing Style design rule if the via is placed during interactive routing.

-

The Layer Stack for a new board includes a single, thruhole via span definition in the Via Types tab of the Layer Stack Manager. For a two-layer board, the default via is named Thru 1:2, the naming reflecting the via type and the First and Last layers that the via spans. The default thruhole span cannot be deleted.

-

Click the

button to add an additional Via Type, then select the layers that this Via Type spans in the Properties panel. The new definition will have a name of <Type> <FirstLayer>:<LastLayer> (e.g., Thru 1:2).

button to add an additional Via Type, then select the layers that this Via Type spans in the Properties panel. The new definition will have a name of <Type> <FirstLayer>:<LastLayer> (e.g., Thru 1:2).

-

The software will automatically detect the type (e.g., Thru, Blind, Buried) based on the layers chosen and name the Via Type accordingly.

-

If a µVia is required, enable the µVia checkbox. This option will be only available when the via spans adjacent layers or adjacent +1 (referred to as a Skip via).

-

If the Layer Stack has the Stack Symmetry option enabled, the Mirror option will become available. When Mirror is enabled a mirror of the current via, spanning the symmetrical layers in the layer stack, is automatically created.

-

Vias placed in the workspace include a Name property dropdown, which lists all of the Via Types defined in the Layer Stack Manager. All vias used in the board must be one of the Via Types defined in the Layer Stack Manager.

-

When you change layers during interactive routing:

-

The Properties panel will display the applicable Via Type (show image

![]() ).

).

-

If multiple Via Types are available to suit the layers being spanned, press the 6 shortcut to cycle through the available Via Types.

-

The proposed Via Type is detailed on the Status bar (show image

![]() ).

).

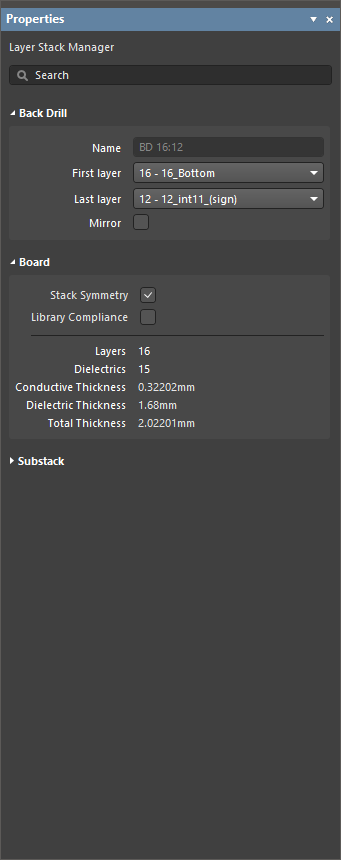

Back Drills Tab - define the layer-spans that are required to be back drilled

In a high-speed design, signal reflections can occur when the barrel of a via extends beyond the signal layers that the signal is routed on. This can lead to signal degradation and signal integrity issues. One approach used to resolve this is to drill out the unused via barrels using controlled depth drilling, which is a technique also referred to as back drilling.

-

Back drill properties are configured in the Back Drills tab, this tab appears when Back Drills are enabled in the Tools » Features sub-menu or by clicking the

button then choosing Back Drills.

button then choosing Back Drills.

-

The Back Drills tab is used to define the layer spans that are required to be back-drilled when there is a pad or via stub present. These settings are used in conjunction with the Max Via Stub Length design rule, where the maximum stub length and the drill oversize amount are specified. The Where the Object Matches setting in the rule can be used to restrict stub-removal to specific nets.

-

Click the

button to add a new back drill definition. The definition will be named according to the First layer and Last layer selected in the Back Drill section of the Properties panel, for example, BD 1:3. First layer defines the first layer to be drilled, Last layer defines the layer that drilling stops before (Last layer is the first layer in the layer stack that will not be back drilled).

button to add a new back drill definition. The definition will be named according to the First layer and Last layer selected in the Back Drill section of the Properties panel, for example, BD 1:3. First layer defines the first layer to be drilled, Last layer defines the layer that drilling stops before (Last layer is the first layer in the layer stack that will not be back drilled).

-

If the Substack Properties has the Stack Symmetry option enabled in the Properties panel, the Mirror option will become available in the Back Drill section of the panel. When this is enabled, a mirror of the current Back Drill is created, for example, BD 1:3 | 6:4.

Printed Electronics Stackup Tab - configure the layers for a printed design

Using modern printing technology, it is possible to print conductive and non-conductive layers directly onto a substrate material, building up an electronic circuit. This is referred to as printed electronics.

-

The layer stack is configured for printed electronics by selecting the

Tools » Features » Printed Electronics option. In this mode, all tabs are replaced by the single Printed Electronics Stackup tab.

Tools » Features » Printed Electronics option. In this mode, all tabs are replaced by the single Printed Electronics Stackup tab.

-

Traditional dielectric layers are not used in printed electronics. Instead, local dielectric patches are printed where routing must cross over. When the Printed Electronics option is enabled in the Features drop-down, all dielectric layers are removed from the layer stack and instead, the dielectric patches are defined by placing suitably shaped region objects on non-conductive layers.

-

In printed electronics, copper signal layers are referred to as conductive layers, and insulating layers are referred to as non-conductive layers.

Board Tab - create and configure the substacks in a rigid-flex design

The Board tab is used to configure the different substacks required in a rigid-flex design. The Board tab is automatically displayed when Rigid-Flex (Advanced) mode is enabled. Note that it is not used/available when the standard Rigid-Flex mode is chosen.

The Board tab of the Layer Stack Manager is used to:

-

Add Substacks. Additional substacks can be quickly created from an existing substack using the Shift+Click shortcut to select the required layers and then dragging the selection horizontally to position it in the set of substacks.

-

Configure the relationships between layers in adjacent Substacks, e.g., Do they share layers (Common), or are the layers unique in that Substack (Individual)?

-

Configure if adjacent layers intrude into the neighboring Substack.

-

Switch to editing a specific substack - double-click on it in the Board tab to do this.

-

Add additional Branches. Branches are used when the design has multiple flex sections radiating from a single rigid section. Learn more about Branches.

The Board tab was introduced as part of the Advanced Rigid-Flex mode. Advanced Rigid-Flex supports design features such as overlapping flexible and rigid board regions, new Board Region and Bending Line behaviors, and the introduction of the Board tab in the Layer Stack Manager. You can switch between the standard Rigid-Flex mode and the Advanced Rigid-Flex mode by selecting the relevant command in the Layer Stack Manager, as shown below.

The interface changes as you select either the standard or Advanced Rigid-Flex mode (hover the cursor over the image to show the difference).

The interface changes as you select either the standard or Advanced Rigid-Flex mode (hover the cursor over the image to show the difference).

► Learn more about Designing a Rigid-Flex PCB.

To change the measurement units in the active layer stack, choose

Tools » Measurement Units then select the desired unit of measure (

mil,

in,

µ, or

mm) or use the

Ctrl+Q keyboard shortcut to cycle through the measurement units.

Editing the Layer Stack Properties

The Layer Stack Manager presents the layer properties in a spreadsheet-like grid. The properties can be edited directly in the grid or they can be edited in the Properties panel. The panel can be used in each of the Layer Stack Manager tabs, for example, giving access to the impedance profile and transmission line properties in the Impedance tab or the µVia settings in the Via Types tab.

A few of the modes of the Properties panel in the Layer Stack Manager

The Properties panel can be enabled/disabled via the  button at the bottom-right of the software.

button at the bottom-right of the software.

When the Stackup tab of the Layer Stack document is active, the Properties panel allows you to edit the layer properties of the Layer Stack.

-

Name – the name of the layer.

-

Manufacturer – the layer manufacturer.

-

Material – the layer material. This can be pre-defined in the Altium Material Library dialog (Tools » Material Library) in the Constructions field or user-defined in the Layer Stack. Click

to open the Select Material dialog to choose the desired material for the currently selected layer in the layer stack.

to open the Select Material dialog to choose the desired material for the currently selected layer in the layer stack.

-

Thickness – the thickness of the signal layer.

-

Dk – this is the Dielectric Constant (also referred to as εr in electromagnetics). This indicates the relative permittivity of an insulator material, which refers to its ability to store electrical energy in an electric field. For insulating purposes, a material with a lower dielectric constant is better, and in RF applications, a higher dielectric constant may be desirable. In addition, the lower the relative dielectric constant, the closer the performance of the material to that of air. This property is critical to matching the impedance requirements of certain transmission lines.

-

Df – this is the Dissipation Factor. This indicates the efficiency of insulating material by showing the rate of energy loss for a certain mode of oscillation, such as mechanical, electrical, or electromechanical oscillation. In other words, this is the property of a material that describes how much of the energy transmitted is absorbed by the material. The greater the loss tangent, the larger the energy absorption into the material. This property directly impacts the signal attenuation at high speeds.

-

Process – displays the copper plating process that is applied to the base copper that makes up the outer signal layers of the PCB (the Top Layer and Bottom Layer).

-

Weight – the weight of the copper per unit area, usually expressed in ounces/square foot (e.g., 0.5 oz/ft2).

-

Orientation – this defines which way the components point (orient) on that layer. For the top and bottom sides, this is set automatically in a new board. For other signal layers, it is used for:

-

Rigid-flex designs, where components mount on an inner signal layer that becomes a surface layer on a flex section, the software needs to know which way those components point. Use the drop-down to select the required orientation. Choices include: Not allowed, Top, and Bottom.

-

For a design that includes embedded components, the software must know which way a component points. Refer to the Designing a PCB with Embedded Components page for information regarding setting the component orientation in the layer stack. Use the drop-down to select the required orientation. Choices include: Not allowed, Top, and Bottom.

-

Copper Orientation – this defines the direction that the copper is laminated onto the core. Use the drop-down to select Above or Below, which determines the direction from which it is etched.

The

Copper Orientation can also be chosen using the drop-down in the

Copper Orientation column of the

Layer Stack. To enable the column, right-click in the header, choose

Select columns then enable the

Copper Orientation entry in the

Select columns dialog. Also, the

Trace Inverted option in the

Impedance Profile mode of the panel can be used to configure the copper orientation.

The orientation can be configured using the Copper Orientation drop-down in the Stackup mode of the Properties panel in the Copper Orientation column (if it is currently displayed) or by the Trace Inverted checkbox in the Impedance Profile mode of the Properties panel.

-

Pullback Distance – the distance from the plane edge to the board edge.

-

Frequency – this is the frequency at which the material is tested and the value that Dk / Df corresponds to a certain frequency. Frequency is also taken from material references.

-

Description – enter a meaningful description.

-

Constructions – for dielectric layers, this displays the constructions of the layer. The numerical reference relates to the structure of the woven glass fabric used in the dielectric layer material; these are standard references used by PCB fabricators.

-

Resin – displays the resin percentage of the layer.

Notes on Constructions and Resin:

The choice of laminate construction can significantly impact both cost and performance. As should be expected, a single-ply construction will typically represent a cost savings compared to a multiple-ply construction. The magnitude of these savings will depend on the specific glass styles involved and a host of other parameters. Performance can also be affected and should be considered when specifying the constructions to be used. First, single-ply constructions are often lower in resin content. The other main benefit of single-ply constructions is dielectric thickness control beyond resin content considerations. Tighter thickness tolerances can be achieved using a single-ply construction.

Constructions with relatively lower resin contents are often preferred since they result in less z-axis expansion and can therefore improve reliability in many applications. In addition, lower resin contents can also improve dimensional stability, resistance to warpage, and dielectric thickness control. On the other hand, constructions with higher resin contents result in lower dielectric constant values, which are sometimes preferred for electrical performance. In addition, a certain minimum resin content is required to ensure adequate resin-to-glass wet-out and to prevent voids from occurring within the laminate. The ability to wet out the glass filaments fully with resin is also important for CAP resistance.

-

Material Frequency – this is the frequency at which the material is tested and the value that Dk / Df corresponds to a certain frequency. Frequency is also taken from material references.

-

GlassTransTemp – this is the Glass Transition Temperature (also known as TG) and is the temperature at which the resin changes from a glass-like state to an amorphous state changing its mechanical behavior, i.e. expansion rate.

-

Note – enter any pertinent notes for the layer.

-

Comment – enter any necessary comments for the layer.

-

Stack Symmetry – enable to maintain layer stack symmetry. Refer to the Layer Stack Symmetry section to learn more.

-

Library Compliance – when enabled, for each layer that has been selected from the Material Library, the current layer properties are checked against the values of that material definition in the library.

-

Substack – this information is for the currently selected substack (layers, dielectric, thicknesses, etc.). As you switch from one substack to another, this information will update accordingly (for the currently selected substack).

The Substack region will only be available if the Rigid/Flex option is enabled in the Features drop-down.

-

Stack Name – enter the substack name. Naming the substack is useful when the X/Y stackup region is being assigned a layer substack.

-

Is Flex – enable if the substack is flex.

-

Layers – the number of conductive layers.

-

Dielectrics – the number of dielectrics.

-

Conductive Thickness – this is the sum of the thicknesses of all signal and plane layers (all copper or conductive layers).

-

Dielectric Thickness – the thickness of dielectric layer(s).

-

Total Thickness – the total thickness of the finished board.

-

Roughness – shows roughness of conductive layers.

-

Model Type – preferred model for calculating the impact of surface roughness (refer to the articles below for more information on the various models). Applies to all copper layers in the stack (should it be the substack?).

-

Surface Roughness – value of the surface roughness (available from your fabricator). Enter a value between 0 to 10µm, default is 0.1µm

-

Roughness Factor – characterizes the expected maximal increase in conductor losses due to the roughness effect. Enter a value between 1 to 100; the default is 2.

-

Copper Resistance - value of the copper resistance in nOhms.

-

Via Plating Thickness - the total thickness of the via plating.

To learn more about the options and controls available for the other Layer Stack tabs, use the links below:

Defining the Layer Stack

The layers you add in the Stackup tab of the Layer Stack Manager are the layers that will be fabricated during the manufacturing process.

Layer properties can be entered directly into the grid, or selected from the Material Library.

Layer properties can be entered directly into the grid, or selected from the Material Library.

The properties of a layer can be edited directly in the grid or in the Properties panel.

Configuring the Layer Properties and Materials

The properties of each layer can be edited directly in the LSM grid, or a pre-defined material can be selected from the Material Library by clicking the ellipsis button ( ) in the Material cell for the selected layer. The Stackup Tab collapsible section earlier on this page summarizes the various techniques available for adding, removing, editing, and ordering the layers.

) in the Material cell for the selected layer. The Stackup Tab collapsible section earlier on this page summarizes the various techniques available for adding, removing, editing, and ordering the layers.

User-defined property columns can be added and the visibility of all columns can be configured in the Select columns dialog. To open the dialog, right-click on any column heading in the grid region then choose Select columns from the context menu.

The Select columns dialog

Options and Controls of the Select columns Dialog

-

Filter - enter characters by which you want the list filtered.

-

List - this is a list of all possible columns that can be displayed in the Layer Stack Manager. When an item displays

, that column will be displayed in the Layer Stack Manager. When an item displays

, that column will be displayed in the Layer Stack Manager. When an item displays  , that column will not be displayed in the Layer Stack Manager. Click the symbols to toggle the show/hide function.

, that column will not be displayed in the Layer Stack Manager. Click the symbols to toggle the show/hide function.

-

Up/Down - click to move the selected item up or down in the list. This determines the order in which the columns will appear in the Layer Stack Manager.

-

Add - click to add a new column. A new column titled Custom[n] will be added to the Column list. Select the new column entry then click Edit to change the name, if desired.

-

Edit - click to edit the selected column. This is available only for a custom column that has been added. System columns cannot be edited.

-

- click to delete the selected column. This is available only for a custom column that has been added. System columns cannot be deleted.

- click to delete the selected column. This is available only for a custom column that has been added. System columns cannot be deleted.

Layer Types and their Properties

There is a large variety of materials used in the fabrication of a printed circuit board. The table in the collapsible section below gives a brief summary of the common materials used.

Summary of layers types and their properties

The selection of layer materials and their properties should always be done in consultation with the board fabricator.

| Layer Type |

Materials Used |

Comments |

| Signal |

Copper |

Copper layer used to define signal routing carries the electrical signals and circuit supply current. Typically annealed foil and electro-deposited. |

| Internal Plane |

Copper |

Solid copper layer used to distribute power and ground; can be split into regions. Also must specify the distance from the plane edge to the board edge (pullback). Typically annealed foil. |

| Surface Finish |

Varies, including Electroless Nickel Immersion Gold (ENIG), Hot Air Solder Leveling (HASL), Lead-Free (HASL), Immersion Tin, Organic Solderability Preservative (OSP)/Entek, Hard Gold, Immersion Silver

|

Applied to the exposed outer copper layers. Has two functions: to prevent oxidization of the copper and provide a good surface for solder adhesion. Different pros and cons for each type of finish. The most popular is ENIG, offering high quality, good solderability and low cost. |

| Dielectric |

Varies, including FR4, polyimide, and a variety of manufacturer-specific materials offering different design parameters |

Insulating layer; can be rigid or flexible. Used to define core, prepreg and flexible layers.

Important mechanical properties are: including dimensional stability over moisture and temp ranges, tear resistance, and flexibility.

Important electrical properties include insulation resistance, dielectric constant (Dk), and dissipation factor (loss tangent, Df or Dj)

|

| Overlay |

Screen printed epoxy, LPI (liquid photo-imageable) |

Present text/artwork, such as component designators, logos, product name, and so on. |

Solder Mask/Coverlay

|

1) Solder Mask - Liquid photo-imageable solder mask (LPI or LPSM) , Dry Film photo-imageable Solder Mask (DFSM)

2) Coverlay - Adhesive-coated flexible film, typically polyimide or polyester.

|

1) Protective layer that restricts where solder can be applied to the circuit. A cost-effective and proven technology, suitable for rigid and flex use class A (flex-to-install) applications. Suitable for finer features than flexible film coverlay.

2) Suitable for flex use classes A and B (dynamic flex). Requires rounded holes/corners, which are typically drilled or punched.

|

| Paste Mask |

Layer from which a paste mask stencil is fabricated. The stencil is typically stainless steel. Openings in the stencil define locations where solder paste is to be applied to the component pads prior to component placement. |

Mask layer is used to fabricate the solder mask screen, which defines locations where solder paste is to be applied. |

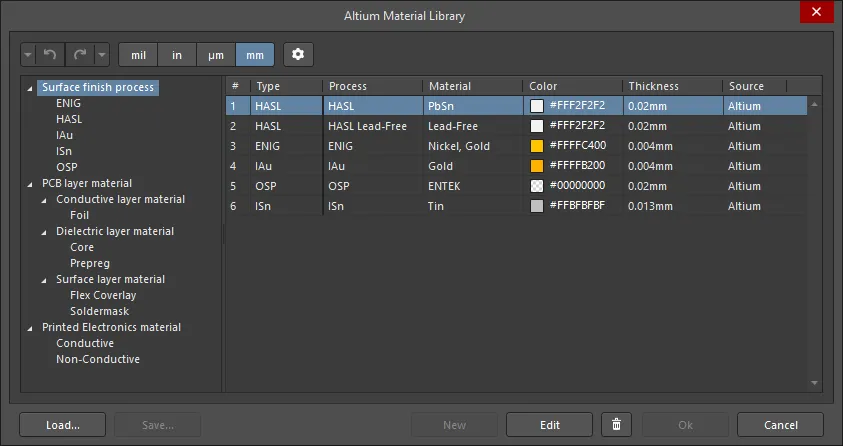

Materials Library and Library Compliance

Preferred layer stack materials can be pre-defined in the Material Library. In the Layer Stack Manager, select Tools » Material Library to open the Altium Material Library dialog, where existing materials can be reviewed and new material definitions added.

The Altium Material Library dialog

Options and Controls of the Altium Material Library dialog

-

/

/  - click to Undo or Redo the previous operation. Use the down arrows to access a list of prior operations from which you can choose.

- click to Undo or Redo the previous operation. Use the down arrows to access a list of prior operations from which you can choose.

-

Units - select the desired units. Supported units are mil, in, µm, and mm.

-

- click to open the Material Library Settings dialog to select the columns displayed in the dialog.

- click to open the Material Library Settings dialog to select the columns displayed in the dialog.

-

Left region - this tree displays the material types available. Click an item to display the details in the grid on the right.

-

Grid - this region displays the available materials for the selected item in the region on the left. Click the

in a header to filter the column by selecting the desired filter in the resulting drop-down.

in a header to filter the column by selecting the desired filter in the resulting drop-down.

-

Load - click to open a dialog to search for and select user-defined materials from an external Material Library Database (*.xml) to load into the dialog.

-

Save - click to save your user-specified materials to a Material Library Database (*.xml).

-

New - click to add a user-defined material. New material definitions will have their Source property set to User. This button is available provided the material type is selected in the tree on the left.

-

Edit - click to edit a selected user-defined material.

-

- click to delete a selected user-defined material.

- click to delete a selected user-defined material.

The material for a specific layer is not selected in the Altium Material Library dialog. To use a specific material for a layer, click the ellipsis ( ) for that layer in the Materials cell of the layer stack grid or click

) for that layer in the Materials cell of the layer stack grid or click  in the Material field in the Properties panel when the layer is selected in the layer stack grid. This will open the Select Material dialog, which restricts the library to only show materials suitable for the layer that the ellipsis control was clicked.

in the Material field in the Properties panel when the layer is selected in the layer stack grid. This will open the Select Material dialog, which restricts the library to only show materials suitable for the layer that the ellipsis control was clicked.

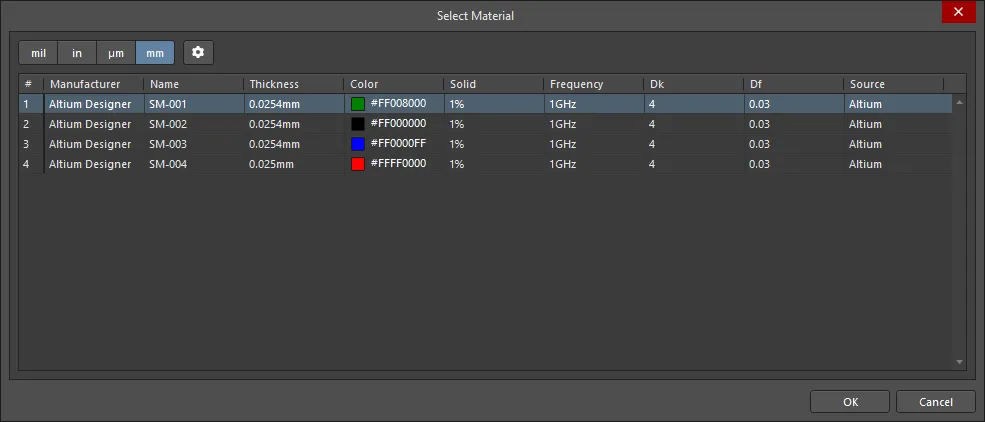

The Select Material dialog

Options and Controls of the Select Material Dialog

-

Units Selector - click the desired units for the Thickness: mil, in, µm, or mm.

-

- click to open the Material Library Settings dialog to select the columns displayed in the Select Material dialog.

- click to open the Material Library Settings dialog to select the columns displayed in the Select Material dialog.

-

Grid - the grid displays information about the materials suitable for the layer that was used to access the Select Material dialog. Select the desired item then click OK to use that material in the Layer Stack.

To select the columns displayed in the Altium Material Library dialog or the Select Material dialog, click the  button to open the Material Library Settings dialog.

button to open the Material Library Settings dialog.

The Material Library Settings dialog

Options and Controls of the Material Library Settings Dialog

-

Filter - enter characters by which you want the Column list filtered.

-

Column - this is a list of all possible columns that can be displayed in the Altium Material Library dialog or the Select Material dialog. When an item displays

, that column will be displayed in the Altium Material Library dialog or the Select Material dialog. When an item displays

, that column will be displayed in the Altium Material Library dialog or the Select Material dialog. When an item displays  , that column will not be displayed in the dialogs. Click the symbols to toggle the show/hide function.

, that column will not be displayed in the dialogs. Click the symbols to toggle the show/hide function.

-

Add - click to add a new column. A new column titled Custom[n] will be added to the Column list. Select the new column entry then click Edit to change the name, if desired.

-

Edit - click to edit the selected column. This is available only for a custom column that has been added. System columns cannot be edited.

-

- click to delete the selected column. This is available only for a custom column that has been added. System columns cannot be deleted.

- click to delete the selected column. This is available only for a custom column that has been added. System columns cannot be deleted.

-

Up/Down - click to move the selected item up or down in the Column list. This determines the order in which the columns will appear in the Altium Material Library dialog or the Select Material dialog.

If the Library Compliance checkbox is enabled in the Layer Stack Manager, then for each layer that has been selected from the Material Library, the current layer properties are checked against the values of that material definition in the library. Any property that is not compliant is marked with an error flag. Re-select the material ( ) to update the values to the Material Library settings.

) to update the values to the Material Library settings.

Layer Stack Symmetry

If you require the board layer stack to be symmetrical, enable the Stack Symmetry checkbox in the Board region of the Properties panel. When this is done, the layer stack is immediately checked for symmetry around the central dielectric layer. If any pair of layers that are equidistant from the central dielectric reference layer are not identical, the Stack is not symmetric dialog opens.

The Layer stack symmetry mismatches grid at the top of the dialog details all detected conflicts in layer stack symmetry.

The lower region of the dialog provides the following options available to achieve layer stack symmetry:

-

Mirror top half down - the settings of each of the layers above the central dielectric layer are copied down to the symmetrical partner layer.

-

Mirror bottom half up - the settings of each of the layers below the central dielectric layer are copied up to the symmetrical partner layer.

-

Mirror whole stack down - an additional dielectric layer is inserted after the last copper (Surface Finish) layer, and then all of the signal and dielectric layers are replicated and mirrored below this new dielectric layer.

-

Mirror whole stack up - an additional dielectric layer is inserted before the first copper (Surface Finish) layer, and then all of the signal and dielectric layers are replicated and mirrored above this new dielectric layer.

When Stack Symmetry is enabled:

-

An edit action applied to a layer property is automatically applied to the symmetrical partner layer.

-

Adding layers will automatically add matching symmetrical partner layers.

Use the Stack Symmetry option as a quick way of defining a symmetric board - define half of the layer stack, enable the Stack Symmetry option, then use one of the mirror whole stack options to replicate that set of layers.

Layer Stack Visualization

An excellent way to verify the layer stack is to visualize it in 3D. The Layerstack Visualizer dialog lets you see the layer stack in either 2D or 3D.

-

Select Tools » Layerstack Visualizer in the Layer Stack Manager to open the Layerstack Visualizer.

-

Use the controls to configure the presentation of the layer stack.

-

Right-click and drag to reorient the board in the visualizer.

-

Left-click on the image, then Ctrl+C to copy the image to the Windows clipboard.

Options and Controls of the Layerstack Visualizer Dialog

-

2D/3D - select in which view you want to see the layer stack.

-

Orthographic camera - enable to view using orthographic projection. Disable to view using perspective projection.

-

Show full stack - check to show the full stack.

-

Show layer names - check/uncheck to show/hide the layer names.

-

Real layers height - check/uncheck to display the layers' real height.

-

Space between layers - check/uncheck to display with space between layers.

-

Simple conductors - check to display with simple conductors.

Defining and Configuring the Rigid-Flex Substacks

Main page: Rigid-Flex Design

Rigid-Flex is under active development and now supports two modes of Rigid-Flex design. The original, or standard mode, referred to as Rigid-Flex, supports simple rigid-flex designs. If your design has more complex rigid-flex requirements, such as overlapping flex regions, then you need the Advanced Rigid-Flex mode (also known as Rigid-Flex 2.0). As well as overlapping flex regions, the Advanced mode also brings: a visual definition of the substacks, easier definition of the rigid and flexible board regions, bends on nested cutouts, custom-shaped splits, and support for bookbinder-type structures. The required mode is selected in the Layer Stack Manager, as shown below.

The interface changes as you select either the standard or Advanced Rigid-Flex mode (hover the cursor over the image to show the difference).

The interface changes as you select either the standard or Advanced Rigid-Flex mode (hover the cursor over the image to show the difference).

► Learn more about Designing a Rigid-Flex PCB.

Each separate zone or region of a rigid-flex design can be made up of a different number of layers. To achieve that you need to be able to define multiple stacks, referred to as substacks.

Adding Substacks in a standard Rigid-Flex design

Adding Substacks in an Advanced Rigid-Flex design

-

Enable the Rigid-Flex option by selecting the Tools » Features » Rigid/Flex (Advanced) command. You can also access the command in the Features (

) menu.

) menu.

-

In Advanced Rigid-Flex mode, the display will switch to show the Board tab, as shown below.

-

There must be a unique substack defined for each unique set of layers needed in the rigid and flex regions of the overall board. Board mode is used to configure the different substacks required in an Advanced rigid-flex design.

-

Additional substacks can be quickly created from an existing substack using the Shift+Click shortcut to select the required layers and then dragging the selection horizontally to position it in the set of substacks, as shown in the image below.

-

Configure the relationships between layers in adjacent Substacks - e.g., Do they share layers (Common), or are the layers unique in that Substack (Individual)?

-

Configure if adjacent layers intrude into the neighboring Substack.

-

Switch to editing a specific substack - double-click on it in the Board tab to do this.

-

Add additional Branches. Branches are used when the design has multiple flex sections radiating from a single rigid section.

-

For flex Substacks, enable the Is Flex option in the Properties panel. Flex-specific coverlay layers can only be added in a Substack that has the Is Flex option enabled and does not include a Soldermask layer.

► Learn more about Designing a Rigid-Flex PCB

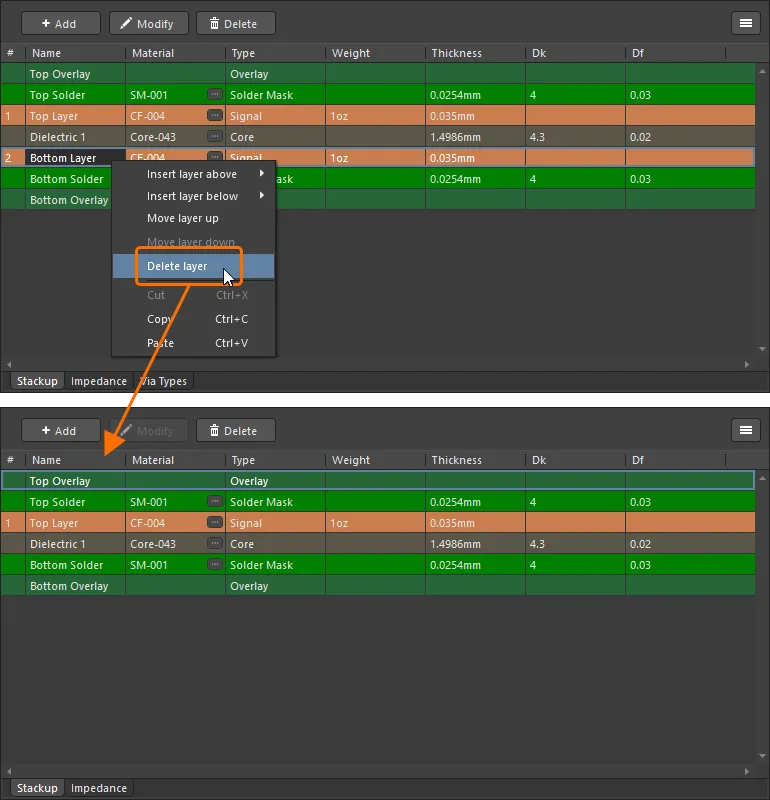

Single Layer PCB Support

A single-layer PCB stack can be created by deleting either the top or bottom layer from a 2-layer PCB stack.

In a 2-layer PCB, you can now delete either the Top or Bottom Layer from its layer stack.

-

A single-layer stack can be created for a PCB but not a footprint.

-

When the layer stack has a single copper layer, the Via Types tab and the Back Drills feature will not be available in the Layer Stack Manager.

-

For a single-layer PCB, you can only create impedance profiles of Single-Coplanar and Differential-Coplanar types on the Impedance tab of the Layer Stack Manager.

-

The removed layer is referenced as a side where applicable. For example, if the bottom layer is removed, it is called

Bottom Side in the Drill Layer Pair column of a drill table.

-

When there are unplated thru-hole pads in a single-layer PCB, they will not be flagged in the Unplated multi-layer pad(s) detected section of the DRC report.

Saving and Loading a Layer Stack

Saving and Loading a Layer Stack using a Stackup Document File

To save the current stackup to a stackup document file (*.stackup or *.stackupx), use the File » Save As command from the main menus. A dialog will open in which you can select the location, name and type of the file.

To load a stackup from an existing stackup document file, use the File » Load Stackup from File command from the main menus. The Open Stackup Document dialog will appear from where you can browse and open the desired file.

Saving and Loading a Layer Stack using a Connected Workspace

To save the current stackup to your connected Workspace, choose the File » Save to Server command from the main menus. The Choose Planned Item Revision dialog will appear – use this to choose an existing Workspace Layerstack to save the stackup to its next revision.

-

A new layerstack can also be created using the Layerstack command from the menu of the Add button or the context menu of the template grid on the Templates tab of the Data Management – Templates page of the Preferences dialog. After selecting the command, click OK in the Close Preferences dialog that opens to close the Preferences dialog and open the temporary Stackup Editor. A planned revision of the new Workspace Layerstack will be created automatically in a Workspace folder of the

Layerstacks type.

-

A new Workspace Layerstack can also be created by uploading an existing stackup document file (

*.stackup). Select the Load from File command from the menu of the Add button or the Add context menu of the template grid on the Templates tab of the Data Management – Templates page of the Preferences dialog. In the Open dialog (a standard Windows open-type dialog) that opens, select the Layer Stack-up File (*.stackup) option in the drop-down at the right of the File name field and use the dialog to browse to and open the required file that will be uploaded into the initial revision of the new Workspace Layerstack created automatically in a Workspace folder of the Layerstacks type.

-

If the required stackup document file resides in the Local Template folder (defined at the bottom of the Data Management – Templates page) and is listed under the Local entry of the template grid, it can be migrated to a new Workspace Layerstack by right-clicking on it and selecting the Migrate to Server command. Click the OK button in the Template migration dialog to proceed with the migration process – as stated in this dialog, the original layerstack file will be added to a Zip archive in the local template folder (therefore, it will not be visible under the Local template list).

-

A Workspace Layerstack can be previewed in the Explorer panel. When the layerstack entry is selected in the revision region of the panel, switch to the Preview aspect view tab to see the layer stackup.

To edit an existing Workspace Stackup, right-click on its entry on the Templates tab of the Data Management – Templates page of the Preferences dialog and choose the Edit command from the context menu. The temporary editor will open, with the template contained in the latest revision of the Workspace Stackup opened for editing. Make changes as required, then save the stackup into the next revision of the Workspace Stackup (right-click the stackup entry in the Projects panel and select Save to Server).

If you need to update a Workspace Stackup and you have an updated stackup document file, you can upload that file to that Workspace Stackup. From the

Templates tab of the

Data Management – Templates page of the

Preferences dialog, right-click on the template entry and choose the

Upload command from the context menu. Use the

Open dialog (a standard Windows open-type dialog) that opens to browse and open the required file that will be uploaded into the next revision of the Workspace Stackup.

To load a stackup from your connected Workspace, choose the File » Load Stackup From Server command from the main menus. The Choose Item Revision dialog will appear – use this to load layer stackup data from a Workspace Layerstack.

If you are not connected to your Workspace, you can still work with Altium Designer (under your valid Altium Designer license), but you will not be able to access your organization's Workspace or any other services it provides. You will, therefore, not be able to use any Workspace layerstacks. You can only use stackup document files (File » Load Stackup From File).

A Workspace layer stackup can also be used as a configuration data item in one or more defined

Environment Configurations. An environment configuration is used to constrain a designer's working environment to only use company-ratified design elements. Environment configurations are defined and stored within the Team Configuration Center – a service provided through the Workspace. Once you have connected to the Workspace and chosen (if applicable) from the selection of environment configurations available to you, Altium Designer will be configured with respect to the use of Layerstacks. If the chosen environment configuration has one or more defined Layerstack Item revisions, then

only those will be available to you for reuse. If the chosen environment configuration applicable to you does not have any layerstack revisions specified/added or is set to

Do Not Control, then all available saved item revisions (shared with you) will be available. You are also free to use local stackup files. For more information, see

Environment Configuration Management (

Altium 365 Workspace,

Enterprise Server Workspace).

Loading a Predefined Layer Stack

A number of pre-defined layer stacks are available in the Tools » Presets menu.

Exporting a Layer Stack

The current layer stack can be exported to a spreadsheet (*.csv) file by choosing the File » Export CSV command from the main menus. After launching the command, the Save As dialog opens in which you can select the desired location and name of the *.csv file.

Using the File » Export To Simbeor command, you can also export the layer stack to a Simbeor file (*.esx).

Other Layer-related Design Tasks

The layers in the layerstack form the space on which you build up the design. There are a number of design tasks that are related to the layers that are not performed in the Layer Stack Manager. These tasks are summarized below, with links to more information.

Defining the Board Shape

Where the layer stack defines the board in the Z-plane, the Board Shape defines the board in the X and Y planes. Also referred to as the board outline, the board shape is a closed polygonal shape that defines the overall extent of the board. The Board Shape can be made up of a single Board Region (for a traditional rigid PCB) or multiple board regions (for a rigid-flex PCB).

The Board Shape can be:

-

Defined manually - by redefining the existing shape or placing one or more new board regions in Board Planning mode.

-

Defined from selected objects - typically done from an outline on a mechanical layer. Use this option if an outline has been imported from another design tool.

-

Defined from a 3D body - use this option if the blank board has been imported as a STEP model from an MCAD tool into a 3D Body Object (Place » 3D Body).

-

Pulled directly from an MCAD package - Altium is developing direct ECAD - MCAD design technology called Altium CoDesigner. Learn more about ECAD-MCAD CoDesign.

Assigning a Net to a Plane Layer

Panel page: Split Plane Editor

Related page: Internal Power & Split Planes

Assign a net to a plane layer or a net to a split plane region in the Split Plane Editor mode of the PCB panel.

The panel lists all plane layers. When a layer is selected in the Layers section, the section below will list all of the split plane zones on that layer (there will only be one if the plane is continuous with no splits defined). Double-click on a split plane zone to open the Split Plane dialog to assign a net. You can also double-click on the layer in the workspace (when the plane layer is the active layer) to open the dialog.

Configuring the Layer Stack for Components Mounted on an Internal Signal Layer

Related article: Embedded Components

There are two situations where components can be mounted on an internal signal layer:

-

when there are embedded components, or

-

when there are components mounted on a flex region of a rigid-flex board, and that flex layer extends from a mid-layer in the rigid section of the board.

The software needs to know which way components are oriented for each layer they are mounted on to know when the component primitives must be mirrored. This is configured automatically for the Top and Bottom Layers; for other layers, the setting is configured by the designer.

A component embedded on an internal signal layer (the component has been highlighted with blue outlines, the cavity with orange outlines).

A component embedded on an internal signal layer (the component has been highlighted with blue outlines, the cavity with orange outlines).

-

Component orientation is configured for a layer in the Orientation column of the Stackup tab of the Layer Stack Manager.

-

If the Orientation column is not visible, enable it by right-clicking on an existing heading in the layers grid and then selecting Select columns from the context menu.

-

The components on a layer can either point upwards (Top) or downwards (Bottom).

Documenting the Layer Stack

Object page: Layer Stack Table

Documentation is a key part of the design process and is particularly important for designs with a complex layer stack structure, such as a rigid-flex design. To support this, Altium Designer includes a Layer Stack Table, which is placed (Place » Layer Stack Table) and positioned alongside the board design in the workspace. The information in the layer stack table comes from the Layer Stack Manager.

Include a Layer Stack Table to document the design.

-

To place a Layer Stack Table, select Place » Layer Stack Table.

-

The Layer Stack Table details the following:

-

Layers used in the design

-

Material used for each layer

-

Thickness of each layer (and optionally the total board thickness).

-

The Dielectric Constant

-

The name of each stack and the layers used in that stack

-

Double-click anywhere on the placed table to open the Properties panel in Layer Stack Table mode.

-

The Layer Stack Table can also include an optional outline of the board showing how the various layer stacks are assigned to regions of the board. Use the Show Board Map option and slider bar to configure the map settings.

-

The Layer Stack Table is an intelligent design object that can be placed and updated as the design progresses. Double-click on the Layer Stack Table to edit it in the Properties panel.

-

An alternative approach to documenting the layer stack is to add a Draftsman document to the project and add a Layer Stack Table to it. Learn more about Draftsman.

Place the .Total_Thickness and the .Total_Thickness(<SubstackName>) special strings on a mechanical layer to include this information in your design documentation.

Including a Drill Table

Object page: Drill Table

Altium Designer includes an intelligent Drill Table that is placed like any other design object. The table can either display the drills required for all layer pairs (composite), or a specific layer pair. Place a drill table for each layer pair used in the design if you prefer separate drill information for each layer pair.

An alternative approach to documenting the layer stack is to add a Draftsman document to the project and add a Layer Stack Table to it. Learn more about Draftsman.

High Quality, Flexible Design Documentation

Main article: Draftsman

Altium Designer also provides a dedicated documentation editor - Draftsman. Draftsman has been built from the ground up as an environment for creating high-quality documentation that can include dimensions, notes, layers stack tables, and drill tables. Based on a dedicated file format and set of drawing tools, Draftsman provides an interactive approach to bringing together fabrication and assembly drawings with custom templates, annotations, dimensions, callouts, and notes.

Draftsman also supports more advanced drawing features including a Board Isometric View, a Board Detail View, and a Board Realistic View (3D view).

Place drawing views, objects and automated annotations on single or multi-page Draftsman documents.

Place drawing views, objects and automated annotations on single or multi-page Draftsman documents.

► Learn more about Draftsman

Layer Stackup Terminology

| Term |

Meaning |

| Blind Via |

A via that starts on a surface layer but does not continue all the way through the board. Typically a blind via descends 1 layer down to the next copper layer. |

| Buried Via |

A via that starts on one internal layer and ends on another internal layer but does not reach a surface copper layer. |

| Core |

A rigid laminate (often FR-4) with copper foil on both sides. |

| Double-Sided Board |

A board that has 2 copper layers, one on either side of an insulating core. All holes are through holes, i.e., they pass all the way from one side of the board to the other. |

| Fine Line Features and Clearances |

Tracks/clearances down to 100µm (0.1mm or 4mil) are considered standard for PCB fabrication today. The current technology limit available in component packaging is around 10µm. |

| High Density Interconnect (HDI) |

High Density Interconnect technology, a PCB that has a higher wiring density per unit area than a conventional PCB. This is achieved using fine-line features and clearances, microvias, buried vias, and sequential lamination technologies. This name is also used as an alternative to Sequential layer Build-Up (SBU). |

| Microvia |

Defined as a via that has a hole diameter smaller than 6 mils (150µm). Microvias can be photo imaged, mechanically drilled, or laser drilled. Laser-drilled microvias are an essential High Density Interconnect (HDI) technology, as they allow vias to be placed within a component pad and when used as part of a build-up fabrication process, allow signal layer transitions without the need for short tracks (referred to as via stubs), greatly reducing via-induced signal integrity issues. |

| Multilayer Board |

A board with multiple copper layers, ranging from 4 to over 30. A multilayer board can be fabricated in different ways:

-

As a set of thin, double-sided boards that are stacked (separated by prepreg) and laminated into a single structure under heat and pressure. In this type of multilayer board, the holes can be all the way through the board (through-hole), blind, or buried. Note that only specific layers can be mechanically drilled to create the buried vias, as they are simply through holes drilled in the thin double-sided boards before the lamination process.

-

Alternatively, a multilayer board is fabricated as described, and then additional layers are laminated onto either side. This approach is used when the design demands the use of microvias, embedded components, or rigid-flex technology.

|

| Prepreg |

A glass-fiber cloth impregnated with thermosetting epoxy (resin+hardener) which is only partially cured. |

| Sequential Lamination |

The name given to the technique of creating a multilayer PCB which includes mechanically drilled buried vias (drilled in the thin, double-sided boards prior to final lamination). |

| Sequential layer Build-Up (SBU) |

Starts as a core (double-sided or an insulator), with conductive and dielectric layers formed one after the other (using multiple pressure passes), on both sides of the board. This technology also allows blind vias to be created during the build-up process and discrete or formed components to be embedded. Also referred to as High Density Interconnect (HDI) technology. |

| Surface Laminar Circuit (SLC) |

Starts as a multilayer core, with build-up layers added on either side (typically 1 to 4). The common notation used to describe the finished board is Build-up copper layers + Core copper layers + Build-up copper layers. For example, 2+4+2 describes a board with a 4-layer core, with 2 layers laminated on either side (also written as 2-4-2). This technology allows blind vias to be created during the build-up process and discrete or formed components to be embedded. |