Interactively Routing with Controlled Impedances on a PCB in Altium Designer

디바이스 스위칭 속도가 증가함에 따라 임피던스 제어 라우팅은 디지털 설계자에게 뜨거운 주제가 되었습니다. 이 문서에서는 신호 무결성 분석 엔진을 사용하여 부품 임피던스와 PCB 에디터의 임피던스 제어 라우팅 기능을 일치시키는 방법을 소개합니다.

엔지니어링 업계에는 디지털 설계에 종사하는 전자 엔지니어는 신호 무결성 문제를 겪어본 사람과 앞으로 겪게 될 사람, 두 종류만 있다는 말이 있습니다. 불과 몇 년 전까지만 해도 신호 무결성이라는 용어는 전문가를 위한 것이었고, 고속 설계에서만 다루면 되었습니다. 그러나 이러한 고속 설계에서 디바이스 스위칭 속도는 더 이상 특별한 것이 아니라 빠르게 표준이 되고 있습니다. 집적 회로 기술이 발전함에 따라 트랜지스터의 크기가 작아지면서 스위칭 속도가 빨라지고 있습니다. 디지털 신호의 무결성에 영향을 미치는 것은 바로 이 스위칭 속도입니다.

다행히도 좋은 설계 원칙을 따르고 임피던스 제어 보드로 설계를 구현하면 많은 잠재적인 신호 무결성 문제를 피할 수 있습니다. 이를 위해서는 잠재적인 링잉 및 반사 문제가 있는 네트를 감지하는 분석 도구와 올바른 라우팅 임피던스를 달성할 수 있는 보드 설계 도구 등 특정 설계 도구 기능이 필요합니다. Altium Designer의 PCB 에디터에는 이러한 기능이 있습니다.

이 페이지에서는 신호 무결성 문제의 원인과 보드에 이러한 문제가 발생할 가능성이 있는지 이해하는 데 도움이 됩니다. 또한 잠재적인 SI 문제를 최소화하기 위해 사용해야 하는 두 가지 설계 접근 방식인 부품 임피던스 일치 및 임피던스 제어 라우팅에 대해서도 설명합니다.

라우팅이 회로의 일부가 되는 경우

디바이스 스위칭 속도가 증가함에 따라 인쇄 회로 기판 설계자와 제작자의 요구 사항도 증가하고 있습니다. 신호 스위칭 에지의 길이가 이를 전달하는 PCB 트레이스의 길이보다 짧아지면 트레이스는 회로의 일부로 취급되어야 합니다. 이 트레이스에는 임피던스가 있는데, 이를

이러한 추가 회로 요소의 영향을 관리하는 가장 좋은 방법은 특성 임피던스가 길이에 걸쳐 일정하도록 트레이스 라우팅을 설계하는 것입니다

트레이스 라우팅의 임피던스는 에 의해 정의됩니다:

-

Cross-sectional area of the trace - 에칭 과정에서 생성된 트레이스 에지의 폭, 높이(구리 두께) 및 경사로부터 결정됩니다. -

Distance from the trace to the reference plane(s) - 신호 에너지의 복귀 경로는 신호의 경로만큼이나 중요합니다. 이 복귀 경로는 인접한 기준 평면의 신호 경로를 따릅니다. -

Properties of the surrounding materials - 신호의 에너지는 트레이스의 구리 내에 포함되지 않으며, 스킨 효과로 인해 트레이스 주변의 유전체 물질을 따라 이동합니다. 유전체 재료의 유전율은 유전체가 해당 에너지의 흐름에 얼마나 영향을 미치는지를 측정합니다.

Simbeor 임피던스 계산기는 지정된 임피던스를 달성하는 데 필요한 폭을 계산합니다.

임피던스 제어 라우팅이 필요한가요?

임피던스 제어 라우팅이 필요한가요?

이상적인 상황에서는 부품 출력 핀에서 나오는 모든 에너지가 PCB의 연결된 트랙으로 결합되어 PCB 라우팅을 통해 반대쪽 끝의 부하 입력 핀으로 흐르고 해당 부하에 흡수됩니다. 모든 에너지가 부하에 흡수되지 않으면 남은 에너지는 PCB 라우팅으로 다시 반사되어 소스 출력 핀으로 흘러갈 수 있습니다. 이렇게 반사된 에너지는 원래 신호와 상호 작용하여 (에너지의 극성에 따라) 더하거나 빼면서 링잉을 일으킬 수 있습니다. 링잉이 충분히 크면 신호의 무결성에 영향을 미쳐 예측할 수 없는 잘못된 회로 동작이 발생할 수 있습니다.

그렇다면 이런 일이 발생할 수 있는지 어떻게 알 수 있을까요? 신호가 부하 핀에 도달하기 전에 소스 핀이 에지 전환을 완료할 수 있다면 반사 에너지로 인해 설계가 영향을 받을 수 있는 조건이 존재합니다. SI 문제가 발생할 가능성이 있는지 판단하는 데 사용되는 일반적인 경험 법칙은 "1/3 상승 시간" 규칙입니다. 이 규칙에 따르면 트레이스가 상승 시간의 1/3보다 길면 반사(링잉)가 발생할 수 있습니다. 소스 핀의 상승 시간이 1 nSec인 경우, 0.33 nSec(FR4의 경우 약 2인치)보다 긴 경로는 신호 무결성 문제가 발생할 수 있는 전송 라인으로 간주해야 합니다. 장치에 이러한 종류의 상승 시간이 있고 이러한 길이의 라우팅이 있다는 것을 알고 있다면 PCB에 신호 무결성 문제가 발생할 수 있습니다.

임피던스는 어떻게 제어하나요?

소스와 부하 사이에서 에너지가 앞뒤로 반사되는 상황을 어떻게 피할 수 있을까요? 임피던스를 일치시킴으로써 이를 방지할 수 있습니다. 임피던스 매칭은 모든 에너지가 소스에서 라우팅으로, 그리고 라우팅에서 부하로 연결되도록 합니다. 임피던스와 관련하여 보드를 라우팅하는 것을 임피던스 제어 라우팅이라고 하며, 다른 말로 임피던스가 관리되는 보드를 임피던스 제어 PCB라고 합니다.

임피던스 매칭을 달성하는 데는 두 가지 요소가 있습니다. 첫 번째는 컴포넌트를 일치시키는 것이고, 두 번째는 필요한 임피던스를 제공하기 위해 보드를 라우팅하는 것입니다.

컴포넌트의 임피던스 매칭

라우팅만으로는 제어된 임피던스 PCB를 얻을 수 없습니다. 먼저 컴포넌트의 임피던스를 확인하고 필요한 경우 일치시켜야 합니다.

이상적으로는 설계 캡처 단계에서 잠재적인 신호 무결성 문제가 있을 수 있는 네트를 감지하여 보드 설계 프로세스가 시작되기 전에 추가 종단 컴포넌트를 포함할 수 있도록 하는 것이 좋습니다. 출력 핀은 임피던스가 낮고 입력 핀은 임피던스가 높기 때문에 임피던스 정합을 달성하려면 설계에 종단 컴포넌트를 추가해야 할 가능성이 높습니다.

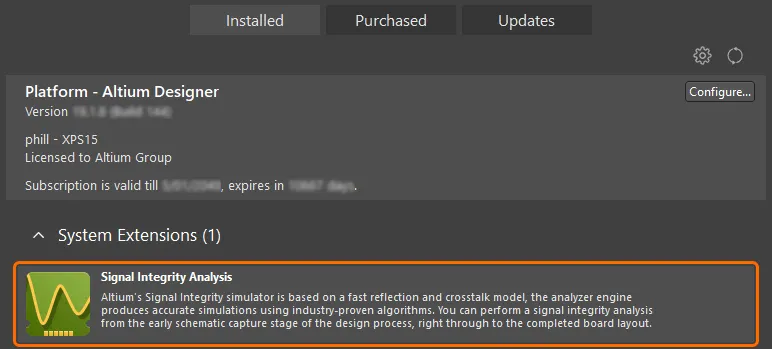

회로도 캡처 단계에서 설계에 대한 신호 무결성 분석을 수행할 수 있습니다. 회로도 캡처 단계에서

설계 디자인 분석하기

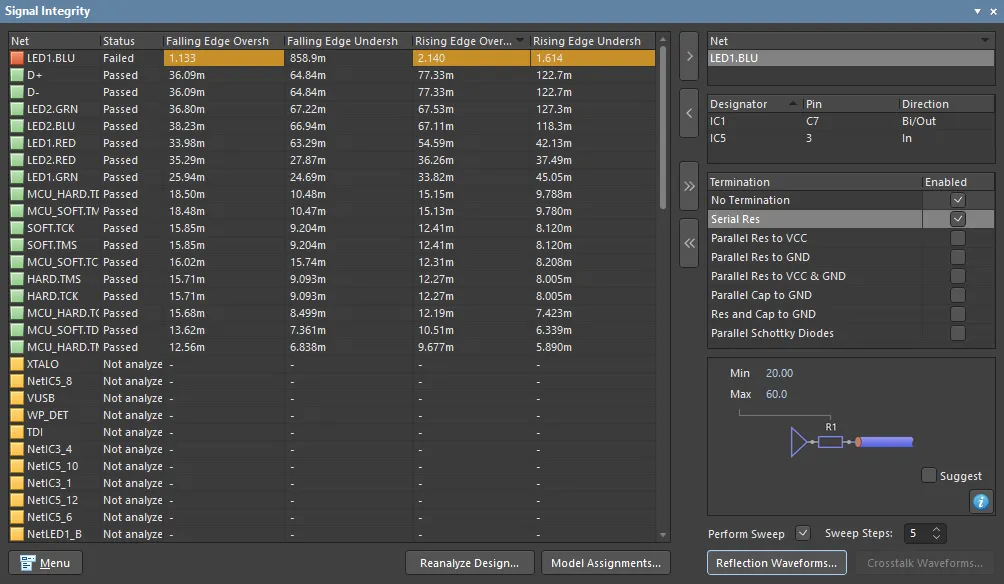

명령이 실행되면

설계 캡처 중에 잠재적인 신호 무결성 문제가 있는지 설계를 테스트합니다.

설계 캡처 중에 잠재적인 신호 무결성 문제가 있는지 설계를 테스트합니다.

패널에서 선택한 네트(또는 네트)에 대한 반사 분석을 수행할 수 있습니다. 왼쪽에는 설계의 모든 네트에 대한 분석 결과가 표시됩니다. 네트를 선택하고 ![]() 버튼(또는 네트 이름을 두 번 클릭)을 클릭하여 해당 네트를 패널 오른쪽의

버튼(또는 네트 이름을 두 번 클릭)을 클릭하여 해당 네트를 패널 오른쪽의

- 해당 망의 핀을 한 번 클릭하여 회로도에서 해당 핀으로 교차 프로브하거나 두 번 클릭하여 해당 핀에 할당된 모델을 확인하고 구성할 수 있습니다.

- 해당 네트에 대해 하나 이상의 이론적 종료 옵션을 활성화합니다.

- 네트에서 반사 분석을 수행하여 네트의 각 핀에서의 동작을 보여주는 파형 집합을 생성합니다.

이 패널에서 가능한 종단 구성 및 값을 실험할 수 있습니다. 참고로

결과 살펴보기

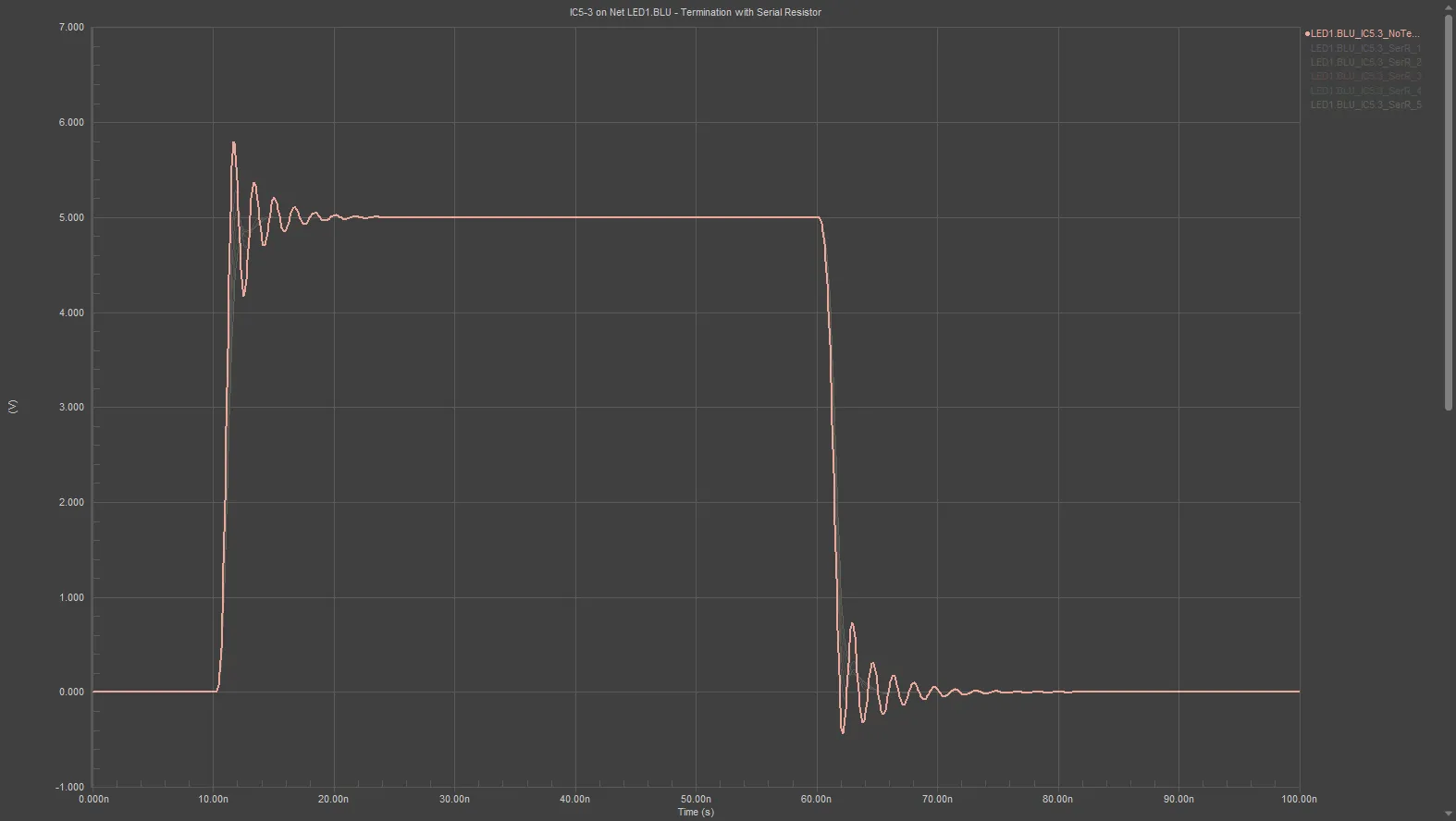

버튼을 클릭하면

파형 창에는 다음이 포함됩니다:

- 분석 중인 각 네트워크에 대한 차트, 창 하단의 탭을 클릭하여 차트 간에 전환할 수 있습니다.

- 각 차트에는 해당 네트워크의 각 핀에 대한 플롯이 포함되어 해당 핀에서의 신호 동작을 보여줍니다.

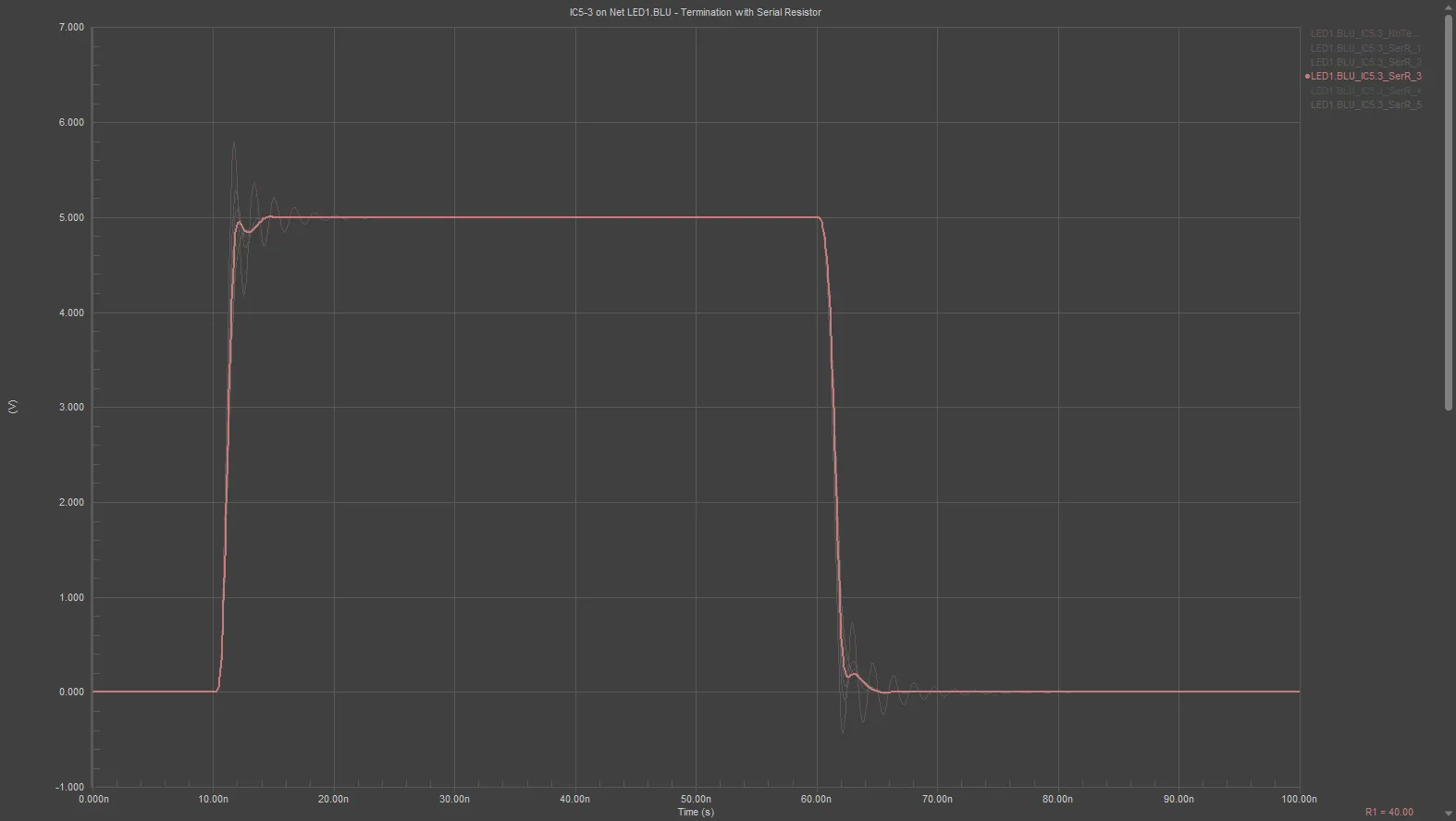

아래 이미지는 이전 패널 이미지에서 선택한 네트워크의 입력 핀에 대한 결과 그래프 두 개를 보여줍니다. 첫 번째 그래프는 종단이 없는 네트워크의 입력 핀이고, 두 번째 그래프는 종단이 없는 원래 네트워크에 대한 6개의 스윕, 그리고 소스 핀에 이론적 직렬 종단 저항이 포함된 5개의 스윕을 보여줍니다.

5번의 반사 분석 패스가 수행되었습니다(52060

왼쪽 그래프는 잠재적인 신호 무결성 문제가 있는 네트워크의 반사 분석을 보여주고, 오른쪽 그래프는 동일한 네트워크에 약 40옴의 이론적 직렬 종단 저항을 추가한 그래프입니다.

왼쪽 그래프는 잠재적인 신호 무결성 문제가 있는 네트워크의 반사 분석을 보여주고, 오른쪽 그래프는 동일한 네트워크에 약 40옴의 이론적 직렬 종단 저항을 추가한 그래프입니다.

라우팅 임피던스는 어떻게 결정되나요?

임피던스 제어 PCB를 구현하는 두 번째 단계는 트랙이 정의된 임피던스를 갖도록 보드를 라우팅하는 것입니다. 경로의 크기와 PCB 제작에 사용되는 재료의 특성을 포함하여 신호 라우팅의 임피던스에 영향을 미치는 여러 가지 요소가 있습니다.

PCB 에디터에는 Simberian의 Simbeor® 전자기 신호 무결성 엔진이 포함되어 있습니다. Simbeor의 모델 정확도는 3D 풀 웨이브 분석, 벤치마킹 및 실험적 검증을 위한 고급 알고리즘을 사용하여 검증됩니다. Simbeor 엔진은 모든 최신 보드 구조와 재료를 지원합니다.

Simbeor SFS

임피던스는 준정적 필드 솔버인 Simbeor SFS로 계산됩니다. Simbeor SFS는 수렴, 비교 및 측정을 통해 검증된 모멘트법(Method of Moments)을 기반으로 하는 고급 준정적 2D 필드 솔버입니다. 솔버는 유전체와 도체 경계를 메쉬화하고 해당 방정식을 풀어서 텔레그래프 방정식에 대한 주파수 의존적 RLGC 행렬을 구축합니다.

Simbeor SFS는 전파되는 파동의 준-TEM 특성으로 인해 PCB 인터커넥트의 임피던스, Delay 또는 감쇠를 평가하는 데 필요하지 않으므로 전체 파동 솔버가 아닙니다. 이러한 파동은 준정적 2D 필드 솔버로 추출한 RLGC 파라미터를 사용하여 정확하게 시뮬레이션할 수 있습니다.

Simbeor SFS 솔버의 고유한 특성은 도체 거칠기 모델을 지원한다는 점입니다. 단, 다층 도체 모델(도금)은 지원하지 않으며 모든 도체에 대해 거칠기가 공통적으로 적용된다는 점에 유의하세요. 솔버는 마이크로 스트립 라인에서 발생하는 고주파 분산(고주파에서 유전율이 높은 유전체에서 전계의 농도가 높아짐)을 솔루션에 포함하지 않기 때문에 준정적(quasi-static)입니다.

심베리안 전자기 신호 무결성 기술에대해 자세히 알아보기

지원되는 PCB 구조

다음 PCB 구조에 대해 임피던스를 계산할 수 있습니다:

- 마이크로 스트립

- 대칭 스트립 라인

- 비대칭 스트라이플라인

- Single 및 Differential 동일 평면 구조

- 서로 다른 유전체 특성을 가진 여러 개의 인접 유전체 레이어.

임피던스 제어 라우팅을 위한 PCB 구성하기

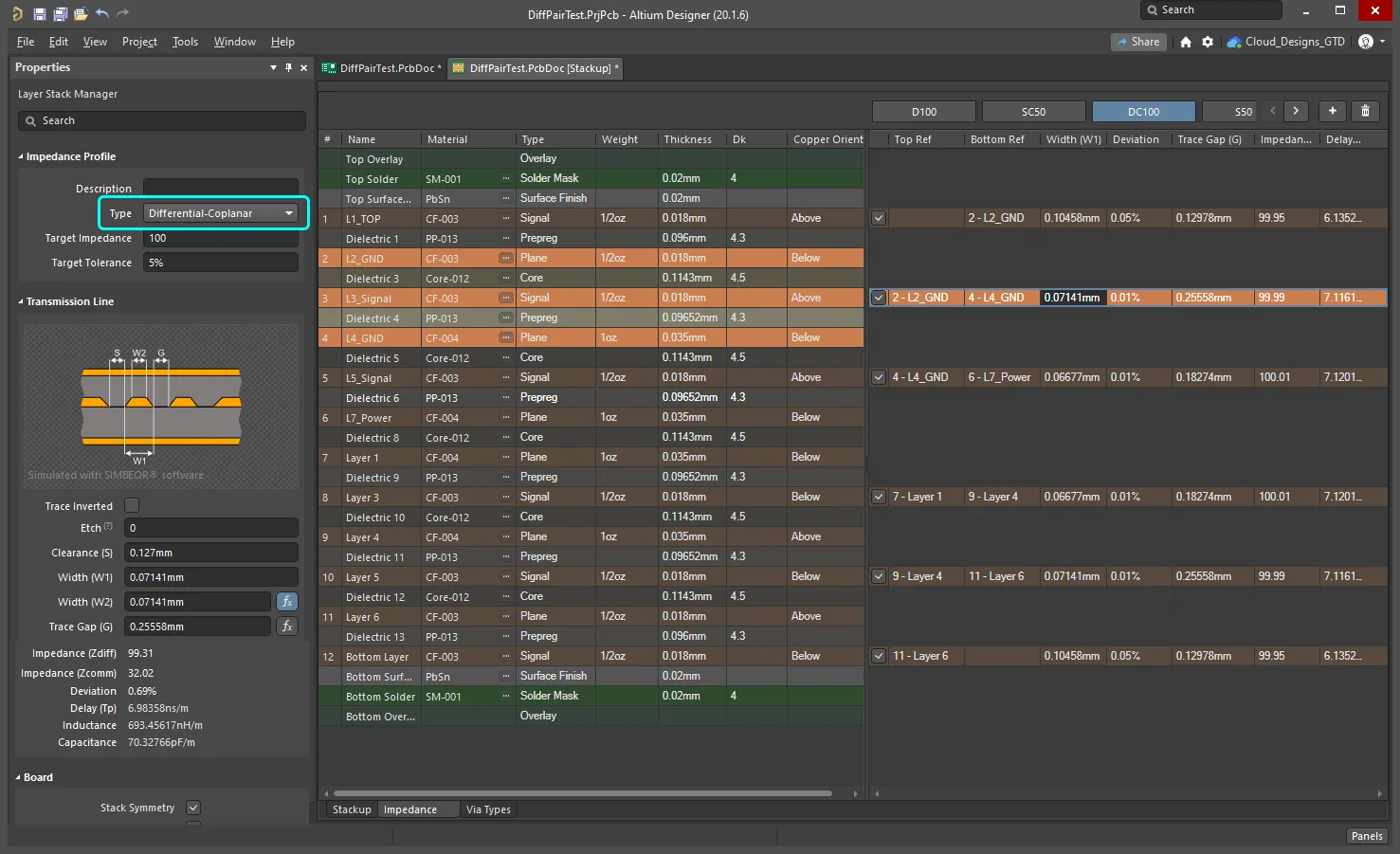

임피던스 제어 라우팅은 특정 임피던스를 전달하기 위해 경로의 치수와 보드 재료의 속성을 구성하는 것입니다. 이 작업은 PCB 에디터의

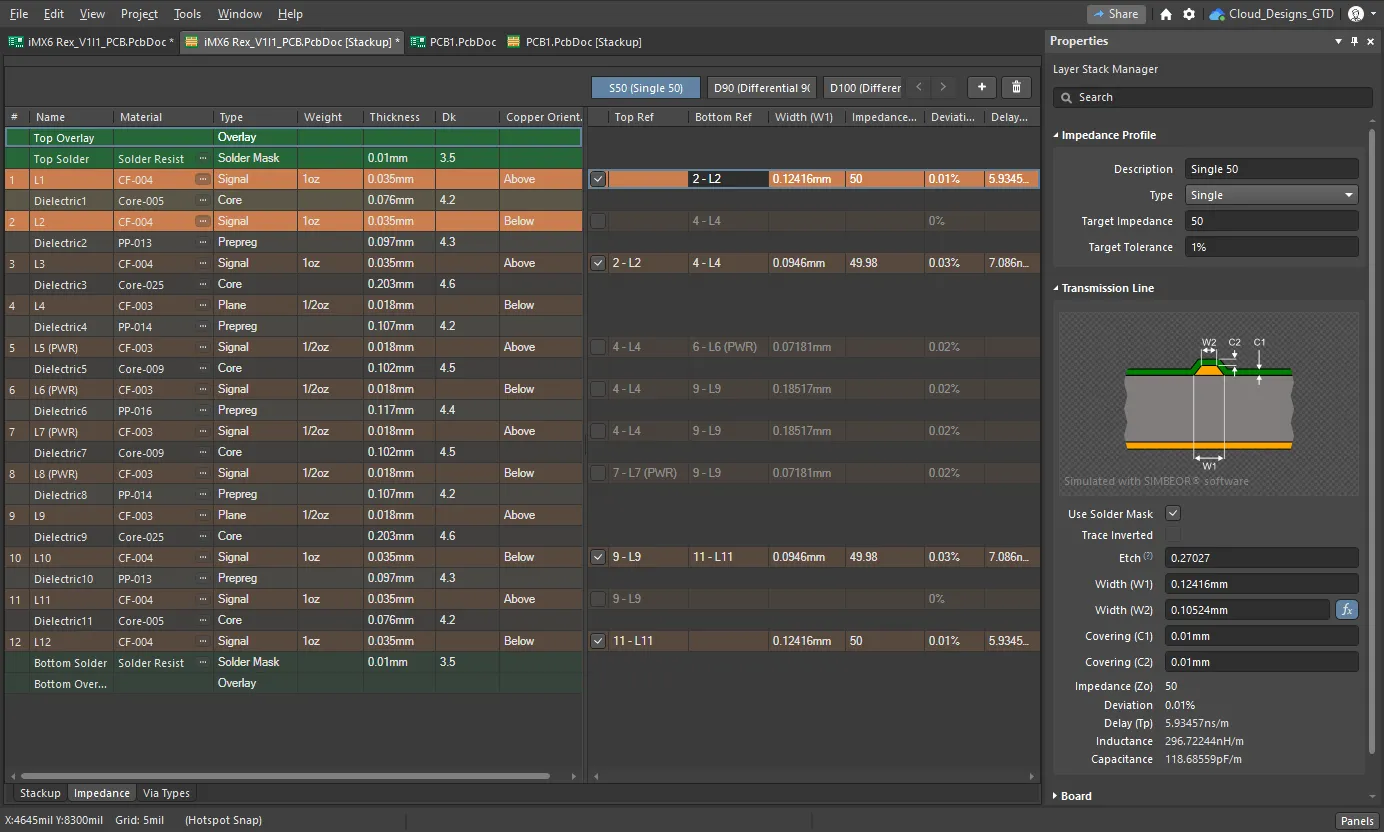

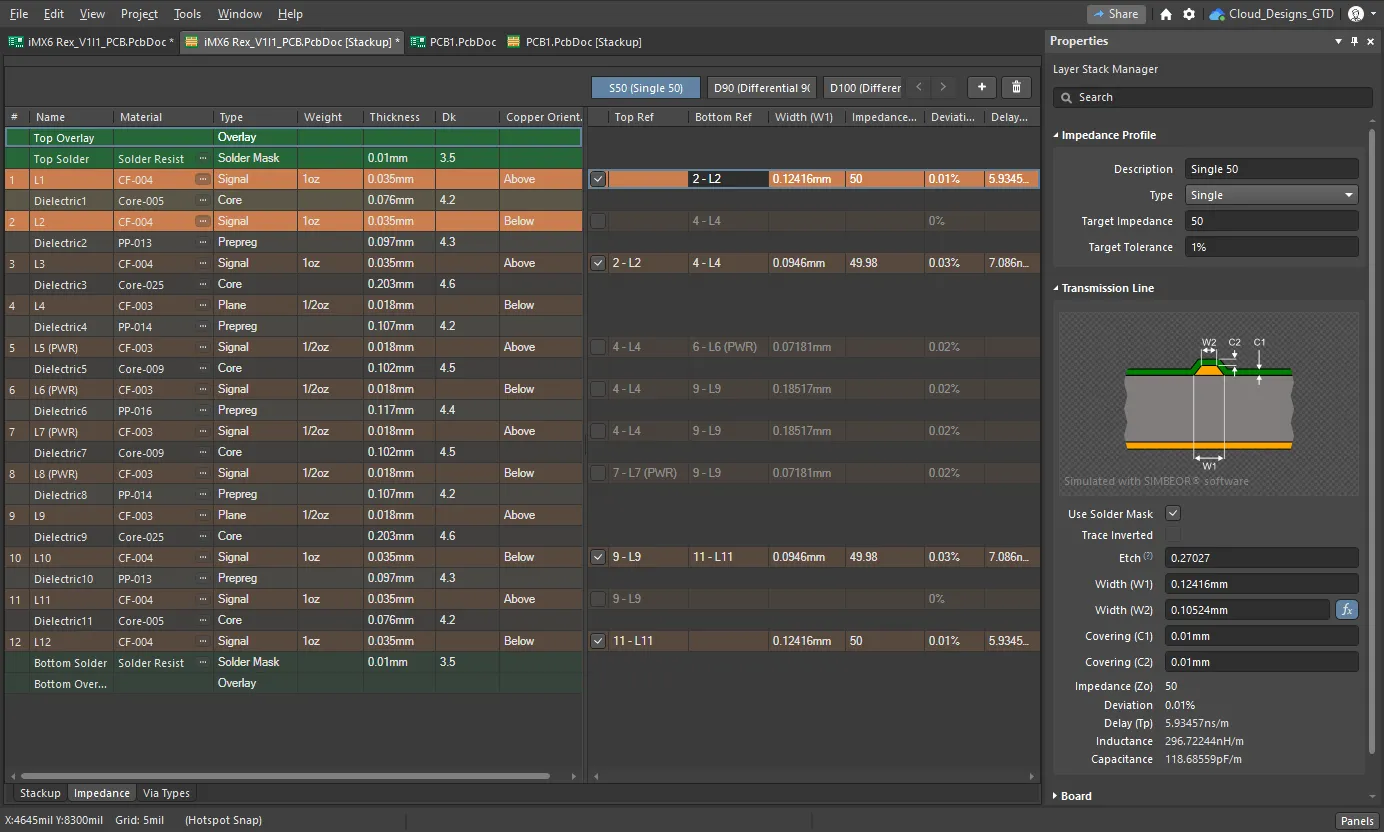

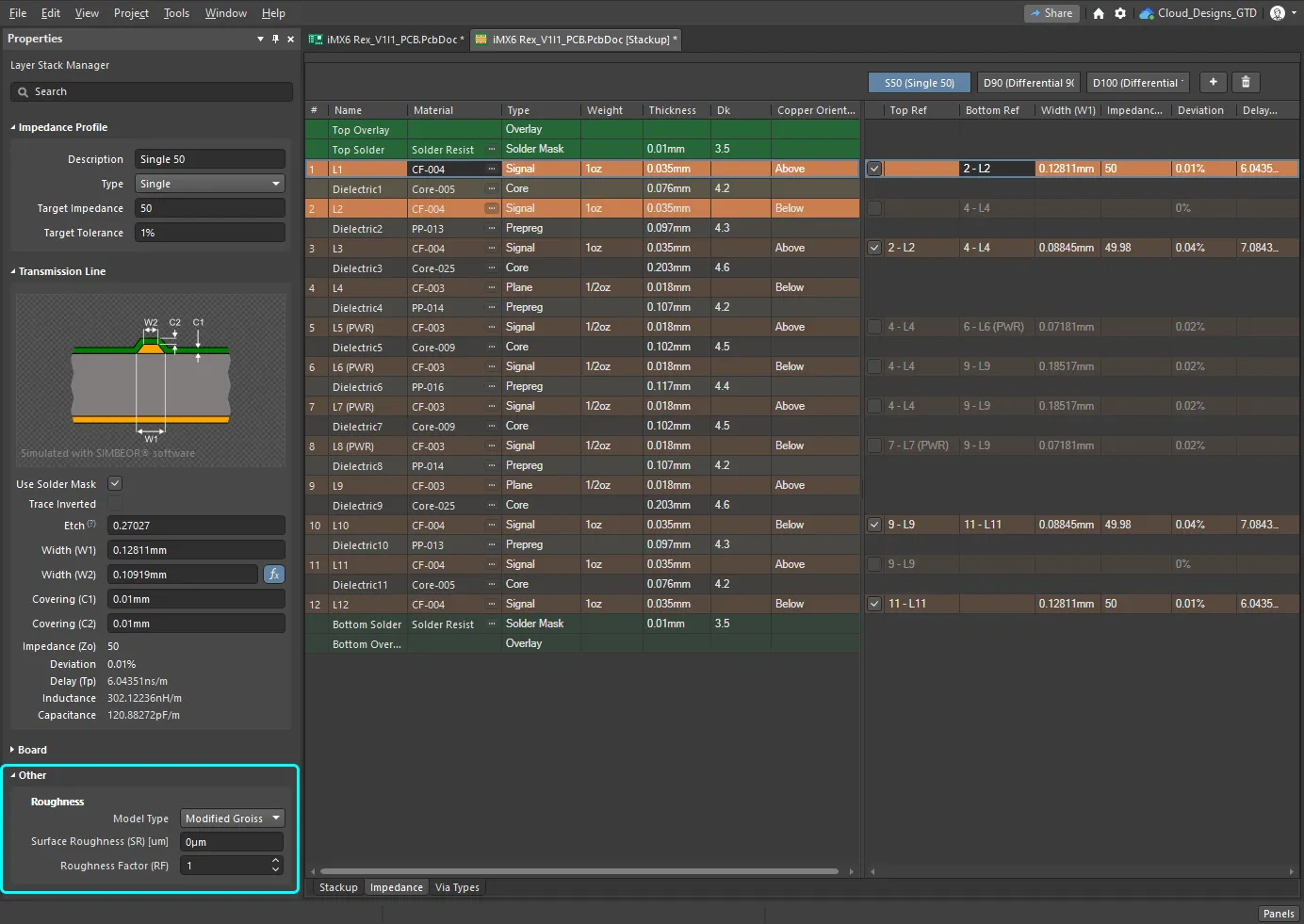

특정 임피던스를 전달하는 데 필요한 트레이스 폭은 임피던스 프로파일의 Impedance 탭에서 구성되는 Layer Stack Manager .임피던스 프로파일의 일부로 계산됩니다.

이것을 기반으로 합니다:

-

Impedance 탭에서 설정한

Target Impedance ,Target Tolerance 및Roughness 및, -

Stackup 탭에 정의된 머티리얼 설정 자료 설정을 포함합니다:

- 신호 레이어의 두께,

- 주변 유전체 층의 두께(기준면으로부터의 거리) 및

- 유전체 재료의 특성(유전율 Dk 및 손실 계수 Df).

이를 올바르게 구성하면 임피던스 계산기는 다음을 계산할 수 있는 충분한 정보를 제공합니다:

- 트레이스 폭

- 계산된 임피던스(Z)

- 공통 모드 임피던스(Zcomm)

- 임피던스 편차(Z 편차)

- 전파 Delay(Tp)

- 단위 길이당 인덕턴스(p.u.l.)

- 단위 길이당 커패시턴스(p.u.l.)

계산된 값은 패널의

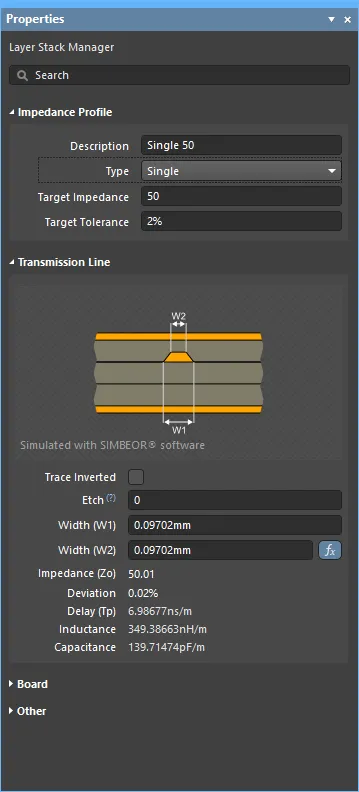

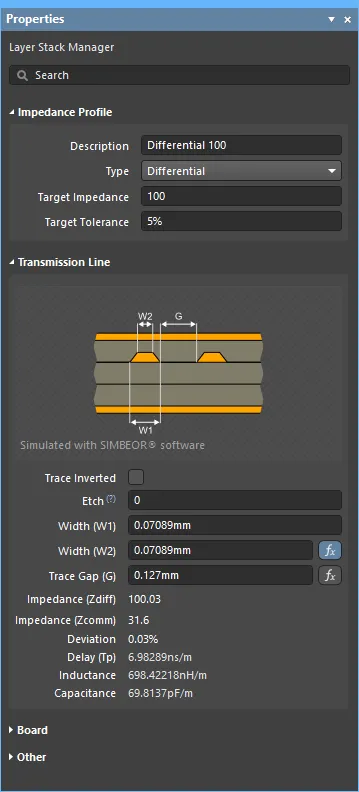

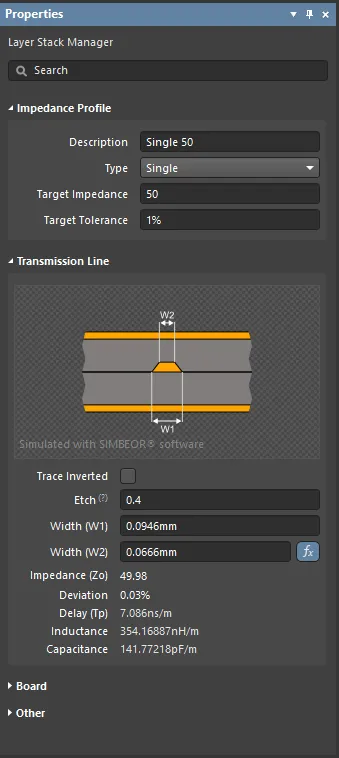

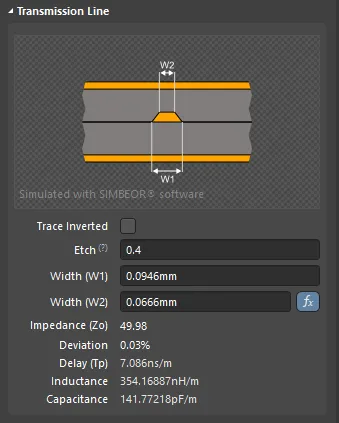

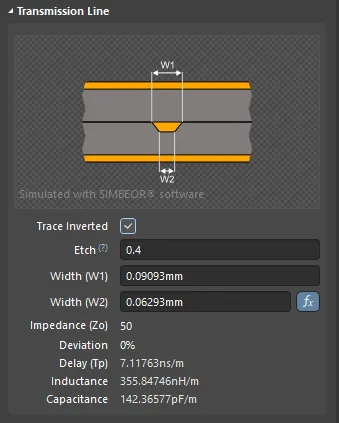

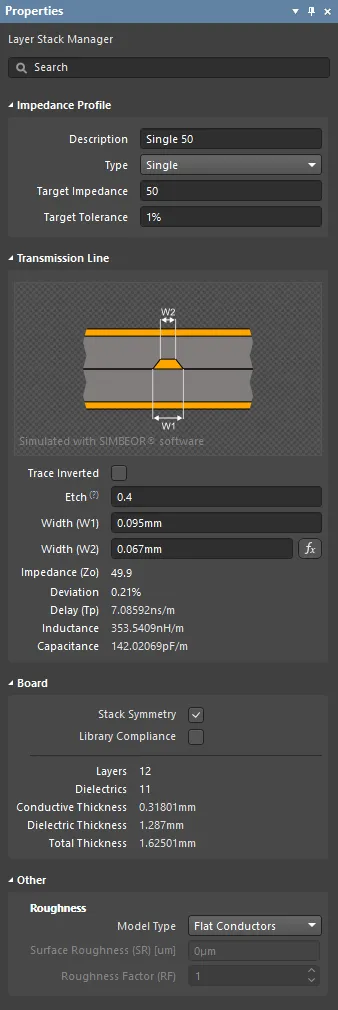

최상위 레이어에 라우팅된 단일 넷에 대해 정의된 50Ω 임피던스 프로파일. 이미지 위로 커서를 가져가면 레이어 L3에 대한 동일한 프로파일에 대한 설정이 표시됩니다(이미지 제공: FEDEVEL 오픈 소스, www.fedevel.com).

최상위 레이어에 라우팅된 단일 넷에 대해 정의된 50Ω 임피던스 프로파일. 이미지 위로 커서를 가져가면 레이어 L3에 대한 동일한 프로파일에 대한 설정이 표시됩니다(이미지 제공: FEDEVEL 오픈 소스, www.fedevel.com).

레이어 스택 구성하기

구리 및 유전체 제작 레이어는 구리 및 유전체 제작 레이어의

- 이 탭에서 레이어를 추가, 제거 및 구성할 수 있습니다. 리지드 플렉스 디자인의 경우 이 탭에서 레이어를 활성화 및 비활성화할 수도 있습니다.

-

현재 선택한 레이어의 속성은 그리드에서 직접 편집하거나

Properties 패널에서 직접 편집할 수 있습니다. 디자인 공간 하단의 버튼을 클릭하여 패널을 활성화합니다.

버튼을 클릭하여 패널을 활성화합니다.

-

레이어 격자를 마우스 오른쪽 버튼으로 클릭하거나

Edit » Add Layer 명령을 사용하여 레이어를 추가합니다. 구리 레이어를 추가하면 기존 인접 레이어도 구리 레이어인 경우 유전체 레이어도 추가됩니다. -

보드 섹션에서

Stack Symmetry 옵션이 보드 섹션에서 활성화된 경우Properties 패널의 보드 섹션에서 옵션을 활성화하면 레이어가 중간 유전체 레이어를 중심으로 일치하는 쌍으로 추가됩니다. -

레이어 재질은 선택된 재질 셀에 직접 입력하거나

Select Material 대화 상자에서 선택하거나 줄임표 버튼을 클릭하여 열 수 있습니다. -

구리 레이어에 표면 마감을 추가할 수 있습니다. 표면 마감을 추가하려면

Add Layer 하위 메뉴를 사용하여 현재 선택된 구리 레이어에Surface Finish 레이어를 추가한 다음 새 표면 마감 레이어의 줄임표 버튼을 클릭하여 마감 유형을 선택합니다. -

선택한 레이어는 오른쪽 클릭 또는

Edit 메뉴. -

레이어의

Board 영역에는Properties 패널의 영역에는Stack Symmetry 및Library Compliance . 이에 대한 자세한 내용은 아래에서 확인하세요. -

영역의

Board 영역은Properties 패널의 영역에는 현재 선택된 스택(또는 멀티 스택 리지드/플렉스 디자인의 경우 서브 스택)의 요약이 표시됩니다.

레이어 스택 고려 사항

임피던스 제어를 위한 기본 요건은 각 신호 경로 아래에 신호 리턴 경로를 포함시키는 것입니다. Simbeor SI 엔진은 평면 레이어와 폴리곤으로 덮인 신호 레이어를 모두 지원합니다. 이러한 리턴 경로 레이어는 보드 스택업을 통해 분산되어야 합니다. 이상적으로는 임피던스 제어 라우팅을 수행하는 각 신호 레이어에 하나 이상의 리턴 경로 레이어가 인접하도록 배치하는 것이 좋습니다. 인접한 리턴 경로 레이어는 신호 리턴 경로를 제공하며, 여기서 다루지 않는 이유로 해당 평면에서 분배되는 DC 전압에 관계없이 리턴 경로를 제공합니다.

평면을 통해 흐르는 리턴 경로 전류는 신호 레이어의 경로와 동일한 물리적 경로를 따라가려고 하므로 중요한 신호 라우팅 아래의 리턴 경로 레이어에 분할 또는 차단과 같은 불연속성을 도입하지 않도록 하는 것이 중요합니다.

신호 및 평면 레이어에 적합한 순서를 선택하는 것뿐만 아니라 각 레이어의 재질 속성도 정의해야 합니다:

- 구리 두께

- 유전체 두께

- 유전 상수

이러한 값과 라우팅 폭은 모두 최종 임피던스에 영향을 미칩니다. 필요한 임피던스를 달성하려면 이 모든 값을 조정하는 과정이 필요합니다. 가능한 구리 및 유전체 두께 값도 PCB 제작업체에서 제공하는 재료에 따라 제한될 수 있다는 점을 기억하세요.

가능한 레이어 스택업에대해 자세히 알아보기

임피던스 프로파일 정의하기

Simbeor 엔진은 PCB 에디터의

최상위 레이어에 라우팅된 개별 네트워크에 대해 정의된 50Ω 임피던스 프로파일입니다. 이미지 위로 커서를 가져가면 레이어 L3에 대한 동일한 프로필의 설정이 표시됩니다.

최상위 레이어에 라우팅된 개별 네트워크에 대해 정의된 50Ω 임피던스 프로파일입니다. 이미지 위로 커서를 가져가면 레이어 L3에 대한 동일한 프로필의 설정이 표시됩니다.

임피던스 프로필 생성 및 구성에 대한 참고 사항:

-

임피던스 프로필의

Layer Stack Manager 탭으로 전환합니다Impedance 탭으로 전환합니다. -

탭에서

버튼(또는 이미 정의된 프로필인 경우

버튼(또는 이미 정의된 프로필인 경우  버튼(또는 이미 프로필이 정의되어 있는 경우 버튼)을 클릭하여 새 프로필을 추가합니다.

버튼(또는 이미 프로필이 정의되어 있는 경우 버튼)을 클릭하여 새 프로필을 추가합니다.

-

필요한 임피던스 정의

Type ,Target Impedance 및Target Tolerance 를 정의합니다Properties 패널에서 정의합니다. 는 선택 사항이며Description 는 선택 사항이며, 임피던스 프로필 이름이 표시되는 모든 곳에 표시됩니다. -

레이어 그리드는 2개의 영역으로 나뉘며, 스택업의 레이어가 왼쪽에 표시되고 스택업의 각 신호 레이어에 대해 오른쪽의 임피던스 프로필 영역에 표시되는 레이어가 있습니다. 프로필 영역에서 레이어 확인란을 사용하여 해당 레이어에 대한 임피던스 계산을 활성화합니다. 위 이미지를 예로 들어 가장 왼쪽 열에 표시된 레이어 번호를 참조하여 레이어

L1L3L10L12 -

프로필 영역에서 활성화된 레이어를 클릭하면 선택한 신호 레이어의 임피던스를 계산하는 데 사용되는 레이어를 제외한 레이어 스택의 모든 레이어가 페이드됩니다(위 이미지와 같이). 임피던스 프로파일 영역의 상단 레퍼런스 및 하단 레퍼런스 열에서 해당 레이어의 레퍼런스 레이어를 편집합니다. 참조 레이어에는 다음 중 하나의 레이어

Type 또는PlaneSignal . 예를 들어, 위 이미지에서 스택업의 레이어L10Top Ref 로 설정된9-L9PlaneBottom Re f는11-L11Signal 레이어로 설정합니다. 소프트웨어는 신호 레이어가 참조 평면으로 사용되는 경우 전원 또는 접지망에 연결된 연속적인 구리 평면이 포함되어 있다고 가정합니다. -

라우팅을 전달할 서로 레이어에 대해

Impedance Profile 체크박스를 활성화하여 이 임피던스에서 라우팅을 수행할 다른 레이어에 대해 참조 평면을 구성합니다. 위 이미지 위로 커서를 가져가면 레이어 L3에 대한 S50 임피던스 프로파일이 표시됩니다. - 계산된 라우팅 트레이스 폭이 정렬할 수 없는 값인 경우 폭과 간격 설정을 조정할 수 있습니다.

너비 및 간격 설정 조정하기

소프트웨어는 목표 임피던스와 허용 오차에서 트레이스 폭을 계산합니다. 계산된 트레이스 폭이 주문할 수 없는 값(예: 0.0683mm)이 되는 경우가 드물지 않습니다. 제작업체는 사용 가능한 재료 두께와 트레이스 폭에 대해 달성할 수 있는 정밀도를 조언합니다. 그런 다음 원하는 값에서 시작한 다음 치수를 사용 가능한 값으로 조정할 때 계산된 임피던스 값에 미치는 영향을 테스트하는 프로세스가 됩니다.

이러한 설정 테스트 및 조정 과정을 지원하기 위해 임피던스 계산기는 순방향 및 역방향 임피던스 계산을 지원합니다. 기본 모드는 순방향입니다(임피던스를 입력하면 소프트웨어가 폭을 계산합니다). 아이콘은 ![]() 아이콘은 계산된 변수를 나타냅니다.

아이콘은 계산된 변수를 나타냅니다.

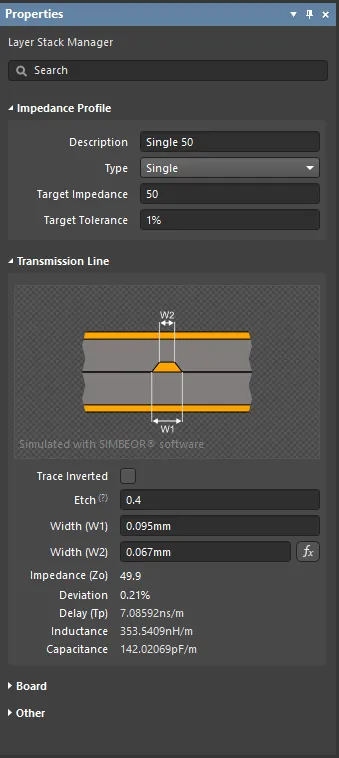

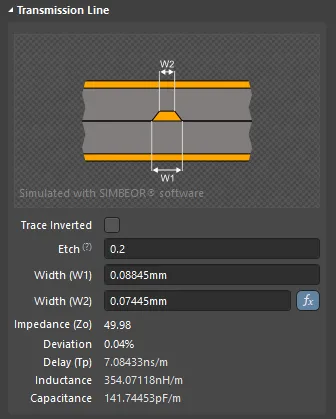

목표 임피던스가 50Ω인 경우 순방향으로 계산된 폭(W1)은 94.6µm입니다. 오른쪽 이미지는 폭(W1)을 95µm로 설정했을 때의 역방향 계산을 보여줍니다.

목표 임피던스가 50Ω인 경우 순방향으로 계산된 폭(W1)은 94.6µm입니다. 오른쪽 이미지는 폭(W1)을 95µm로 설정했을 때의 역방향 계산을 보여줍니다.

계산을 반대로 하고 선택한 레이어에 대한 다른 트레이스 폭을 탐색하려면 새로운 ![]() 버튼을 클릭하여 계산기를 정방향 계산 모드로 되돌립니다. 에 새 값을 입력하면

버튼을 클릭하여 계산기를 정방향 계산 모드로 되돌립니다. 에 새 값을 입력하면

차동 쌍 전송 라인 결과를 탐색하려면 계산된 변수를 지정합니다 ![]() 버튼을 클릭합니다. 다른 변수를 편집하여

버튼을 클릭합니다. 다른 변수를 편집하여

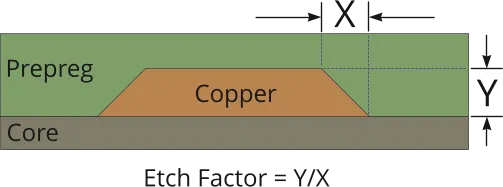

에칭 계수

PCB의 신호 트레이스는 불필요한 구리를 에칭하여 제작됩니다. 에칭액이 표면의 구리를 에칭하기 시작하기 때문에 이 구리는 에칭액과 접촉하는 시간이 길어집니다. 그 결과 아래 이미지와 같이 완성된 트레이스의 가장자리가 경사져 완성된 트레이스의 단면적이 줄어듭니다.

에칭 중 손실되는 트레이스 에지 구리 면적(양쪽 가장자리) = = X * Y

기울기의 양을 에칭 계수라고 하며, 여기서 에칭 계수는 다음과 같습니다:

Etch Factor = Y/X

만약 Y = XEtch Factor = 1

에 표시된 이미지를 참조하여

위에 커서를 올리면 공식이 표시됩니다.

위에 커서를 올리면 공식이 표시됩니다.

에치 팩터의 표준 정의는 다음과 같은 비율로 지정하는 것입니다 trace thickness / amount of over-etching

= T/[0.5(W1-W2)]

이 접근 방식의 단점은 오버 에칭을 지정하지 않으려면(트레이스 가장자리가 수직임을 의미) 에칭 계수 값으로 inf0

[0.5(W1-W2)]/T

구리 방향

에칭 계수에 영향을 미치는 또 다른 제조 세부 사항은 구리의 방향입니다. PCB 트레이스는 유전체 기판 위에 적층된 연속 구리 시트에서 원하지 않는 구리를 에칭하여 형성됩니다. 구리 방향은 구리가 해당 기판에서 돌출되는 방향을 정의합니다. 구리가 위 또는 아래에서 에칭되는 방향이라고 생각할 수도 있습니다.

트레이스 반전 확인란을 클릭하여 구리 방향을 위쪽에서 아래쪽으로 전환합니다.

트레이스 반전 확인란을 클릭하여 구리 방향을 위쪽에서 아래쪽으로 전환합니다.

도체 표면 거칠기(Roughness)

인쇄 회로 기판의 각 구리 층 표면에는 어느 정도의 거칠기가 있습니다. PCB 제조 과정에서 구리 층의 표면은 구리 층과 유전체 층 사이의 접착력을 향상시키기 위해 거칠기를 증가시키는 처리를 거칩니다. 이러한 표면 거칠기는 스위칭 속도 10GB/s 이상에서 도체 임피던스에 중요한 영향을 미칩니다. 광범위한 연구와 분석을 통해 업계 전문가들은 표면 거칠기를 다음에서 파생된 거칠기 보정 계수로 모델링할 수 있다는 결론을 내렸습니다

거칠기:

-

Model Type - 표면 거칠기의 영향을 계산할 때 선호하는 모델입니다(다양한 모델에 대한 자세한 내용은 아래 문서 참조). 서브스택의 모든 구리 레이어에 적용됩니다. -

Surface Roughness - 표면 거칠기 값(제작업체에서 제공). 0~10µm 사이의 값을 입력하며 기본값은 0.1µm입니다 -

Roughness Factor - 거칠기 효과로 인해 예상되는 도체 손실의 최대 증가를 나타냅니다. 1에서 100 사이의 값을 입력합니다(기본값은 2).

추가 읽을 자료

-

인터커넥트에서 신호 손실 및 분산에 대한 도체 거칠기의 영향을 분석하는 실용적인 방법론: Y. Shlepnev, C. Nwachukwu,

DesignCon2012 . -

인터커넥트 도체 표면 거칠기 모델링에 대한 통합 접근 방식: Y. Shlepnev, 2017 IEEE 제26회 전자 패키징 및 시스템의 전기적 성능 컨퍼런스(EPEPS2017)

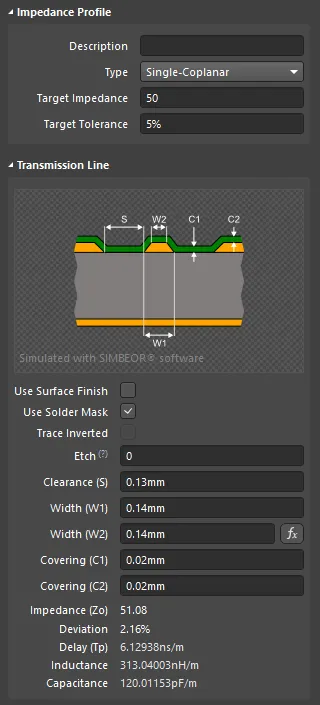

동일 평면 전송선 구조 지원

의 임피던스 계산기는 Single-CoplanarDifferential-Coplanar

동일 평면 구조로 작업하기:

-

표준 Single 및 Differential 임피던스와 마찬가지로 각 변수의 값은 사용자가 정의한 값에 따라 자동으로 계산됩니다

Target Impedance 및Target Tolerance 및 보드 레이어의 물리적 속성을 기반으로 각 변수의 값이 자동으로 계산됩니다. 이렇게 자동으로 계산된 값은 편집 상자에 새 값을 입력하여 조정할 수 있습니다Layer Stack Manager 모드의Properties 패널의 편집 상자에 새 값을 입력하여 조정할 수 있습니다. -

동일 평면 구조로 라우팅하려는 신호망을 대상으로 지정하려면 라우팅 폭 (또는 차동 쌍 라우팅) 디자인 규칙을 구성하고

Use Impedance Profile 옵션을 활성화하고 필요한 동일 평면 임피던스 프로파일을 선택합니다. -

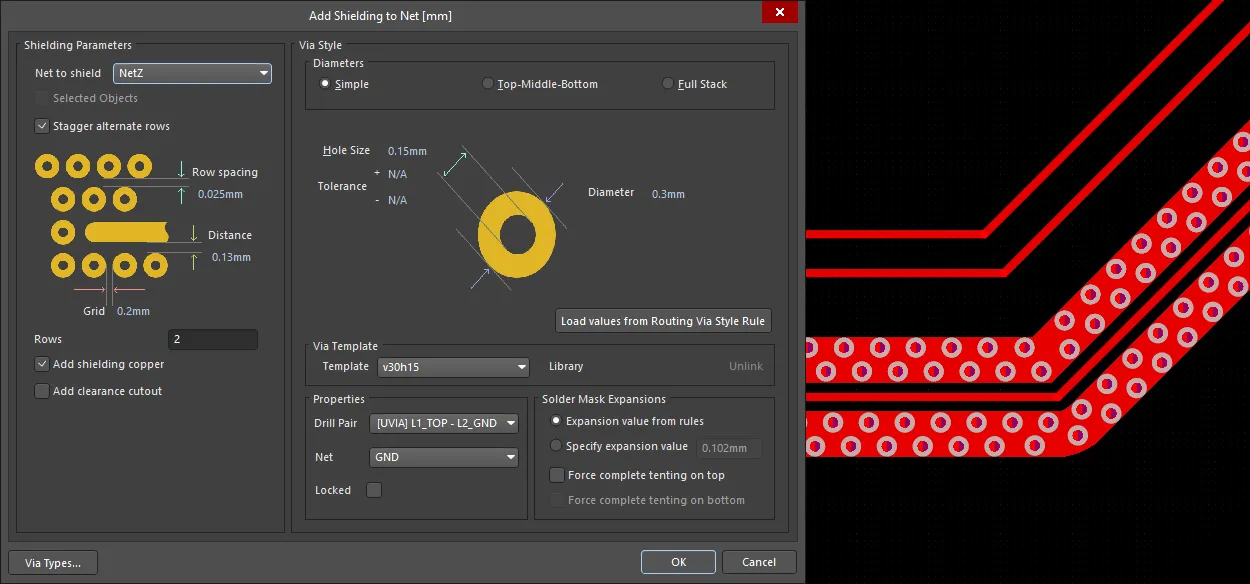

동일 평면 구조는 신호 경로의 양쪽에 기준 평면이 필요하며, 이는 사용자가 배치한 다각형으로 만들거나 스티칭 비아를 추가하는 경우

Add Shielding to Net 명령(아래 자세한 정보)으로 만들 수 있습니다. 다각형을 배치하는 경우, 이 다각형과 신호 경로 사이의 간격은 심비어 임포머에 의해 결정되는Clearance (S) 값에 의해 결정됩니다('Simbeor 임피던스 계산기'에 표시된Properties 패널에 표시됨, 위와 아래 이미지에 표시됨). 클리어런스 설계 규칙을 구성하여 기준 다각형과 신호 경로 사이의 간격을 제어합니다(이미지 표시). -

동일 평면 구조가 접지된 경우 신호 트레이스의 각 측면을 따라 비아 펜스를 포함하는 것이 일반적입니다. 이 작업을 수행하려면 PCB 편집기에서

Tools » Via Stitching/Shielding » Add Shielding to Net 명령을 사용하여 이 작업을 수행합니다. 비아를 배치할 뿐만 아니라, 이 명령은Add shielding copper 옵션을 활성화하면 아래 오른쪽 이미지와 같이 비아 펜스를 덮도록 신호 라우팅 주위에 다각형을 배치할 수도 있습니다.

비아차폐에 대해 자세히 알아보기

임피던스 계산기는 신호 속성 및 간격을 결정하고(첫 번째 이미지), 비아 차폐 거리 설정에서 해당 간격을 사용합니다.

임피던스 계산기는 신호 속성 및 간격을 결정하고(첫 번째 이미지), 비아 차폐 거리 설정에서 해당 간격을 사용합니다.

레이어 재질 선택

임피던스 제어 설계에서는 레이어 스택업에 사용되는 재질을 선택하는 것이 매우 중요합니다.

예를 들어, PCB 제작에 가장 일반적으로 사용되는 재료는 유리 섬유(유리 섬유) 강화 에폭시 수지로, 각 면에 구리 호일이 접착되어 있습니다. 유리 섬유 직물의 짜임새는 유전 상수 Dk(유전율) 및 손실 탄젠트 Df의 값과 일관성에 영향을 미칩니다. 직조된 유리 섬유 직물을 둘러싸고 있는 것은 레진으로, 사용된 레진의 비율도 재료의 성능에 중요한 영향을 미칩니다.

사용 가능한 유리 섬유 직조는 매우 다양합니다. PCB 제조에 사용되는 유리 섬유 기반 재료의 예측 가능성과 성능을 보장하기 위해 IPC에는 직조 표준이 있습니다:

IPC standard IPC-4412B: Specification for Finished Fabric Woven from "E" Glass for Printed Boards

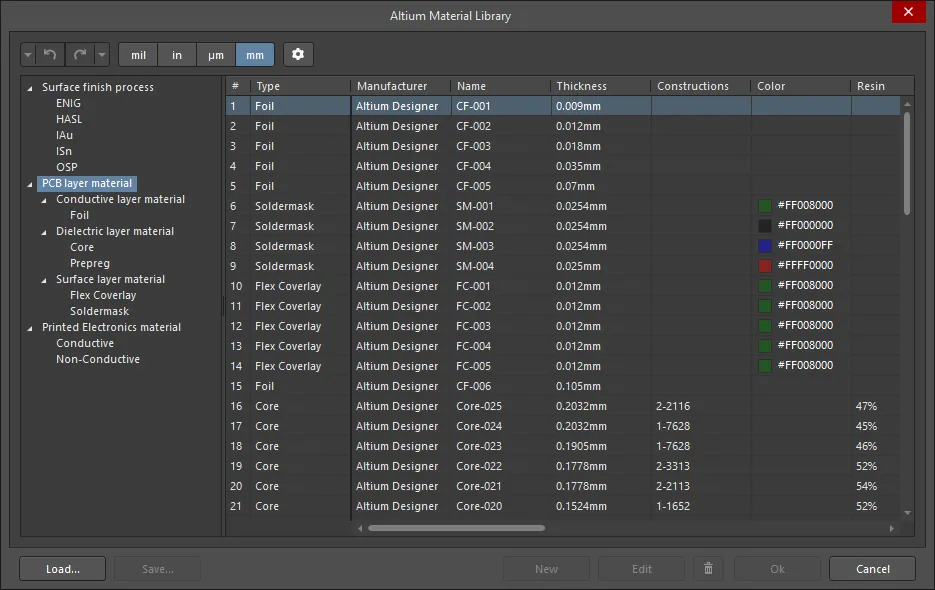

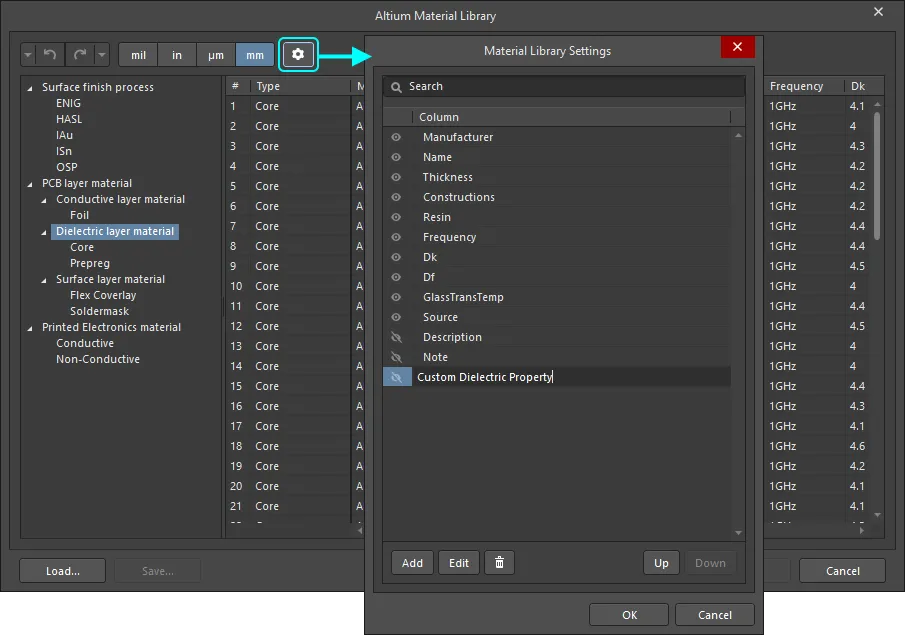

머티리얼 라이브러리

디자이너는 머티리얼 속성을 직접 편집하거나

전체 라이브러리는 Altium 머티리얼 라이브러리 대화상자 (

자료는 사용 범주로 구성되어 있으며 대화 상자 왼쪽의 트리 구조를 통해 액세스할 수 있습니다. 이 수준 아래에서 각 사용 범주는 다음과 같은 기능적 범주로 나뉩니다

자료 추가, 저장 및 로드

트리에서 특정 소재 카테고리를 선택하면 라이브러리에 새 소재를 추가할 수 있습니다. 외부 소재 라이브러리에 정의된 소재를 로드할 수 있으며(

머티리얼에 사용자 정의 속성 추가하기

사용자 정의 프로퍼티는 라이브러리에 자세히 설명된 머티리얼(기본 및 사용자 정의 머티리얼)에 추가할 수 있습니다. 커스텀 프로퍼티를 추가하려면 먼저 왼쪽 트리에서 올바른 노드를 선택하여 추가할 머티리얼을 정의한 다음 ![]() 버튼을 클릭하여

버튼을 클릭하여

그런 다음 대화 상자에서 선택한 머티리얼에 필요한 값을 추가할 수 있습니다

속성 패널

레이어 스택 문서의

-

Impedance Profile -

Description - 의미 있는 설명을 입력합니다. 이 필드는 선택 사항이며 임피던스 프로파일 이름이 표시되는 모든 곳에 표시됩니다. -

Type - 드롭다운을 사용하여 임피던스 유형을 선택합니다. 선택 가능한 항목은Single ,Differential ,Single-Coplanar 및Differential-Coplanar .

-

-

Target Impedance - 원하는 임피던스를 입력합니다. -

Target Tolerance - 달성하려는 허용 오차를 입력합니다. 제작업체와 상의하여 제작업체가 제공할 수 있는 현실적인 허용 오차 값을 찾아야 합니다. -

Transmission Line -

Trace inverted - 패널에 표시된 대로 이 옵션을 활성화하여 추적을 반전합니다Properties 패널에 표시된 대로 이 옵션을 활성화합니다. 이 옵션은 트레이스를 반전할 때 표시되는Copper Orientation 탭이 활성화되었을 때 표시되는Stackup 탭이 활성화되었을 때 표시되는 옵션과 동일하며 구리가 코어에 라미네이트되는 방향을 정의합니다. 구리 방향은 구리가 해당 기판에서 돌출되는 방향을 정의합니다. 구리가 위 또는 아래에서 에칭되는 방향이라고 생각할 수도 있습니다. -

Etch - 에칭 계수는= T/[(W1-W2)/2]Etch 에 대한 정보는 보드 제작업체에 문의하세요.

-

-

Width (W1) / (W2) - W1은 라우팅하는 트레이스의 너비이고, W2는 에칭된 후 해당 트레이스의 상단 표면의 너비이며, 여기에Etch 계수가 적용됩니다. 트레이스 너비에 사용할 수 있는 정방향/역방향 계산 기능이 있습니다. 기본값은 입력한 값을 기준으로 너비를 계산하는 것입니다Target Impedance (순방향 계산)을 기준으로 너비를 계산하는 것입니다. 이 너비는 5.978과 같이 제작자가 제공할 수 없는 값일 수 있으며, 제작자는 6.0과 같이 보다 합리적인 값을 원할 것입니다. 6.0을 입력할 수 있습니다Width 필드에 6.0을 입력하고 키보드에서Enter 를 눌러 계산된 값을 다시 계산할 수 있습니다(Impedance ,Deviation 등). 버튼이 회색으로 바뀌고(비활성화됨) 이제 역방향 계산 모드가 됩니다. 버튼을 클릭하여 활성화하면 다시 정방향 모드가 되고

버튼이 회색으로 바뀌고(비활성화됨) 이제 역방향 계산 모드가 됩니다. 버튼을 클릭하여 활성화하면 다시 정방향 모드가 되고 Width (W1) 가 계산된 값으로 되돌아갑니다. 이 기능을 사용하면 사실적인 제작 가능한 너비 옵션을 탐색할 수 있습니다. W2 값을 수동으로 입력하면 에칭 계수가 그에 맞게 업데이트됩니다. -

Impedance - 소프트웨어는 기판 제작에 사용된 재료(구리, 코어 및 프리프레그)의 특성과 트레이스의 단면적(트레이스의 폭, 두께 및 에칭 계수에 의해 결정됨)을 기반으로 임피던스를 계산합니다. -

Deviation - 이는 원하는 값(목표 임피던스)과 실제 값(계산된 임피던스)의 차이를 측정한 값입니다. 소프트웨어는 기판을 만드는 데 사용된 재료(구리, 코어 및 프리프레그)의 특성과 트레이스의 단면적(트레이스의 폭, 두께 및 에칭 계수에 의해 결정됨)을 기반으로 임피던스 편차(입력한 재료와 치수에 따라 실제로 얻을 수 있는 값)를 계산합니다. -

Delay - 신호가 발신자에서 수신자까지 이동하는 데 걸리는 시간입니다. -

Inductance - 임피던스 계산기는Impedance 값을 사용하여 단위 길이당 인덕턴스를 계산합니다. -

Capacitance - 임피던스 계산기는Impedance 값을 사용하여 단위 길이당 커패시턴스를 계산합니다.

-

Board -

Stack Symmetry - 를 활성화하면 중간 유전체 레이어를 중심으로 일치하는 쌍으로 레이어를 추가할 수 있습니다. 활성화하면 레이어 스택이 중앙 유전체 레이어를 중심으로 대칭을 이루는지 즉시 확인합니다. 중앙 유전체 기준 레이어에서 등거리에 있는 레이어 쌍이 동일하지 않으면 스택이 대칭이 아님 대화 상자가 열립니다. -

Library Compliance - 이 옵션을 활성화하면 머티리얼 라이브러리에서 선택한 각 레이어에 대해 현재 레이어 프로퍼티가 라이브러리의 해당 머티리얼 정의 값과 비교하여 확인됩니다.

-

-

Substack - 이 정보는 현재 선택된 서브스택(레이어, 유전체, 두께 등)에 대한 정보입니다. 한 서브스택에서 다른 서브스택으로 전환하면 이 정보도 그에 따라 업데이트됩니다(현재 선택된 서브스택의 경우).

Stack Name - 의미 있는 서브스택 이름을 입력합니다. 이 필드는 X/Y 스택업 영역에 레이어 서브스택을 할당할 때 유용합니다.Is Flex - 서브스택이 플렉스인 경우 활성화합니다.Layers - 총 레이어 수입니다.Dielectrics - 유전체의 총 개수입니다.Conductive Thickness - 전도성 층의 두께입니다. 구리 신호 레이어를 전도성 레이어라고 합니다.Dielectric Thickness - 유전체 층의 두께입니다.Total Thickness - 보드의 총 두께입니다.

-

Other -

Roughness - 전도성 층의 거칠기를 나타냅니다.-

Model Type - 표면 거칠기의 영향을 계산하는 데 선호되는 모델입니다(다양한 모델에 대한 자세한 내용은 아래 문서 참조). 스택의 모든 구리 레이어에 적용됩니다(서브스택이어야 하나요?). -

Surface Roughness - 표면 거칠기 값(제작업체에서 제공). 0~10µm 사이의 값을 입력하며, 기본값은 0.1µm입니다 -

Roughness Factor - 거칠기 효과로 인해 예상되는 도체 손실의 최대 증가를 나타냅니다. 1에서 100 사이의 값을 입력합니다(기본값은 2).

-

설계 규칙 구성

라우팅 임피던스는 경로의 폭과 높이 및 주변 유전체 재료의 특성에 따라 결정됩니다. 에 정의된 재료 속성을 기반으로

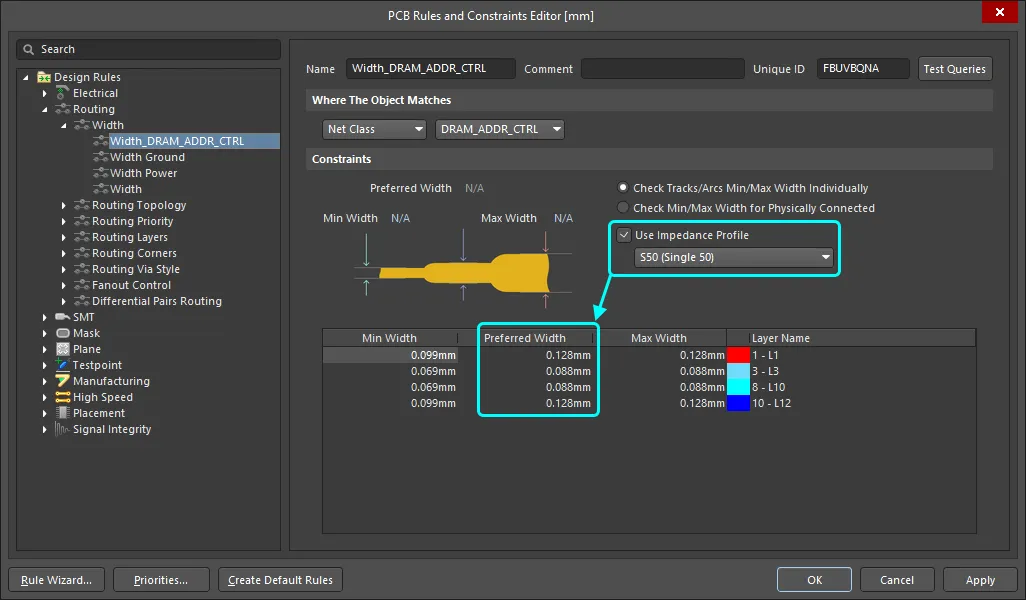

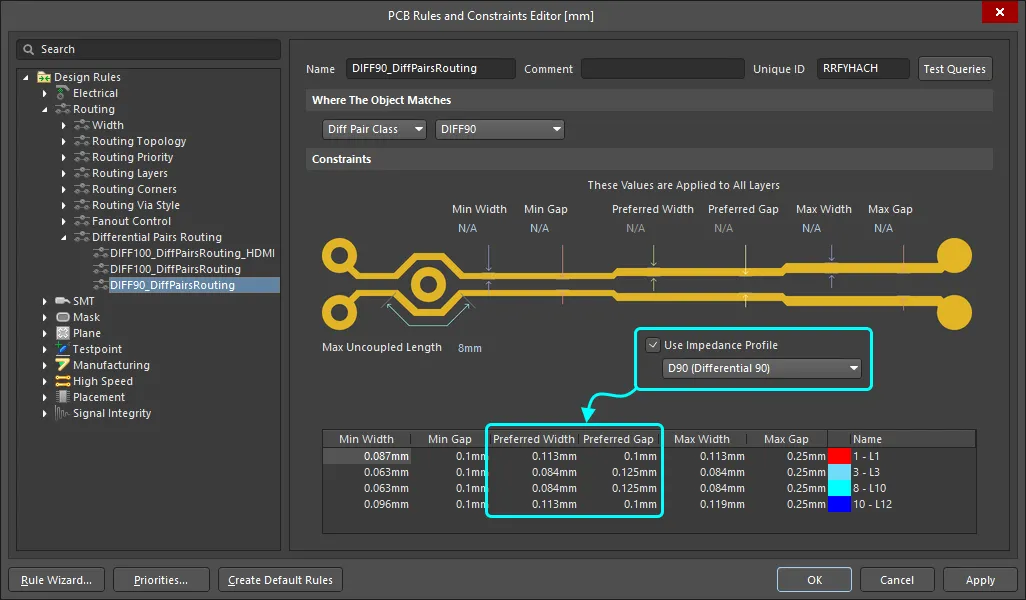

대부분의 보드 설계에서 특정 네트 세트는 제어된 임피던스로 라우팅됩니다. 일반적인 접근 방식은 아래 이미지와 같이 이러한 네트를 포함하는 네트 클래스 또는 차동 쌍 클래스를 생성한 다음 이 클래스를 대상으로 하는 라우팅 규칙을 생성하는 것입니다.

일반적으로는 수동으로

라우팅 폭 디자인 규칙

단면 네트의 경우 라우팅 폭은 라우팅 폭 디자인 규칙에 의해 정의됩니다.

임피던스 프로파일 사용을 선택하면 사용 가능한 레이어와 기본 폭은 선택한 프로파일에 의해 제어됩니다.

임피던스 프로파일 사용을 선택하면 사용 가능한 레이어와 기본 폭은 선택한 프로파일에 의해 제어됩니다.

디퍼렌셜 페어 라우팅 디자인 규칙

디퍼렌셜 쌍의 라우팅은 디퍼렌셜 쌍 라우팅 디자인 규칙에 의해 제어됩니다.

차동 쌍의 경우 사용 가능한 레이어, 선호 폭 및 선호 간격은 선택한 프로필에 의해 제어됩니다.

차동 쌍의 경우 사용 가능한 레이어, 선호 폭 및 선호 간격은 선택한 프로필에 의해 제어됩니다.

차동 페어 라우팅에대해 자세히 알아보기

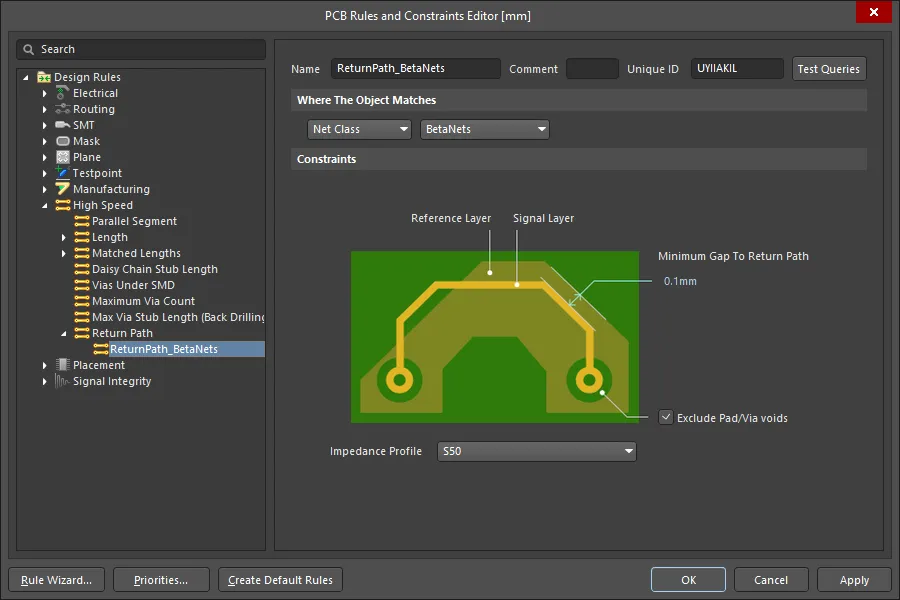

리턴 경로 디자인 규칙

리턴 경로 디자인 규칙을 통해 리턴 경로의 끊김이나 넥을 감지할 수 있습니다. 리턴 경로 설계 규칙은 규칙이 타겟팅하는 신호 위 또는 아래의 지정된 기준 레이어에서 연속적인 신호 리턴 경로를 확인합니다. 반환 경로는 기준 신호 레이어 또는 평면 레이어에 배치된 채우기, 영역 및 다각형 타설로 만들 수 있습니다.

반환 경로 레이어는 참조 레이어에 정의된

반환 경로 레이어는 선택한

반환 경로 레이어는 선택한

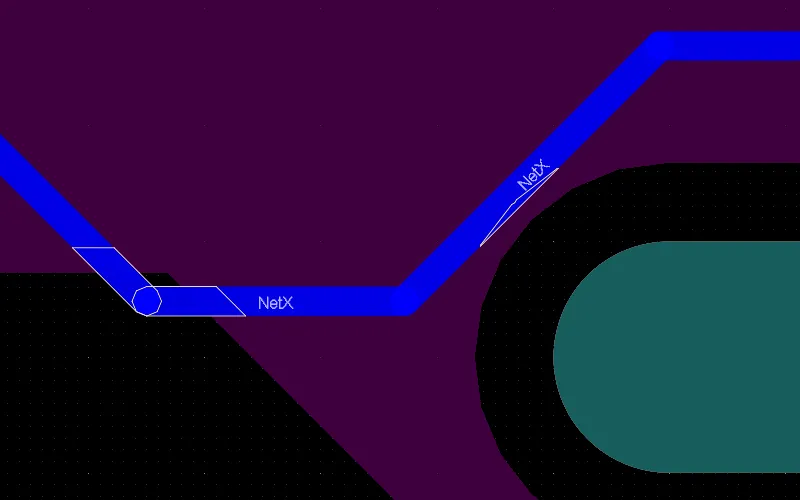

아래 이미지는 신호에 대해 감지된 리턴 경로 오류를 보여줍니다, NetX0.1mm

altium 디자이너에서 고속 디자인에대해 자세히 알아보기

필요한 임피던스로 넷 라우팅하기

기판을 라우팅하고 레이어를 변경하면 소프트웨어가 지정된 임피던스를 달성하는 데 필요한 크기로 트랙 폭을 자동으로 조정합니다. 이 대화형 임피던스 제어 라우팅은 임피던스 제어 PCB 설계 작업을 크게 간소화합니다.

경로 길이 조정

고속 설계 라우팅의 핵심 과제 중 두 가지는 경로의 임피던스를 제어하고 중요 네트워크의 길이를 맞추는 것입니다. 임피던스 제어 라우팅은 출력 핀을 떠나는 신호가 대상 입력 핀에서 올바르게 수신되도록 보장합니다. 경로 길이를 일치시키면 타이밍이 중요한 신호가 목표 핀에 동시에 도착할 수 있습니다. 경로 길이를 조정하고 일치시키는 것도 차동 페어 라우팅의 필수 요소입니다.

아코디언 패턴이 라우팅에 추가되어 차동 쌍의 길이가 일치하도록 보장합니다.

아코디언 패턴이 라우팅에 추가되어 차동 쌍의 길이가 일치하도록 보장합니다.

그리고

길이 튜닝에대해 자세히 알아보기

라우팅된 보드의 신호 무결성 테스트하기

설계 캡처 중에 가정된 라우팅 길이와 라우팅 임피던스를 사용하여 네트를 테스트한 것과 같은 방식으로 라우팅이 완료되면 보드에서 이 프로세스를 반복하여 잠재적인 임피던스 불일치 및 반사 문제를 확인해야 합니다. PCB 편집기에서

지정된 임피던스 달성

올바른 임피던스를 달성하기 위해 거치는 반복적인 치수 튜닝 프로세스 외에도 제작되는 PCB에서 달성할 최종 임피던스에 영향을 미치는 다른 요소들이 있습니다. 여기에는 PCB에 사용되는 유전체 재료의 일관성과 안정성, 그리고 에칭 공정의 일관성과 품질이 포함됩니다. 임피던스 제어 PCB가 필요한 경우 PCB 제작업체와 논의해야 합니다. 일부 제작업체는 원하는 스택업을 제공하면 트랙 형상에 대한 조언을 제공할 수 있습니다. 또한 많은 제작업체는 제작하는 각 패널에 임피던스 테스트 쿠폰을 포함할 수 있으며, 이를 사용하여 보드에서 달성한 실제 임피던스를 측정할 수 있습니다.

추가 읽기 및 리소스

이 문서에서는 신호 무결성 및 임피던스 제어 PCB 설계에 대한 주제를 소개합니다. 다음 링크를 사용하여 자세한 내용을 알아보고 업계 전문가가 개발한 리소스에 액세스하세요.

AI-localized

AI-localized