부모 페이지: 회로도로 설계 아이디어를 포착하기

전자 설계에는 회로의 반복 섹션을 포함하는 것이 일반적입니다. 스테레오 앰프일 수도 있고 64Channel 믹싱 데스크일 수도 있습니다. 이러한 유형의 설계는 Multi-Channel 설계이라고 알려진 기능 세트로 완벽하게 지원됩니다.

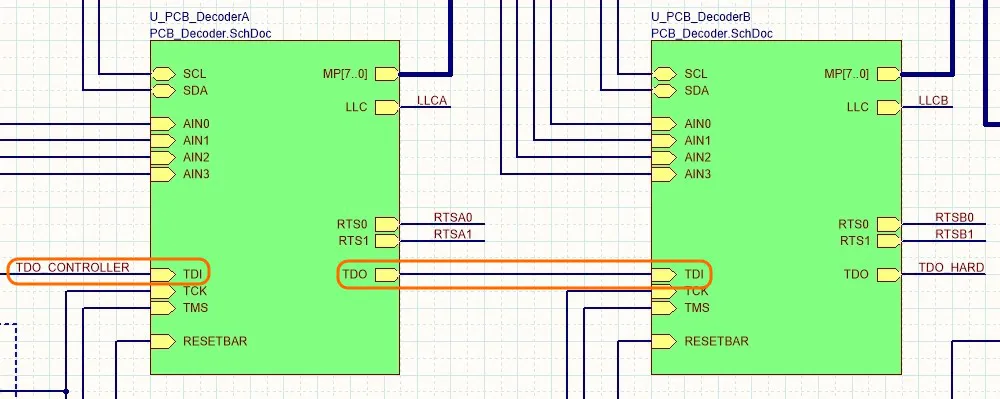

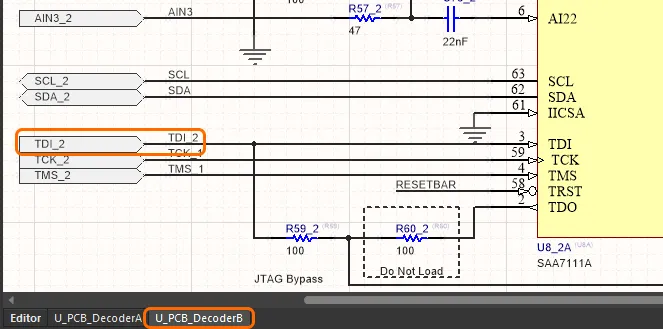

비디오 멀티플렉서의 두 디코더 Channel, Multi-Channel 설계 구조를 사용하면 디코더 Channel은 한 번만 포착됩니다.

Multi-Channel 설계에서는 반복되는 회로를 한 번 포착한 다음 소프트웨어에게 필요한 횟수만큼 반복하도록 지시합니다. 설계가 자동으로 컴파일되면 모든 부품와 연결이 사용자가 정의한 Channel 네이밍 체계에 따라 필요한 횟수만큼 메모리에 확장됩니다.

포착한 논리적 설계는 실제로 평면화되지 않으며, 소스는 항상 Multi-Channel 회로도로 유지됩니다. PCB 레이아웃으로 전송할 때 물리적인 부품와 Net은 자동으로 필요한 횟수만큼 확장됩니다. 회로도와 PCB 간에 작업할 수 있는 표준 교차 프로빙 및 교차 선택 도구에 대한 완전한 액세스 권한이 있습니다. 또한 PCB Editor에는 한 Channel의 배치 및 라우팅을 다른 모든 Channel에 복제하고 전체 Channel을 쉽게 이동하고 재배치할 수 있는 도구도 있습니다.

동적 컴파일

관련 페이지: 설계 프로젝트 확인하기

각 사용자 작업 후에는 동적 컴파일을 통해 설계 연결성 모델이 점진적으로 업데이트됩니다. 프로젝트를 수동으로 컴파일할 필요가 없으며, 이 작업은 자동으로 수행됩니다. 설계 프로젝트의 자동 컴파일 프로세스는 다음 세 가지 기능을 수행합니다:

- 설계 계층 구조를 인스턴스화합니다.

- 모든 설계 시트 간의 네트워크 연결성을 설정합니다.

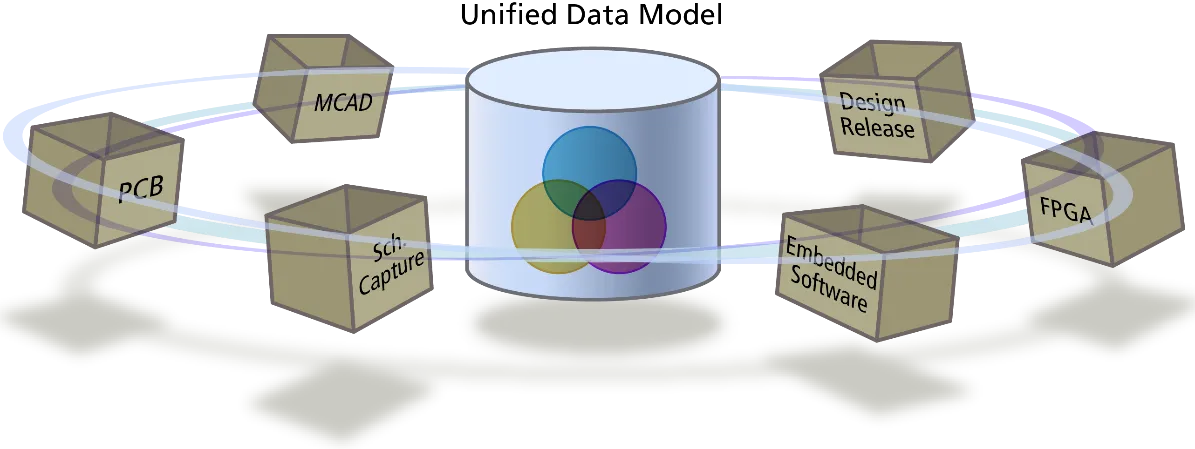

- 설계의 내부 통합 데이터 모델 (UDM, United Data Model)을 구축합니다.

이를 통해 수행된 설계 변경 사항이 즉시 Navigator 및 Projects 패널에 반영됩니다.

프로젝트의 컴파일된 모델은 통합 데이터 모델 (UDM)로 참조됩니다. UDM에는 설계의 모든 부품에 대한 자세한 설명과 서로 연결된 방식이 포함됩니다.

UDM과 컴파일러 설정 간의 논리적, 전기적 및 도면 오류를 확인하기 위해 프로젝트를 유효성 검사해야 합니다. 이 명령은 주 메뉴에서 프로젝트 » 프로젝트 유효성 검사 명령을 선택하거나, 프로젝트 패널의 항목 위에서 마우스 오른쪽 버튼을 클릭하고 컨텍스트 메뉴에서 프로젝트 유효성 검사 명령을 선택하여 액세스할 수 있습니다.

컴파일러에서 감지된 모든 위반 사항은 메시지(Message) 패널에 경고 및/또는 오류로 나열됩니다. 컴파일러는 위반 사항을 확인할 때 소스 문서에 대한 오류 보고 및 연결 행렬 탭에서 정의된 옵션을 사용합니다 (프로젝트 유형에 적용되는 경우).

Altium Designer 20.0 이전 버전에서는 통합 데이터 모델을 구축하기 위해 프로젝트를 수동으로 컴파일해야 했습니다. 그 이후로는 사용자 작업 후 동적 컴파일을 통해 설계 데이터 모델이 점진적으로 업데이트됩니다. 이를 동적 데이터 모델(DDM, Dynamic Data Model)이라고 합니다. 프로젝트의 수동 컴파일은 필요하지 않으며, 모든 작업이 자동으로 수행됩니다. 설계 연결성 모델은 동적 컴파일을 통해 사용자 작업 후 점진적으로 업데이트됩니다.

통합 데이터 모델

Multi-Channel 설계를 이해하기 위해서는 설계 데이터가 어떻게 관리되는지 이해하는 것이 도움이 됩니다. 소프트웨어의 기본 요소는 통합 데이터 모델(UDM)입니다. 프로젝트가 자동으로 컴파일되면 설계 프로세스의 중심에 위치한 단일하고 일관된 모델이 생성됩니다. 모델 내의 데이터는 소프트웨어 내의 다양한 Editor와 서비스를 사용하여 액세스하고 조작할 수 있습니다. 다양한 설계 도메인마다 별도의 데이터 저장소를 사용하는 대신, UDM은 설계의 모든 측면에서 모든 정보를 수용할 수 있도록 구조화되어 있으며, 이에는 부품와 그들의 연결성도 포함됩니다.

통합 데이터 모델은 모든 Editor에 모든 설계 데이터를 제공하며, Multi-Channel 설계와 같은 고급 기능을 제공합니다.

UDM은 계층적 설계 시스템과 결합하여 Multi-Channel 설계 기능을 제공합니다. "Channel"은 시트 심볼 내의 회로입니다. 이 시트 심볼 아래에는 단일 시트 또는 다른 하위 시트를 포함하는 프로젝트 구조의 전체 분기가 있을 수 있습니다. 또한 2단계 Multi-Channel 설계에서는 상위 Channel을 "뱅크"라고 하고, 하위 수준의 Channel을 "Channel"이라고 합니다.

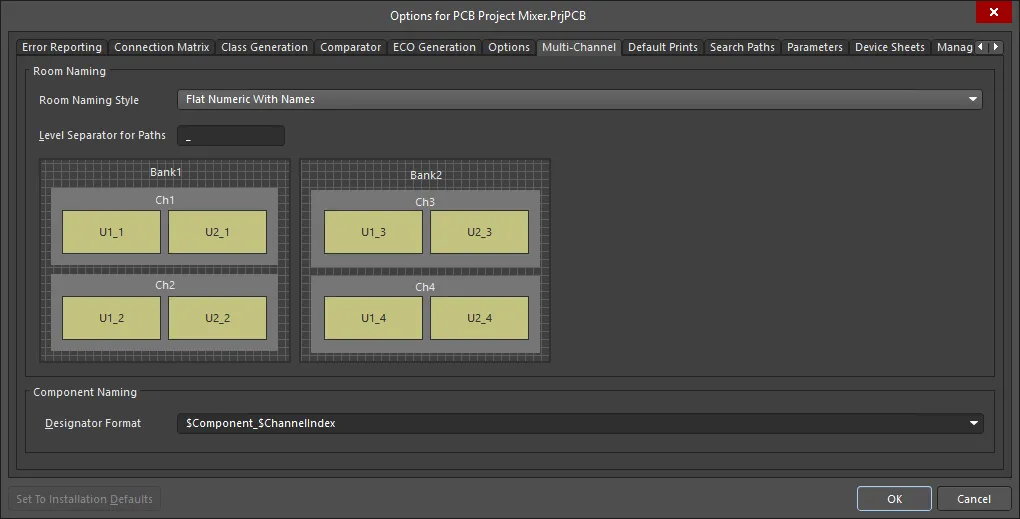

이 전체적으로 PCB에 준비된 설명이 메모리에 존재하기 때문에, 부품 설계자와 네트와 같은 반복된 객체를 처리하는 체계적인 방법이 있다면 회로 부분을 반복할 수 있습니다. 체계적인 명명은 프로젝트 옵션 대화 상자의 다음과 같이 Multi-Channel 탭에서 정의됩니다.

Multi-Channel 설계 생성

회로 부분이 반복되는 설계를 Multi-Channel이라고 합니다. 이는 시트 심볼 수준에서 수행됩니다. 다음 중 하나로 수행됩니다:

- 동일한 하위 도면을 참조하는 여러 시트 심볼을 배치하거나

- 참조된 하위 도면을 필요한 횟수만큼 반복하는 단일 시트 심볼을 구성하는 것

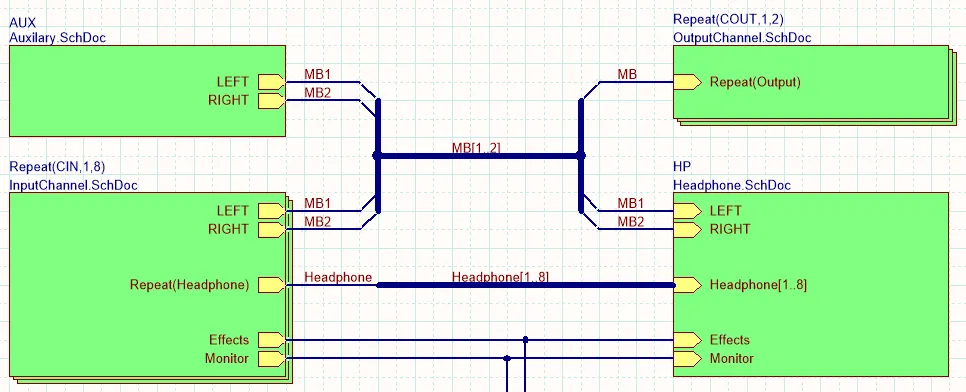

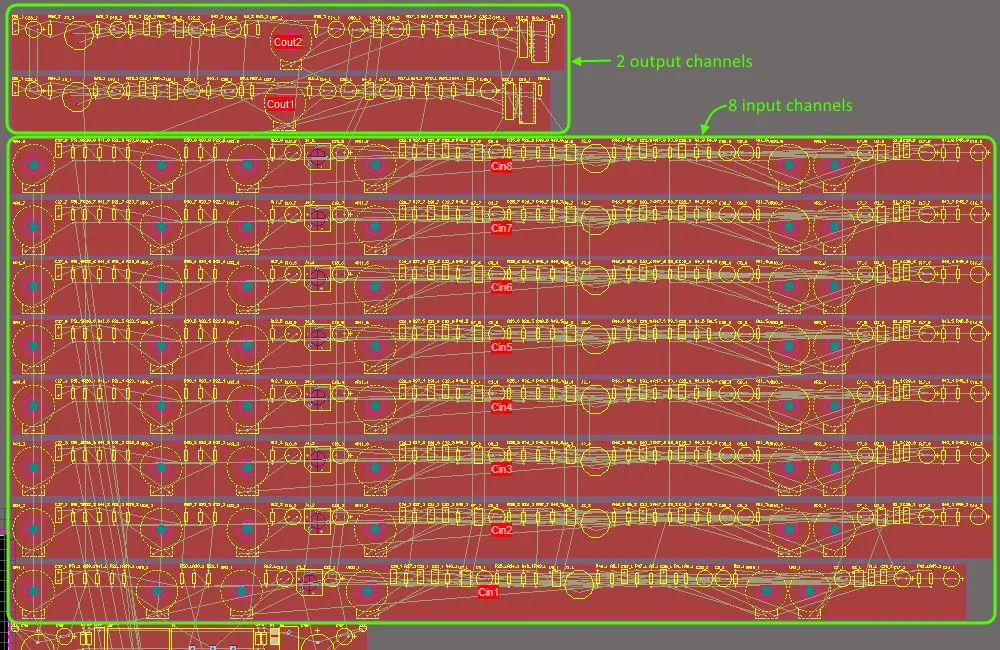

첫 번째 이미지 - 동일한 하위 시트 (PortIO.SchDoc)를 참조하는 네 개의 시트 심볼이 있습니다. 두 번째 이미지 - Repeat 키워드의 존재로 인해 InputChannel.SchDoc가 여덟 번, OutputChannel.SchDoc가 두 번 반복됩니다.

위의 이미지에서 Multi-Channel 설계를 생성하는 두 가지 접근 방식이 보여집니다. 첫 번째 이미지에서는 동일한 하위 시트 (PortIO.SchDoc)를 참조하는 네 개의 시트 심볼이 있습니다. 두 번째 이미지에서는 시트 심볼의 Designator 필드에 Repeat 키워드의 존재로 인해 InputChannel.SchDoc가 여덟 번 반복되고 OutputChannel.SchDoc가 두 번 반복됩니다.

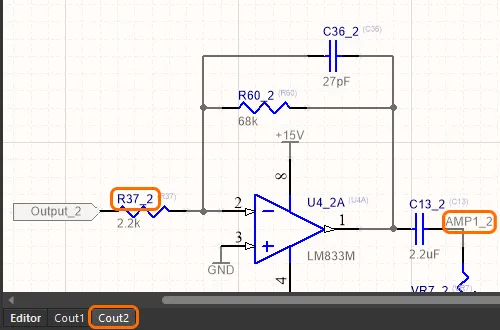

프로젝트에서 반복되는 부품 디자이너와 Net 이름은 표준 네이밍 Schematic를 사용하여 해결됩니다. 예를 들어, 하나의 네이밍 Schematic는 반복되는 부품와 Net 식별자(Net Label 및 Port)에 Channel 인덱스를 추가하는 것입니다. 아래 이미지에서 강조된 부분을 참조하십시오.

프로젝트를 열 때 도면 하단에 나타나는 탭에 유의하십시오. Editor 탭에는 캡처한 논리적 설계이 포함되어 있으며, 다른 컴파일된 탭(COUT1 및 COUT2)도 표시되어 PCB Editor로 전송될 물리적 설계을 나타냅니다. 각 물리적 Channel에 대한 탭이 있을 것입니다.

컴파일된 프로젝트, 논리적 뷰를 위한 탭과 PCB로 전송되는 각 물리적 Channel을 위한 탭이 표시됩니다. 반복되는 디자이너와 Net 식별자가 어떻게 관리되는지 주목하십시오.

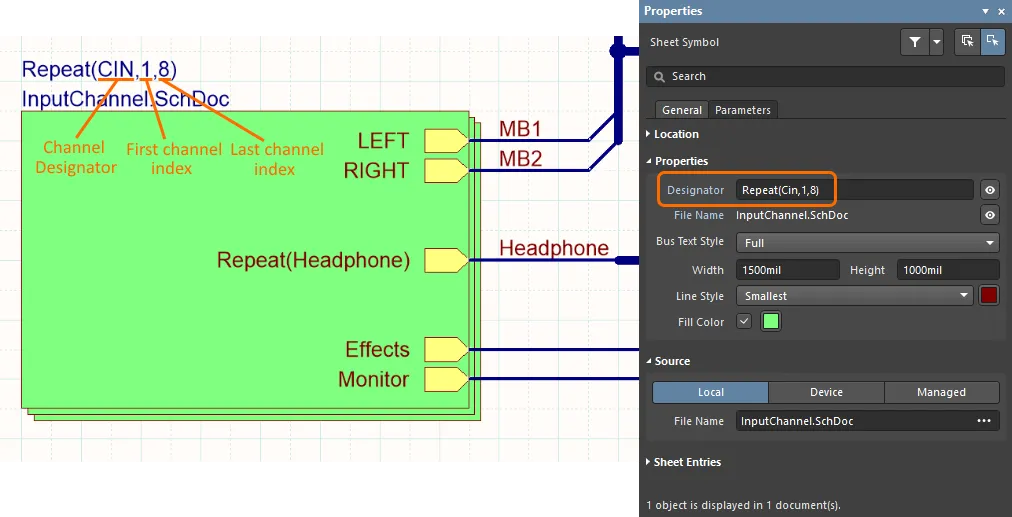

반복 키워드

언급한 대로, Channel은 동일한 하위 시트를 참조하는 여러 시트 심볼을 배치하거나 시트 심볼의 Designator 필드에 Repeat 키워드를 포함하여 반복됩니다. Repeat 키워드를 사용하면 시트 심볼은 쌓인 시트 심볼 세트로 그려집니다.

Repeat 문은 Channel 디자이너와 Channel 수를 정의합니다. 시트 심볼이 반복된 Channel을 나타내기 위해 쌓인 심볼 세트로 그려진 것을 주목하세요.

각 Channel은 시트 심볼의 Designator에서 가져온 Channel 디자이너로 식별됩니다. 여러 시트 심볼을 배치하여 설계을 Channel화하는 경우, Channel 디자이너는 각 시트 심볼에 정의된 Designator 값입니다. Repeat 키워드를 사용하여 설계을 Channel화하는 경우, Channel 디자이너는 Repeat 키워드에 의해 정의된 ChannelIdentifier+ChannelIndex입니다.

Repeat 키워드를 사용할 때 Designator 필드의 구문은 다음과 같습니다:

Repeat(<ChannelIdentifier>,<ChannelIndex_1>,<LastChannelIndex_n>)

프로젝트 옵션 대화 상자의 Options 탭에서

New Indexing of Sheet Symbols 옵션이 활성화된 경우, 반복된 시트 심볼의 첫 번째 또는 마지막 인덱스로 0을 포함하여 모든 숫자를 사용할 수 있으며, 마지막 인덱스는 항상 첫 번째 인덱스보다 커야하며 음수는 허용되지 않습니다.

Multi-Channel 네이밍

한 번 캡처한 후 반복해서 사용할 수 있는 개념인 Multi-Channel 설계는 소프트웨어의 통합 데이터 모델(UDM)을 기반으로 제공됩니다. 반복되는 부품는 시스템적인 네이밍 체계를 사용하여 이름이 지정되며, 이는 프로젝트 옵션(Options for Project) 대화 상자의 Multi-Channel 탭에서 구성됩니다.

이 대화 상자에는 방(Rooms)의 네이밍을 제어하는 상단 섹션과 해당 방 내의 부품의 네이밍을 제어하는 하단 섹션이 포함되어 있습니다. 방 레벨에서는 2가지의 평면 네이밍 스타일과 3가지의 계층적 네이밍 스타일이 있으며, 일반적으로 Channel 내에 Channel이 있는 설계인 경우에만 계층적 네이밍 스타일을 선택해야 합니다. 그렇지 않은 경우, 평면 방 네이밍 스타일이 더 짧고 이해하기 쉽습니다.

부품 네이밍의 경우, $Component$ChannelAlpha 또는 $Component_$ChannelIndex 옵션을 사용하면 가장 짧고 해석하기 쉬운 부품 지정이 가능합니다. 또한, 사용 가능한 키워드를 사용하여 직접 디자이너 네이밍 체계를 구성할 수도 있습니다.

반복되는 부품(및 Net)는 프로젝트 옵션 대화 상자의 Multi-Channel 탭에서 선택한 시스템적인 네이밍 체계를 통해 관리됩니다.

- 부품뿐만 아니라 부품 명명 체계는 각 Channel 내에서 Net을 고유하게 식별하는 데 사용됩니다. 이 체계는 Net Label 및 Port를 포함한 Net 식별자의 이름을 변경하는 데 사용됩니다.

- 이러한 이름들의 표시는 아래의 컴파일된 이름 표시 섹션에서 설명됩니다.

Room의 역할

Room은 보드에서 영역을 정의하는 PCB 설계 객체로 사용됩니다. 이후 두 가지 방법으로 사용할 수 있습니다:

- 객체 포함 - Room은 다각형 모양 객체와 같이 배치되지만, 실제로는 배치 설계 규칙으로 생성됩니다. Room의 정의 중 일부는 해당 room 내에 포함되어야 하는 객체를 지정하는 것입니다. 이는 종종 부품입니다. Room이 이동되면 room 내의 모든 부품도 함께 이동합니다.

- 다른 설계 규칙의 범위로 사용 - Room은 자체적인 규칙일 뿐만 아니라 다른 설계 규칙의 범위로도 사용할 수 있습니다. 예를 들어, 하나의 라우팅 폭 설계 규칙은 Net 클래스의 라우팅 폭을 정의하고, Room 범위를 가진 더 높은 우선순위의 설계 규칙은 해당 Room 내의 해당 Net 클래스에 적용할 다른 폭을 지정할 수 있습니다.

Multi-Channel 설계에서는 방들이 매우 잘 작동합니다. 회로도 Editor에서 PCB Editor로 전송되는 동안 프로젝트 옵션 대화 상자의 클래스 생성 탭의 옵션에 따라 자동으로 생성될 수 있습니다. 각 시트 심볼마다 방이 생성됩니다. 해당 Channel의 부품를 클러스터링하는 것 외에도, 방은 해당 방 내의 부품의 이름 지정에 사용될 수 있습니다. 방과 그들이 보드 설계 프로세스에서의 역할에 대해서는 이 문서의 Multi-Channel PCB 설계 섹션에서 자세히 설명됩니다.

평면 부품 번호 체계를 선호하는 경우, Board Level Annotation을 수행하여 체계적인 명명 체계를 대체할 수 있습니다. Board Level Annotation이라고 불리는 이유는 부품 디자이너가 전체 컴파일된 설계(물리적 설계)에만 적용되기 때문입니다. 이 설계는 PCB가 될 운명을 가지고 있습니다.

Multi-Channel 설계에서의 연결성

Multi-Channel 설계의 경우, Net 식별자 범위를 자동, 계층적 또는 엄격한 계층적으로 설정하세요. Multi-Channel 설계는 소프트웨어가 설계를 컴파일할 때 이 구조적 모델을 사용하여 Channel을 메모리에 인스턴스화하기 때문에 계층적이어야 합니다.

Net이 반복되는 Channel에 연결되는 경우 소프트웨어는 두 가지 다른 연결 요구 사항을 지원해야 합니다. Net은 다음 중 하나일 수 있습니다:

- 모든 Channel에 공통적인 경우

- 각 Channel마다 고유한 경우

이에 대한 지원 수준은 Channel을 정의하는 데 사용된 방법에 따라 다릅니다 (여러 개의 시트 심볼 또는 Repeat 키워드를 통해). 설계이 여러 개의 시트 심볼 (각 Channel에 대한 개별 시트 심볼)을 사용하는 경우, Net 연결성은 디자이너가 배치한 배선에 의해 명시적으로 정의됩니다.

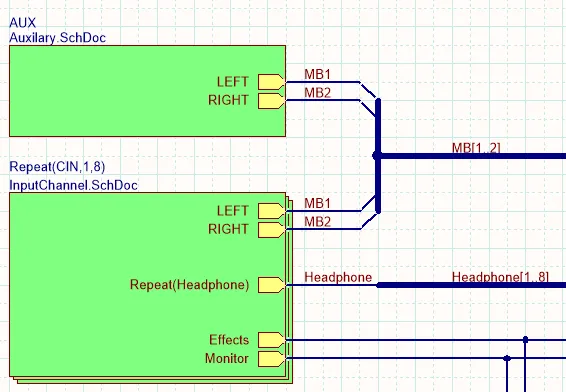

이 설계은 Repeat 키워드를 사용하여 여러 Channel을 생성합니다.

설계이 Repeat 키워드를 사용하는 경우, 다음과 같은 연결 규칙이 적용됩니다.

| 모든 Channel에 Net 전달하기 |

만약 Net이 모든 Channel에서 사용 가능해야 한다면, 그냥 시트 엔트리에 연결하면 됩니다. 위 이미지에서는 Monitor Net이 InputChannel.SchDoc 시트 심볼에 연결되어 있습니다. Effects, MB1, MB2 Net도 모든 Channel에서 사용 가능합니다. 버스 내의 Net도 동일한 방식으로 처리됩니다. 버스가 시트 엔트리에 연결되면, 해당 버스의 각 요소는 모든 Channel에서 사용 가능합니다. |

| 특정 Channel에 Net 전달하기 |

버스에서 각 Channel에 하나의 Net을 할당하려면, 시트 엔트리에 Repeat 키워드를 사용합니다. 위 이미지에서는 Headphone 버스에 Repeat(Headphone)이라는 이름의 시트 엔트리가 있습니다. 이 경우, Net Headphone1은 Channel CIN1에 연결되고, Headphone2는 Channel CIN2에 연결됩니다. Repeat 키워드를 사용하여 Channel을 생성한 경우, 개별 Net을 하나의 Channel에만 전달하는 것은 불가능합니다. 이 경우, 각 Channel에 개별적인 시트 심볼을 배치해야 합니다. |

Repeat 키워드를 사용할 때, 하네스를 Channel에 전달하는 것은 지원되지 않습니다.

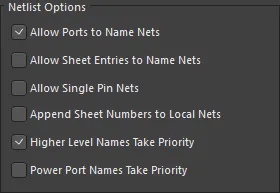

Net의 이름 지정 방법

최종적으로, 각 Net은 PCB에서 하나의 이름만 가질 수 있습니다 (하나의 PCB Net은 두 개의 이름을 가질 수 없습니다). 소프트웨어는 여러 개의 이름을 가진 Net을 자동으로 하나의 이름으로 해결하여 프로젝트에서 하나의 이름만 가지도록 합니다. Multi-Channel 설계에서 Net의 라벨이 의미 있는 방식으로 표시되도록 네이밍 옵션을 구성하는 것이 중요합니다. Net 네이밍 옵션은 Net리스트 옵션 섹션에 있으며 옵션 탭의 프로젝트 옵션 대화 상자에 있습니다.

Multi-Channel 설계에서 이러한 옵션을 설정하는 좋은 방법은 상위 레벨 이름 우선 옵션을 활성화하고 Channel화된 하위 시트에 연결된 모든 Net에 Net 라벨을 배치하는 것입니다.

예를 들어, 아래 이미지를 살펴보십시오. 두 개의 시트 심볼이 모두 시트 PCB_Decoder.SchDoc를 가리키고 있으므로 이 회로에는 U_PCB_DecoderA와 U_PCB_DecoderB라는 2개의 Channel이 있습니다.

시트 심볼에는 JTAG 경계 스캐닝 체인의 Test Data In 라인 인 TDI라는 시트 엔트리가 포함되어 있습니다. DecoderA의 TDO (Test Data Out)는 다음 장치의 TDI에 연결되며, 이 장치는 DecoderB Channel에 있습니다.

두 개의 디코더 Channel은 동일한 회로도인 PCB_Decoder.SchDoc을 참조하는 두 개의 시트 심볼을 배치하여 생성됩니다.

프로젝트를 열면 회로도 뷰 하단에 Channel 탭인 U_PCB_DecoderA와 U_PCB_DecoderB가 표시됩니다. 이 탭은 물리적 설계를 PCB Editor로 전달하는 것을 보여줍니다. 아래 이미지에서, 캡처된 디코더 회로의 회로도는 왼쪽의 Editor 탭에 표시되며, 그 다음으로 해당 회로의 두 개의 물리적 Channel인 U_PCB_DecoderA와 U_PCB_DecoderB가 표시됩니다.

원래 캡처된 회로도에서 설계자는 Net을 TDI로 라벨링했습니다 (첫 번째 이미지). 소프트웨어가 더 높은 수준의 Net 이름인 TDO_CONTROLLER를 DecoderA 탭에 적용한 것을 확인할 수 있습니다 (두 번째 이미지). 이는 더 높은 수준의 Net 이름이 이 설계에서 우선순위를 가지도록 설정되었기 때문입니다. DecoderB에는 더 높은 수준의 이름이 정의되어 있지 않으므로, 원래 Net 이름인 TDI가 이 Channel에서 TDI_2로 식별되었습니다 (세 번째 이미지). 이는 프로젝트 옵션 대화 상자의 Multi-Channel 탭에서 정의된 네이밍 스킴에 따라 구성된 것입니다 (네트와 부품 모두를 각 Channel 내에서 식별하기 위해 부품 네이밍 스킴이 사용됩니다).

PCB_Decoder.SchDoc 회로도: 첫 번째 이미지 - 캡처된 회로도; 두 번째와 세 번째 이미지 - 두 Channel의 컴파일된 뷰.

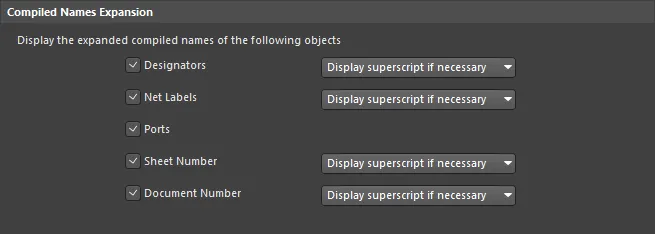

컴파일된 이름 표시

Multi-Channel 설계에서 Net을 추적하고 분석하는 것은 혼란스러울 수 있습니다. 반복되는 Net을 식별하기 위해 이름을 변경해야하지만 여전히 고유해야합니다. 이를 돕기 위해 컴파일된 객체 이름의 표시를 제어하는 여러 옵션이 있습니다. 이에는 부품 디자이너, Net Label, 전원 Port 및 Port가 포함됩니다. 인쇄 유형의 출력을 생성할 준비가 되면 시트 및 문서 번호에 대한 옵션도 있습니다.

컴파일된 객체 이름의 표시는 회로도 - 컴파일러 페이지에서 환경 설정 대화 상자에서 구성됩니다. 아래 이미지에서 확인할 수 있습니다.

컴파일된 객체 이름의 표시를 구성하려면 위첨자는 부품 디자이너에 유용합니다.

일반적으로 디자이너와 Net 라벨을 표시하고, 문제를 진단하는 경우 Port가 유용합니다. 시트 번호와 문서 번호도 중요하며 올바르게 구성되어야 합니다. 부품 및 시트 번호에 대한 정보 링크는 설계 Annotation 섹션에서 찾을 수 있습니다.

Schematic - 컴파일러 페이지의 환경 설정 대화 상자에서 Net 라벨 옵션은 파워 Port 개체의 확장을 결정합니다.

필요한 경우 위 첨자 표시 옵션을 선택하면 현재 문서 보기에 비표시 보기의 개체 식별자가 위 첨자로 포함됩니다. 이를 선호에 맞게 구성하세요.

Multi-Channel 설계의 Channel 2 (CIN2)에 대한 뷰입니다. 원래 논리적인 Schematic의 디자이너와 Net 이름이 위 첨자로 표시되는 것을 확인하세요.

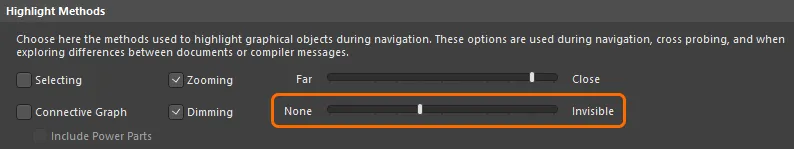

Channel(물리적) 탭에서 일부 회로도 요소가 흐릿하게 표시되는 이유가 궁금하신가요? 기본 설정은 Channel 탭에서 편집 가능한 객체를 표준 표시 강도로 표시하고, 편집할 수 없는 객체는 흐리게 표시합니다. 흐리게 표시되는 강도는 시스템 - Explorer 페이지의 환경 설정 대화 상자에서 설정됩니다. 객체를 흐리게 표시하는 장점은 Channel 탭에서 지원되지 않는 편집 작업(예: Channel 탭에서 Net Label을 이동하는 작업)을 시도하지 않도록 도와줍니다. 필요한 대로 흐릿한 수준을 설정하세요.

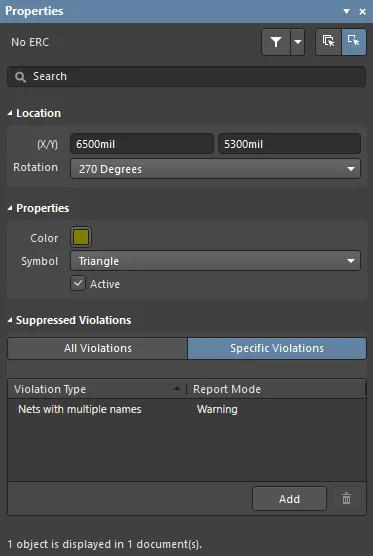

여러 개의 Net 이름 오류 해결하기

회로도 Editor의 오류 확인 옵션은 기본적으로 여러 개의 이름을 가진 Net의 모든 인스턴스를 표시합니다. 이는 의도적으로 이름을 변경한 경우에 발생할 수 있습니다. 예를 들어, Net이 시트 심볼에 들어가고 해당 시트 내에서 다른 이름을 사용하려는 경우입니다. 아래 이미지는 이에 대한 여러 가지 예시를 보여줍니다. 상단 시트에서 왼쪽과 오른쪽 출력이 버스로 묶여 있지만 시트 항목에서는 Left와 Right로 호출됩니다.

버스를 사용한 이유는 두 출력 Channel을 반복 키워드를 가진 단일 시트 심볼로 나타낼 수 있기 때문입니다. 만약 왼쪽과 오른쪽 Channel에 별도의 와이어를 사용한다면, 설계자는 왼쪽과 오른쪽 출력 Channel을 위한 별도의 시트 심볼을 배치하고 각 출력을 해당하는 출력 시트 심볼에 연결해야 했을 것입니다.

소프트웨어에게 여러 Net 식별자를 처리하는 방법을 지시해야 합니다. 이를 위해 다음 중 하나를 수행해야 합니다:

- 다중 이름을 가진 Net 오류 확인을 보고 없음으로 설정하십시오. 프로젝트 옵션 대화 상자의 오류 보고 탭에서 이 작업을 수행할 수 있습니다. 이는 설계 전체에서 이 오류 조건의 모든 확인을 차단하기 때문에 선호되지 않는 옵션입니다. 대안으로 다음을 수행할 수 있습니다.

- 영향을 받는 Net에 특정 No ERC 지시문을 배치하려면 메시지 패널에서 오류/경고를 마우스 오른쪽 버튼으로 클릭한 다음 이 위반에 대한 특정 No ERC 마커 배치 명령을 선택하십시오. 이렇게 하면 NoERC 객체 배치 모드로 전환되며, 커서에 사전 구성된 특정 NoERC 마커가 부착되어 오류가 발생한 Net에 배치 준비가 됩니다. 배치한 후에는 두 번 클릭하여 스타일과 색상을 구성하십시오.

주황색으로 감싸인 작은 삼각형에 유의하십시오. 이는 MB1 및 MB2 Net에서 중복 Net 이름 오류를 비활성화하기 위해 배치된 특정 No ERC 마커입니다.

다중 보드 설계 Annotation

설계 캡처 프로세스의 중요한 부분은 설계에 Annotation을 달아 각 부품와 각 회로도 시트에 고유한 식별자를 부여하는 것입니다. 이는 Multi-Channel 설계의 두 단계 프로세스입니다. 먼저, 배치한 부품와 그린 시트에 번호를 매겨야 합니다. 그런 다음 반복 Channel에서 인스턴스화된 부품와 시트에도 번호를 매겨야 합니다.

평면 부품 번호 지정 체계를 선호하는 경우, Board Level Annotation을 수행하여 체계적인 명명 체계를 대체할 수 있습니다. Board Level Annotation이라고 하는 이유는 부품 디자이너가 전체 컴파일된 설계(물리적 설계)에만 적용되기 때문입니다. 이는 PCB가 될 운명을 가진 설계입니다. 회로도 Annotation은 Board Level Annotation의 선행 조건이며, 다중 부품 부품가 패키지화되고 각 부품에 고유한 식별자가 있는지 확인합니다.

이러한 Board Level Annotation은 각 논리적 디자이너를 할당된 물리적 디자이너에 매핑하는 .Annotation 파일에 저장됩니다. 이 파일은 프로젝트의 일부이므로 저장하라는 메시지가 표시됩니다.

Multi-Channel 설계에서 Annotation 프로세스는 부품 디자이너가 상당히 긴 부품 디자이너를 생성할 수 있으므로 PCB에서 디자이너 문자열을 배치하는 것이 어려울 수 있습니다. PCB에서 논리적 및 물리적 디자이너 표시 사이에서 선택할 수 있습니다. -

자세히 알아보기.

Multi-Channel PCB 설계

회로도 Editor에서 PCB Editor로 설계를 전송할 때, 각 시트의 부품은 프로젝트 옵션에서 room 생성이 활성화되어 있다면 PCB 배치 공간에 클러스터링 됩니다.

Multi-Channel 설계에서 room을 사용하는 큰 장점은 PCB Editor가 한 room(Channel)에서의 배치 및 라우팅을 다른 room(Channel)로 복제할 수 있다는 것입니다. room은 하나의 개체처럼 이동할 수도 있어 PCB에서 Channel을 정렬하는 과정을 간소화합니다.

회로도 Editor에서 PCB Editor로 설계가 전송된 후의 여덟 개의 입력 Channel과 두 개의 출력 Channel, 빨간색 영역은 room입니다.

PCB Room의 역할

Room은 보드에서 영역을 정의하는 PCB 설계 객체로, 다음 두 가지 방식으로 사용될 수 있습니다:

- 객체 포함 - Room은 다각형 모양 객체와 같이 배치되지만, 실제로는 배치 설계 규칙으로 생성됩니다. Room의 정의 중 일부는 해당 Room에 포함되어야 하는 객체(일반적으로 부품)를 지정하는 것입니다. Room이 이동되면 Room 내의 모든 부품도 함께 이동합니다.

- 다른 설계 규칙 범위로 사용 - Room은 자체적인 규칙일 뿐만 아니라 다른 설계 규칙의 범위로 사용될 수도 있습니다. 예를 들어, 하나의 라우팅 폭 설계 규칙은 Net 클래스의 라우팅 폭을 정의하고, Room 범위를 가진 우선순위가 더 높은 설계 규칙은 해당 Room 내의 해당 Net 클래스에 적용할 다른 폭을 지정할 수 있습니다.

Room은 Multi-Channel 설계에서 매우 유용합니다. 각 시트 심볼마다 Room이 있는 옵션을 기반으로 회로도 Editor에서 PCB Editor로 전송되는 동안 자동으로 생성될 수 있습니다. 해당 Channel의 부품를 클러스터링하는 것 외에도, Room은 해당 Room 내의 부품의 이름 지정에도 사용될 수 있습니다.

유용한 Room 조작 명령

- Design » Rooms - 이 하위 메뉴에는 Room을 정의하고 수정하는 데 유용한 여러 명령이 있습니다.

- Design » Rooms » Room 형식 복사 - 이 명령을 사용하여 한 Room(Channel)의 배치와 라우팅을 다른 Room(Channel)에 복제할 수 있습니다.

- Design » Rooms » Room 이동 - Room은 커서 아래에 다른 설계 객체가 없는 곳에서 클릭하고 들고 이동할 수 있습니다. 커서는 가장 가까운 부품 패드 또는 Room 꼭짓점에 자동으로 맞춰집니다. 설계 객체를 클릭하지 않고 클릭하고 들 수 없는 경우에는 이 명령을 사용하세요.

- Edit » Select » Room Connections - 이 명령을 사용하여 패드에서 시작하고 Room 내에서 끝나는 모든 구리 세그먼트를 선택할 수 있습니다.

전자 설계, PCB 및 공학과 관련된 특정 텍스트가 제공됩니다. 한국어로 번역해주세요. 이미지의 alt 텍스트를 제외한 class, id, href 및 유사한 html 속성은 무시해야 합니다.

부품이 연결되는 방법

각 회로도 부품는 고유 식별자(UID, Unique Identifier)를 통해 PCB 부품에 연결됩니다. UID는 회로도 부품이 시트에 배치될 때 할당되며, 설계가 PCB Editor로 전송될 때 PCB 부품에 할당됩니다. 이 방식은 간단한 설계에는 적합하지만, 동일한 회로도 부품이 각 물리적 Channel에서 반복되는 Multi-Channel 설계를 지원할 수 없습니다(따라서 PCB 부품은 동일한 UID를 가질 것입니다).

이를 위해 PCB 부품의 UID는 부모 시트 심볼의 UID와 회로도 부품의 UID를 결합하여 생성됩니다. Multi-Channel 설계가 생성된 방식에 따라 PCB UID의 구문이 약간 변경됩니다.

동일한 회로도 시트를 참조하는 여러 시트 심볼을 배치하여 생성된 Multi-Channel 설계의 경우, 각 시트 심볼은 고유한 ID를 제공할 수 있으므로 PCB UID는 다음 형식을 갖습니다:

\SheetSymbolUID\SchComponentUID

Repeat 키워드를 사용하여 생성된 Multi-Channel 설계의 경우, 사용 가능한 시트 심볼 UID가 하나 뿐이므로 PCB UID에는 ChannelIndex도 포함되어 있으며, 다음 형식을 갖습니다:

\ChannelIndex+SheetSymbolUID\SchComponentUID

부품 연결은 부품 연결 편집 대화 상자(프로젝트 » 부품 연결 명령)를 통해 관리됩니다. 이 대화 상자에서 변경 사항을 적용하면 PCB UID가 회로도 UID와 일치하도록 업데이트됩니다.

위 설명은 부품가 연결되는 방법을 설명합니다. 참고로 Altium Designer의 최신 버전(18.0 이상)에서는 패널과 대화 상자에 더 이상 UID가 표시되지 않습니다.

PCB에 디자이너 표시하기

Multi-Channel 설계에서 디자이너 문자열을 위치시키는 것은 어려울 수 있습니다. 디자이너 문자열은 꽤 길 수 있기 때문입니다. 짧은 이름으로 결과를 얻을 수 있는 네이밍 옵션을 선택하는 것 외에도, 다른 옵션은 원래 논리적인 부품 표시만 표시하는 것입니다. 예를 들어, C30_CIN1은 C30으로 표시됩니다. 이 경우, 각 Channel을 나타내기 위해 보드에 다른 표기법을 추가해야 합니다. 예를 들어, 부품 오버레이에 각 Channel 주위에 상자를 그리는 것입니다.

PCB Editor의 기타 섹션에서 PCB에서 논리적인 디자이너 표시와 물리적인 디자이너 표시 중 선택할 수 있습니다. Multi-Channel 설계의 부품에 논리적인 디자이너를 표시하도록 선택하면, 이러한 디자이너는 PCB와 출력물(인쇄물 및 Gerber 파일 등)에 표시됩니다. 그러나 Bill of Materials를 생성할 때는 고유한 물리적인 디자이너가 항상 사용됩니다.

► 부품 Annotation 달기에 대해 더 알아보기

파라미터화 된 Multi-Channel 계층적 설계

현재 프로젝트에서 시트 심볼을 회사에서 선호하는 전원 공급 회로와 연결하는 등 설계의 일부를 재사용하는 도전은 부품의 값이 항상 고정되어 있지 않다는 것입니다.

파라미터 계층적 설계는 이를 해결합니다 - 이는 부품 값의 명세를 회로도 시트에서 시트 심볼로 이동시킬 수 있게 해줍니다. 이 기능은 Multi-Channel 설계와 완벽하게 작동하여 각 Channel마다 다른 부품 값을 가질 수 있습니다. 각 Channel이 자체 시트 심볼을 가져야 한다는 점에 유의해야 합니다. 부품 값이 저장되는 곳이기 때문입니다.

예를 들어, 그래픽 이퀄라이저는 같은 회로를 여러 번 반복해서 사용할 수 있으며, 각 Channel마다 유일한 차이점은 부품 값입니다. 따라서 캐패시터는 다른 Channel에서 0.12µF, 0.056µF, 0.033µF와 같은 값을 가질 수 있습니다. 이를 구현하는 것은 간단합니다. 각 Channel을 참조하는 시트 심볼에서 이러한 값을 지정하면 됩니다. 이렇게 하면 부품 값만 다른 유사한 회로도를 여러 개 가지고 있을 필요가 없어집니다.

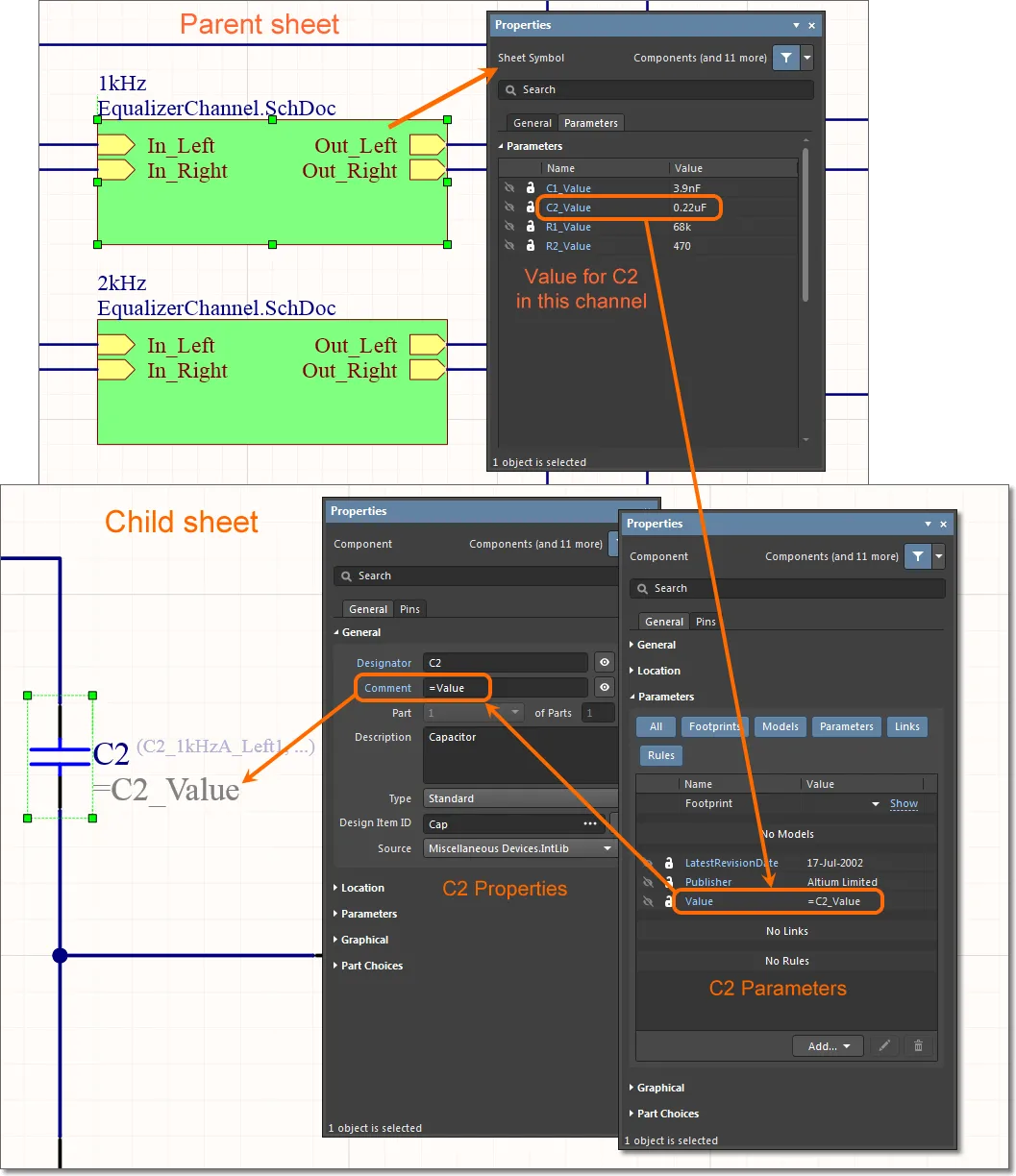

파라미터 부품은 대상 부품에서 해당 파라미터를 참조하는 방식으로 정의됩니다. 아래 이미지는 그래픽 이퀄라이저의 상위 시트를 왼쪽에 보여주며, 1KHz 시트 심볼의 파라미터를 나란히 보여줍니다. 이미지는 또한 하위 수준의 캡처된 회로도와 컴파일된 1KHz Channel(하단 탭에서 선택함)을 보여줍니다.

각 Channel마다 다른 캐패시터와 저항 값이 있는 그래픽 이퀄라이저; 실제 부품 값은 시트 심볼에서 정의되므로 하위 수준의 회로도를 하나만 캡처하면 됩니다.

각각의 시트 심볼 파라미터는 아래 수준의 도면 부품의 파라미터로서도 정의됩니다. 아래 이미지에서 확인할 수 있듯이, 각 시트 심볼 파라미터의 값은 관련 도면 부품으로 전달되어 부품의 코멘트 필드에 매핑됩니다. 만약 값 파라미터가 부품의 코멘트 파라미터가 아닌 부품의 값으로 직접 사용된다면, 유일한 요구 사항은 시트 심볼 파라미터를 부품의 값 파라미터에 매핑하고 가시적으로 만드는 것입니다 (Value=C2_Value).

값 파라미터가 =C2_Value의 값을 가지고 있기 때문에, 컴파일러는 실제 부품 값이 상위 수준의 시트 심볼에서 찾아야 함을 알 수 있습니다.

파라미터 계층은 부품 값에만 국한되지 않습니다. 부품 파라미터 뿐 만 아니라 도면 시트의 다른 객체 텍스트 Label에도 파라미터 적으로 참조할 수 있습니다. 다만 부품 ID, Port 객체 및 문서 파일 이름과 같은 기본 연결 요소는 제외됩니다. 계층 구조에서 여러 시트 위로부터 파라미터를 참조하는 경우, 시스템은 일치하는 파라미터를 찾을 때까지 계층을 검색합니다.