親ページ: チュートリアル - Altium Designerを使った完全な設計プロセス

メインページ: PCB設計ルールリファレンス, PCB設計ルールの定義、範囲設定、および管理

PCBエディタはルール駆動型の環境であり、トラックの配置、コンポーネントの移動、ボードの自動配線など、設計を変更するアクションを実行すると、ソフトウェアが各アクションを監視し、設計が設計ルールにまだ準拠しているかどうかをチェックします。準拠していない場合、そのエラーは直ちに違反として強調表示されます。ボードの作業を開始する前に設計ルールを設定しておくことで、設計のタスクに集中し続けることができ、設計エラーが即座に指摘されることを確信して作業を進めることができます。

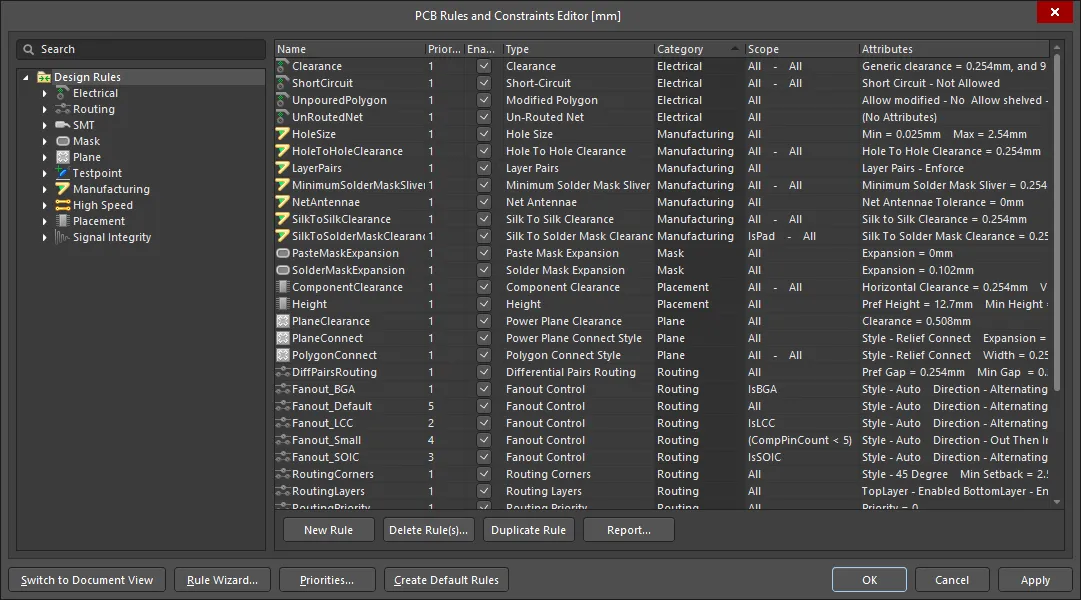

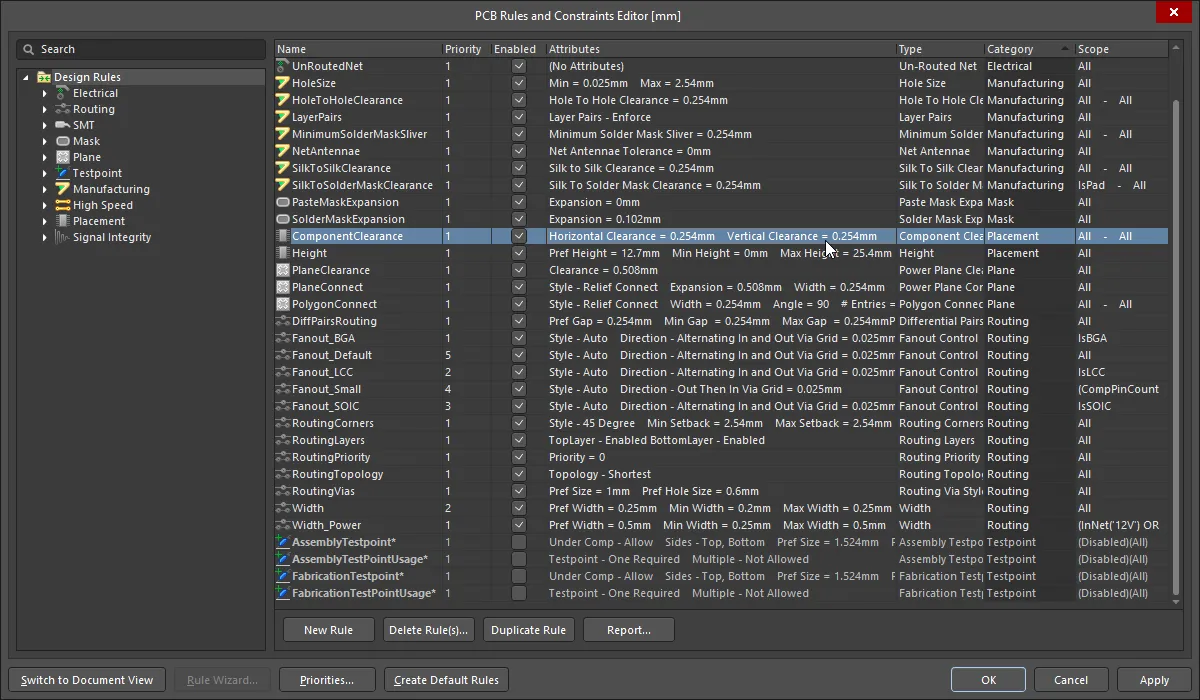

設計ルールは、以下に示すようにPCB Rules and Constraints Editorダイアログで設定されます(Design » Rules)。ルールは10のカテゴリーに分けられ、さらに設計ルールタイプに細分化されます。

すべてのPCB設計要件は、PCBルールと制約エディタでルール/制約として設定されます。

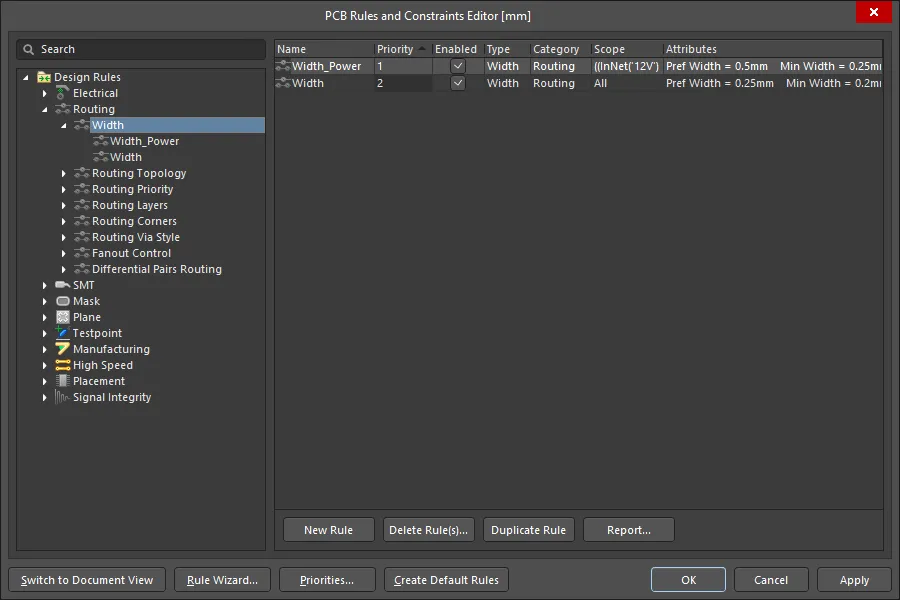

配線幅の設計ルール

設計ルール参照:幅

配線の幅は、適用可能な配線幅設計ルールによって制御されます。このルールは、Interactive Routingコマンドを実行し、ネットをクリックするとソフトウェアによって自動的に選択されます。

ルールを設定する際の基本的なアプローチは、最も多くのネットを対象とする最低優先度のルールを設定し、その後、電源ネットなどの特別な幅要件を持つネットを対象とするより高優先度のルールを追加することです。ネットが複数のルールによって対象とされても問題はありません。ソフトウェアは常に最も高い優先度のルールを探し、それのみを適用します。

たとえば、このチュートリアルの設計には、多数の信号ネットと2つの電源ネットが含まれています。デフォルトの配線幅ルールは、信号ネットに対して0.25mmに設定できます。このルールは、ルールの範囲をAllに設定することで、設計内のすべてのネットを対象とします。Allの範囲が電源ネットも対象とするにもかかわらず、InNet('12V') or InNet('GND')の範囲を持つ、2番目の優先度の高いルールを追加することで、これらを特定的に対象とすることができます。下の画像は、これら2つのルールの要約を示しており、詳細は次の2つの折りたたみセクションの画像に示されています。

2つの配線幅設計ルールが定義されており、優先度の低いルールは全てのネットを対象とし、優先度の高いルールは12VネットまたはGNDネット内のオブジェクトを対象としています。

同じタイプのルールが複数ある場合、PCBエディターはルールの優先度を使用して、適用可能な最高優先度のルールが適用されるようにします。

ルールを追加する場合:

-

新しいルールが追加されると、最高優先度が与えられます。

-

ルールが複製されると、そのコピーには元のルールよりも低い優先度が与えられます。

ダイアログの下部にある

優先度ボタンをクリックして、優先度を変更します。

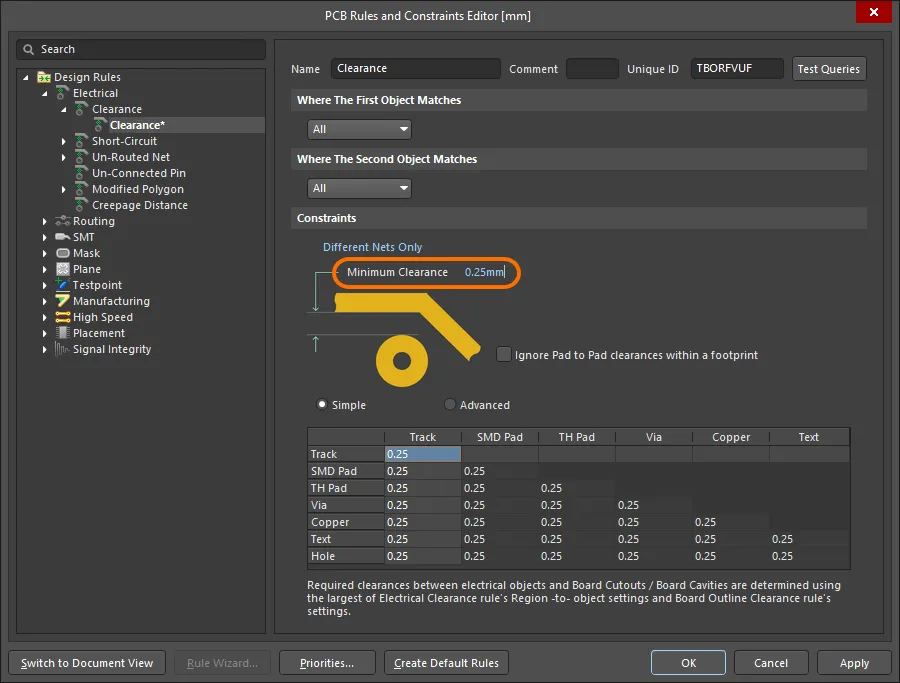

電気的クリアランス制約の定義

設計ルール参照: クリアランス制約

次のステップは、異なるネットに属する電気オブジェクトが互いにどれだけ近くにあることができるかを定義することです。

この要件は、電気的クリアランス制約によって扱われます。チュートリアルでは、全てのオブジェクト間で0.25mmのクリアランスが適切です。

Minimum Clearanceフィールドに値を入力すると、その値がダイアログの下部にあるグリッド領域の全てのフィールドに自動的に適用されることに注意してください。オブジェクトタイプに基づいてクリアランスを定義する必要がある場合にのみ、グリッド領域で編集する必要があります。

電気クリアランスの制約はオブジェクト間で定義されます。全てのオブジェクト種を表示するには、制約を高度に切り替えます。

電気クリアランス制約には最初のオブジェクトが一致する場所と二番目のオブジェクトが一致する場所の二つのオブジェクト選択フィールドがあることに注意してください。これは二項ルールであるためです。つまり、二つのオブジェクト間に適用されるルールです。

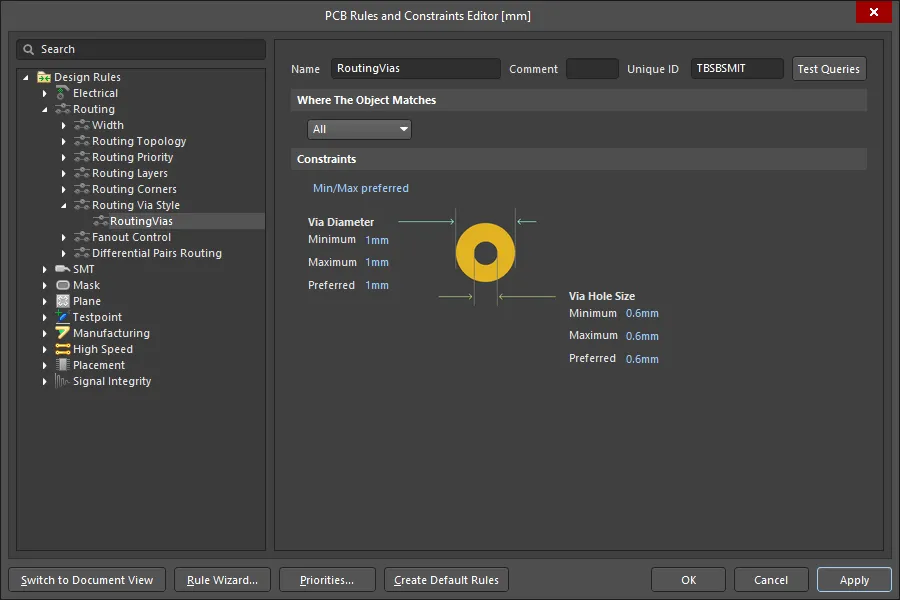

ルーティングビアスタイルの定義

設計ルール参照: ルーティングビアスタイル

レイヤーを変更しながらルーティングする際、ビアは自動的に追加されます。この状況では、ビアのプロパティは適用されるルーティングビアスタイル設計ルールによって定義されます。もしPlaceメニューからビアを配置する場合、その値は内蔵のデフォルトプリミティブ設定によって定義されます。このチュートリアルでは、ルーティングビアスタイル設計ルールを設定します。

この設計では、全てのネットに対して単一のルーティングビアが適しています。

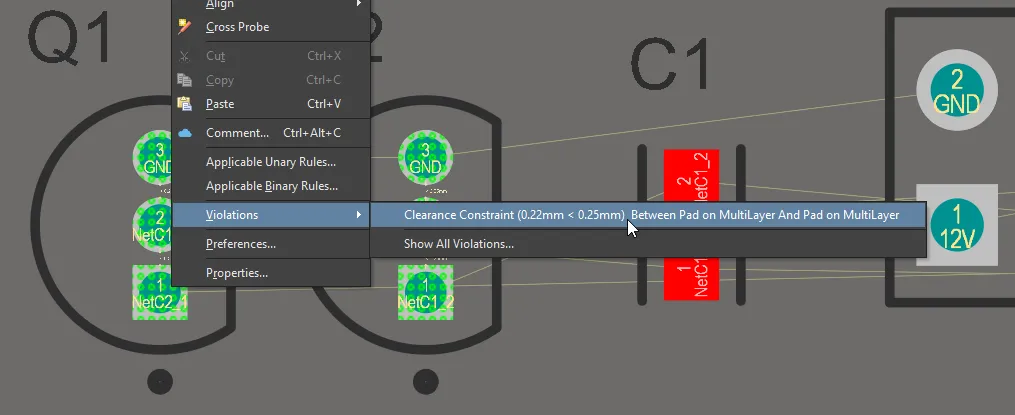

既存の設計ルール違反

トランジスタのパッドに違反が表示されていることに気づいたかもしれません。違反の上で右クリックし、以下に示すように右クリックメニューのViolationsを選択します。詳細には以下のように表示されます:

-

クリアランス制約の違反

-

マルチレイヤー上のパッドと、マルチレイヤー上のパッドの間

-

クリアランスが0.22mmで、指定された0.25mmより少ない

違反を右クリックして、どのルールに違反しているか、および違反条件を調べます。この画像では、表示がシングルレイヤーモードで、アクティブレイヤーとしてトップレイヤーが設定されています。

この違反については、間もなく議論され、解決されます。違反マーカーが気になる場合は、Tools » Reset Error Markersコマンドを実行することでクリアできます。このコマンドはマーカーをクリアするだけで、実際のエラーを隠したり削除したりするわけではありません。次にオンラインDRCを実行する編集アクション(コンポーネントの移動など)を行うか、バッチDRCを実行すると、エラーは再びフラグが立てられます。

設計ルールの確認

ソフトウェアによって作成されたデフォルトの新しいボードには、すべての設計で必要ではないルールが含まれており、多くの他の設計ルールは、設計の要件に合わせて調整する必要があります。このため、設計ルールを確認することが非常に重要です。これは、PCBルールと制約エディタで行うことができます。左側のツリーの上部でDesign Rulesを選択し、Attributes列をすべてスキャンして、値を調整する必要があるルールをすぐに見つけ出してください。

デフォルトのボードはインペリアル単位も使用しています。もしボードがメトリックを使用している場合、はんだマスクの膨張など多くのルール値が、4milのような丸められた値から0.102mmへ、または最小はんだマスクスリバーのデフォルトが10milから0.254mmへ変更されるでしょう。たとえば、0.002mmのような最も小さい桁は出力生成においては無視できるものですが、それが気になる場合はデザインルール内でこれらの設定を編集できます。

デザインルールをレビューする際、必要に応じて列の順序を変更できることに注意してください。

新しいボードを作成すると、デザインに必要のないデフォルトの設計ルールが含まれることがあります。たとえば、新しいボードを作成するときに含まれる組立および製造テストポイントタイプの設計ルールは、このデザインでは不要です。

-

開いていない場合は、PCBルールと制約エディタを開きます。

-

テストポイントカテゴリをクリックし、四つのテストポイントタイプルールを無効にします(有効列のチェックボックスをクリアします)。これを行わないと、チュートリアルの後半でテストポイント違反が発生します。

デザインルールは、.RULファイルにエクスポートして保存し、将来のPCBデザインにインポートすることもできます。これを行うには、PCBルールと制約エディタの左側のツリーで右クリックして、デザインルールを選択ダイアログを開きます。標準のWindows選択技術を使用してエクスポートしたいルールを選択し、OKをクリックして選択したルールをエクスポートします。