このページでは、シグナルインテグリティ(SI)解析の実行について説明します。設計ルールやシグナルインテグリティモデルのような設計パラメータの設定、回路図とPCBエディタからのシグナルインテグリティの起動、ネットスクリーニング解析に使用されるテストの設定、選択されたネット上でのさらなる解析の実行、信号線の終端、設定の好みと結果の波形との作業についてカバーしています。

Altium Designerを使用すると、回路図またはPCBエディタからPCBのシグナルインテグリティ性能を解析し、事前に定義されたテストに対してネットスクリーニング結果を評価し、選択されたネットに対して反射とクロストーク解析を実行し、SimDataエディタで波形を表示および操作することができます。

シグナルインテグリティ解析機能は、デフォルトではAltium DesignerにインストールされていないSignal Integrity Analysisシステム拡張を通じて利用可能です。この拡張機能は、Altium DesignerのExtensions and Updatesページからインストール/削除または更新できます(システムユーザーメニューからExtensions and Updatesオプションを選択します -  )。インストールされていない場合、Signal Integrity Analysis拡張機能はPurchasedタブ内にあります。カーソルを拡張機能の上に置き、そのエントリの右上にある

)。インストールされていない場合、Signal Integrity Analysis拡張機能はPurchasedタブ内にあります。カーソルを拡張機能の上に置き、そのエントリの右上にある アイコンをクリックします。

アイコンをクリックします。

► Altium Designer拡張機能のインストールと管理についての詳細は、インストールの拡張と更新を参照してください。

シグナルインテグリティの概要

Altium Designerには、プレレイアウトおよびポストレイアウトのシグナルインテグリティ解析機能が含まれています。Altium Designerのシグナルインテグリティアナライザーは、洗練された伝送線計算とI/Oバッファマクロモデル情報をシミュレーションの入力として使用します。高速反射およびクロストークシミュレーターモデルに基づいて、シグナルインテグリティアナライザーは、業界で実証されたアルゴリズムを使用して正確なシミュレーションを生成します。

最終的なボードレイアウトと配線に先立って、ソース回路図から予備的なインピーダンスおよび反射シミュレーションを実行できます。これにより、ボードレイアウトを確定する前に、ネットインピーダンスの不一致などの潜在的なシグナルインテグリティ問題に対処できます。

最終ボード(または部分的に配線されたボード)に対して、インピーダンス全体、信号反射、クロストーク解析を実行して、設計の実世界でのパフォーマンスをチェックできます。信号完全性スクリーニングは、Altium Designerの設計ルールシステムに組み込まれており、通常のボードDRC(設計ルールチェック)プロセスの一部として信号完全性違反をチェックできます。信号完全性の問題が見つかった場合、Altium Designerはさまざまな終端オプションの効果を示し、設計を変更する前に最適な解決策を見つけることができます。

回路図のみのプロジェクトから信号完全性解析を実行する

プロジェクトの一部としてPCBがない場合でも、回路図のみを使用して設計に対して信号の完全解析を実行できます。回路図はプロジェクトの一部でなければならず、Free Documentsとして開かれたドキュメントでは解析は実行されません。配線されたネットがこの解析に必要なため、クロストーク解析は利用できません。

回路図のみモードで実行する場合、デフォルトの平均トラック長とインピーダンスは、シグナルインテグリティ設定オプションを使用して定義できます。シグナルインテグリティアナライザーは、回路図から反応ネットと供給ネットのためのPCB設計ルールも読み取ります。これらのルールは、回路図内のネットにPCBレイアウト指示またはパラメータセット指示として追加できます。

回路図エディターで、回路図を開いた状態で、メニューからTools » Signal Integrityを選択します。これにより、必要なシグナルインテグリティモデルを設定し、その後Signal Integrityパネルが表示され、初期結果を表示したり、さらなる解析を実行したりできます。

PCBプロジェクトからシグナルインテグリティ解析を実行する

PCBドキュメントからシグナルインテグリティ解析を実行する場合、PCBは関連する回路図と共にプロジェクトの一部でなければなりません。プロジェクト内の任意の回路図ドキュメントからシグナルインテグリティを実行しても、PCBから実行するのと同じ効果が得られることに注意してください。これにより、反射とクロストーク解析の両方を実行できます。

PCBエディターから、Tools » Signal Integrityを選択すると、上記で説明した回路図のみのモードと同じプロセスを進めます。

これで、PCBに回路図のコンポーネントがいくつか(またはなし)含まれていても、配置されたものはすべてコンポーネントリンクでリンクされている必要があります。これは、Project » Component Linksを選択することで確認できます。また、配線されていないネットは、解析目的でトラック長の推定値を計算するためにピン間のマンハッタン距離を使用します。

シグナルインテグリティを実行する前に

設計のシグナルインテグリティ解析を成功させ、正確な結果を得るためには、解析を実行する前に以下の作業を行う必要があります。

-

各ネットはネットとインピーダンスデータを提供するためにスクリーニングできますが、すべてのネットが信号整合性特性(電圧とタイミング)について解析されるわけではありません。すべての特性のスクリーニングを成功させるためには、ネットには少なくとも1つの出力ピンを持つICが含まれていなければならず、他のコンポーネントは含まれていません。例えば、抵抗器、コンデンサ、インダクタは、駆動源を提供する出力ピンがないため、それ自体はシミュレーション結果を提供しません。双方向ネットがスクリーニングされる場合、両方向がシミュレートされ、最悪の結果が表示されることに注意してください。

-

各コンポーネントに関連するSignal Integrity Model タイプは正しくなければなりません。これは、Signal Integrity Model Assignmentsダイアログを使用するか、回路図ソースドキュメントに配置されたコンポーネントに関連付けられたSignal Integrity Model を編集する際に、Signal Integrity Model ダイアログのタイプフィールドに正しいエントリを手動で設定することで達成されます。このエントリが定義されていない場合、Signal Integrity Model Assignmentsダイアログは、その特性に基づいてコンポーネントのタイプを推測しようとします。このエントリが定義されていない場合、タイプは統合回路と仮定されます。詳細については、Signal Integrity Model Assignmentsダイアログを使用したSIモデルの追加を参照してください。

-

電源ネットの設計ルールが必要です。一般に、電源ネット用とグラウンドネット用の少なくとも2つのルールが必要です。これらのスコープは、ネットまたはネットクラスのいずれかになります。電源ネットは信号整合性を解析できません。詳細については、回路図の信号整合性設計ルールまたはPCBの信号整合性設計ルールを参照してください。

-

信号反応の設計ルールを設定できます。デフォルトの反応を上書きしたい場合にのみ、反応ルールが必要ですので、一般的には必要ありません。

-

PCBのレイヤースタックが正しく設定されている必要があります。信号整合性アナライザーは連続した電源プレーンを要求します。分割プレーンはサポートされていないため、プレーンに割り当てられたネットが使用されます。存在しない場合は、仮定されるので、それらを追加して適切に設定する方がはるかに良いです。ボードのすべての層、コア、プレプレグの厚さも正しく設定されている必要があります。PCBエディタでレイヤースタックを設定するには、Design » Layer Stack Managerコマンドを使用します。回路図のみモードで信号整合性を実行する場合、デフォルトで2層ボードと2つの内部プレーンが使用されます。より多くの制御が必要な場合は、レイヤースタックが設定された空のPCBを作成できます。レイヤースタックの定義ページで詳細を学ぶことができます。

信号の特性、例えば電圧レベルは、テスト中のネットの出力ピンに割り当てられたモデルによって決定されます。ピンモデルは、コンポーネントモデル割り当てプロセスの一部として割り当てられ、これらのコンポーネントレベルのモデル割り当ては、回路図を更新することで保持されます。個々のピンモデルも、たとえばシグナルインテグリティパネルでピンをダブルクリックすることによって上書きすることができますが、これらのピンレベルの再割り当ては編集セッション間で保持されません。 Signal Integrity Model Assignmentsダイアログを使用してSIモデルを追加する デザインにシグナルインテグリティモデルを追加する最も簡単な方法は、Signal Integrity Model Assignmentsダイアログを使用することです。

-

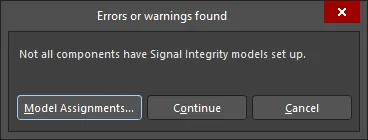

メニューからTools » Signal Integrityを選択します。プロジェクトでシグナルインテグリティを始めたばかりで、シグナルインテグリティモデルが添付されていないコンポーネントがある場合、Errors or warnings foundダイアログが表示されSignal Integrity Model Assignmentsダイアログを使用してモデルの割り当てを設定するように促されます。

Errors or warnings foundダイアログ

Signal Integrity Model Assignmentsダイアログ

また、ContinueをクリックしてSignal Integrityパネルが表示されている場合、パネル内のModel Assignmentsボタンをクリックすることで、いつでもSignal Integrity Model Assignmentsダイアログに入ることができます。これを行うと、モデル割り当ての変更により既存の結果が無効になるため、すべての結果がクリアされて再計算されることに注意してください。

すべてのコンポーネントに対してモデルが既に設定されている場合、SI Setup Optionsダイアログが表示されます。SI設定オプションの設定については、詳細をご覧ください。

-

Errors or warnings foundダイアログでModel Assignmentsをクリックすると、Signal Integrity Model Assignmentsダイアログが表示されます。

Signal Integrity Models Assignmentダイアログを実行すると、Signal Integrity Model を含まない各コンポーネントに必要なSignal Integrity Model を推測しようとします。モデルが既に定義されているコンポーネント(およびモデル情報)を含むすべてのコンポーネントがSignal Integrity Models Assignmentダイアログに表示されます。各コンポーネントには、次の表で説明されているステータスが割り当てられます。

| ステータス |

定義 |

| 一致なし |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントを特定のタイプにリンクする特性を見つけることができませんでした。ユーザーが正しく設定するために変更が必要になる可能性が高いです。 |

| 低信頼度 |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントのタイプを選択しましたが、強い根拠はありませんでした。 |

| 中信頼度 |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントのタイプを選択し、その推測には合理的な自信があります。 |

| 高信頼度 |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントのタイプを選択し、通常このタイプのコンポーネントに関連付けられる特性のほとんどに適合しています。 |

| モデル見つかる |

このコンポーネントの既存のモデルが見つかりました。 |

| ユーザーによる変更 |

ユーザーがSignal Integrity Model Assignmentsダイアログの初期推測から変更した場合、コンポーネントはこのステータスに変わります。 |

| モデル追加 |

ユーザーがSignal Integrity Model Assignmentsダイアログを使用して回路図ドキュメントを変更し、新しいモデルを保存した場合に使用されるステータスです。 |

Signal Integrity Model Assignmentsダイアログを使用したコンポーネントモデルの変更

-

モデルを変更したいコンポーネントを選択します。

-

正しいタイプを選択します。シグナルインテグリティ用のコンポーネントには、抵抗器、コンデンサ、インダクタ、ダイオード、BJT、コネクタ、ICの7種類があります。各コンポーネントのタイプは、Type列のドロップダウンまたは右クリックメニューから選択できます。

-

抵抗器、コンデンサ、インダクタの値を設定します。可能であれば、Signal Integrity Model Assignmentsダイアログは、コンポーネントのコメントフィールドとパラメータに基づいてこの列にコンポーネントの正しい値を配置しようとします。これに変更が必要な場合(または存在しない場合)は、この時点で行う必要があります。抵抗器アレイなどの部品アレイの特別なケースは、列内をクリックすることでアクセスできる別のダイアログを通じて行われます(詳細については、コンポーネントにシグナルインテグリティモデルを手動で追加するを参照してください)。

-

コンポーネントがICの場合、技術タイプの選択が重要です。これにより、シミュレーションで使用されるピンモデルの特性が決まります。これは、Value/Type列のドロップダウンリストを介して選択するか、右クリックメニュー(Change Technology)を通じてアクセスできます。

-

最後に、Signal Integrity Model Assignmentsダイアログで許可されている以上の詳細を指定する必要がある場合があります。これは、IBISモデルなどの場合です。これは、右クリックメニューからAdvancedを選択することで実現できます。このプロセスの詳細については、コンポーネントにシグナルインテグリティモデルを手動で追加するを参照してください。

モデルの保存

いずれかまたはすべてのコンポーネントに対してモデルが選択されたら、その情報を保存するために回路図ドキュメントを更新できます。

-

Signal Integrity Model Assignmentsダイアログで更新されるすべてのコンポーネントのUpdate Schematic列をチェックします。その後、Update Models in Schematicボタンをクリックします。

-

選択された各コンポーネントに対して、新しいSignal Integrity Model (または既存のものの変更)が回路図ドキュメントに追加されます。回路図ドキュメントは後で保存する必要があります。

信号整合性解析プロセスを進めるためにモデルを保存する必要はありません。モデルが保存されない場合、解析はSignal Integrity Model Assignmentsダイアログに現在表示されている通りのすべてのモデルで進行します。しかし、次に信号整合性ツールを使用する際には、いかなる変更も失われていることになります。

コンポーネントに手動で信号完全性モデルを追加する

回路図コンポーネントに信号完全性モデルを追加するには:

-

回路図エディターで配置されたコンポーネントの場合 - コンポーネントを選択し、Propertiesパネルを開きます。

-

回路図シンボルエディターで編集中のコンポーネントの場合 - SCH Libraryパネルでそのエントリを選択してアクティブにし、Propertiesパネルを開きます。

PropertiesパネルのParameters領域でAddボタンをクリックし、Signal Integrityを選択します。Signal Integrity Model ダイアログが開きます。

モデルを設定して、OKをクリックしてください。

受動部品の設定

抵抗やコンデンサなどの部品を設定する場合、通常はタイプと値を入力するだけで十分です。値はValueフィールドに入力でき、全体のコンポーネントのパラメータとして設定できます。

抵抗アレイのようなコンポーネントもサポートされています。これは、コンポーネントタイプを選択した後、Signal Integrity Model ダイアログでSetup Part Arrayボタンをクリックすることで実現できます。Part Array Editorダイアログでは、ピン間の接続やそれらの接続の値/モデルを設定できます。

Part Array Editorダイアログ

ICの設定

ICタイプモデルを設定する際には、いくつかの代替方法があります。

IBISファイルのインポート

もう一つの重要なオプションは、IBISファイルをインポートする機能です。

-

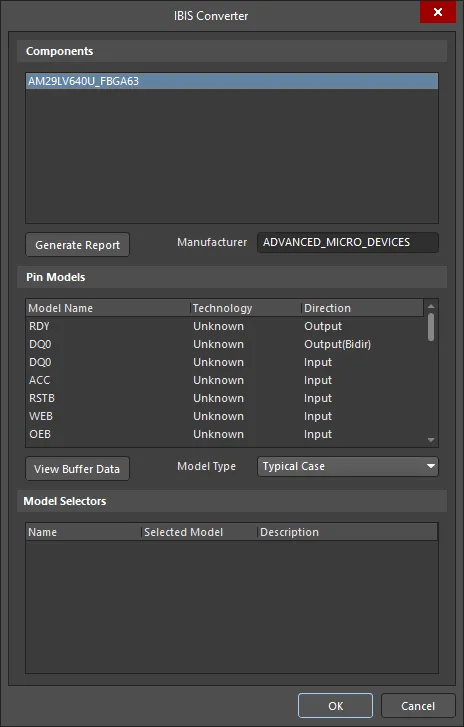

ICモデルの入出力特性を指定するためにIBIS(Input/Output Buffer Information)ファイルを使用するには、Signal Integrity Model ダイアログでImport IBISボタンをクリックします。Import IBISダイアログからIBISファイルを選択し、開くをクリックします。IBIS Converterダイアログが表示されます。

IBISコンバーターダイアログ

-

IBISファイルに含まれる必要なコンポーネントを選択します。Altium DesignerはIBISファイルを読み込み、IBISファイルからピンモデルをインストール済みのピンモデルライブラリにインポートします。重複するモデルが見つかった場合、既存のモデルを上書きするかどうか尋ねられます。さらに、コンポーネント上のすべてのピンには、IBISファイルで指定された通りの適切なピンモデルが割り当てられます。

-

どのピンが成功して、どのピンが失敗したかを示すレポートが自動的に生成されます。上記のように、適切なピンに対して手動でモデルを選択することにより、さらなるカスタマイズが可能です。

-

OKをクリックして、IBIS情報のインポートを完了し、Signal Integrity Model ダイアログに戻ります。

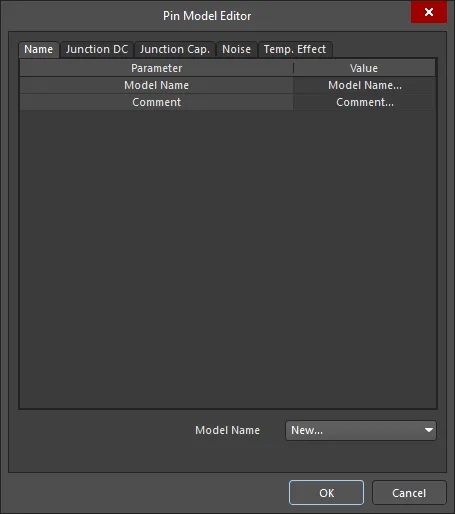

ピンモデルの編集

そのピンのさまざまな電気特性を指定することで、既存のピンモデルを追加または編集することが可能です。この機能は、BJT、コネクタ、ダイオードなどの他のタイプにも利用可能です。

-

ピンモデルを変更するには、そのタイプで利用可能な場合、Signal Integrity Model ダイアログのAdd/Edit Modelボタンをクリックします。ピンモデルエディタダイアログが表示されます。

Pin Model Editorダイアログ

-

Model NameのドロップダウンリストでNewをクリックします。

-

必要な変更を行い、OKをクリックします。

-

これが新しいピンモデルの場合、そのモデルはこの(および他の)コンポーネントのピンで選択できるようになります。

IBISモデル実装エディタの使用

Altium Designerのシグナルインテグリティモデル形式(SIマクロモデルと呼ばれる)を使用できず、専用のIBISモデルが必要なサードパーティツールをサポートするために、Altium Designerは専用のIBISモデル実装エディタを組み込んでいます。これにより、IBISモデルを回路図コンポーネントに添付できます。したがって、以下のいずれかを行うことができます:

-

シグナルインテグリティ解析中にIBISピンモデルをコンポーネントピンにインポートし(上記のようにAltium Designer SIマクロモデルとして保存)、または

-

以下に説明するように、IBISモデルを回路図コンポーネントに添付します。

この機能は、バージョン4.0を含むすべてのバージョンのIBISモデル仕様をサポートしています。

回路図コンポーネントにIBISモデルを追加するには:

-

回路図エディターで配置されたコンポーネントについて - コンポーネントを選択し、Propertiesパネルを開きます。

-

回路図シンボルエディターで編集中のコンポーネントについて - SCH Libraryパネルでそのエントリを選択してアクティブにし、Propertiesパネルを開きます。

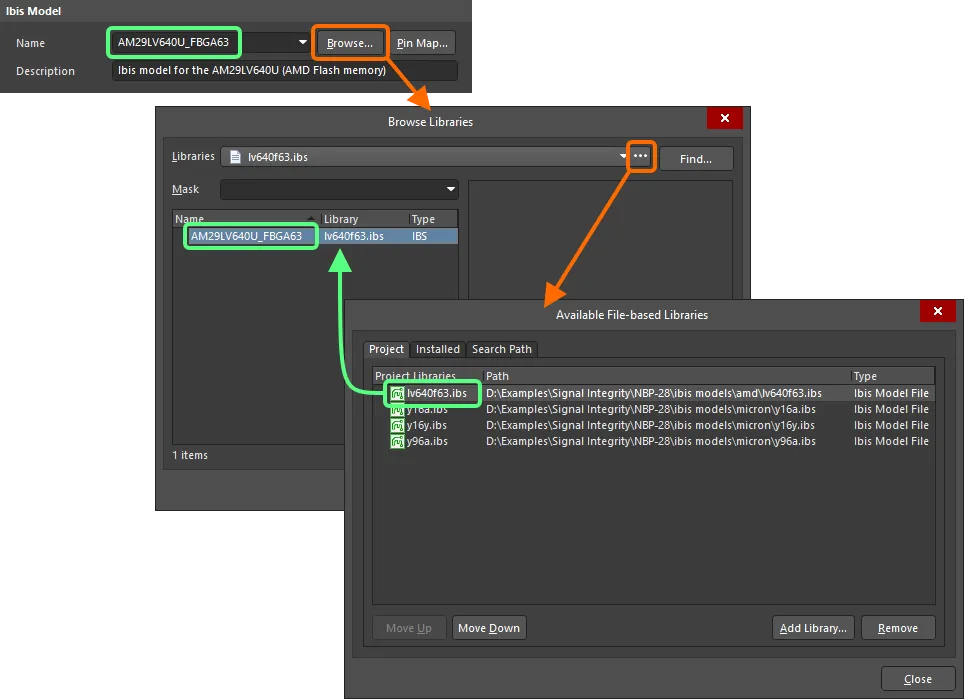

PropertiesパネルのParameters領域でAddボタンをクリックし、Ibis Modelを選択します。IBIS Model ダイアログが開きます。

回路図コンポーネントに対して、IBISモデルのリンクは複数定義できますが、アクティブなモデルは一度に1つだけです。

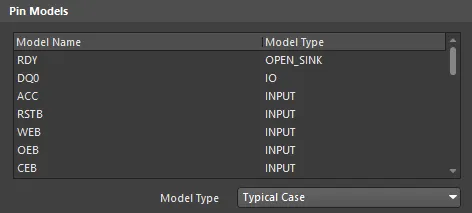

IBISモデル

モデルの名前を指定します - .ibsファイル内での正確な名前と同じように - そして、このドメインでの実装を説明する意味のある名前をモデルリンクに付けてください。

また、特に名前がわからない場合は、Browseボタンを使用してBrowse Librariesダイアログにアクセスします。このダイアログを使用して、現在利用可能なライブラリ全てにわたるIBISモデルファイルを参照します。必要なモデルファイルが現在利用可能なライブラリに含まれていない場合は、このダイアログのFind機能を使用してください。

モデルの名前を直接指定するか、またはそれを参照してください。

IBISファイルを参照する際、名前ドロップダウンはそのファイル内で定義されている全てのモデルを名前で表示します。必要なものを単に選択してください。

回路図コンポーネントのピンとIBISモデルのピンのマッピングは、Pin MapボタンをクリックしてアクセスするModel Mapダイアログで定義されます。

モデルマップダイアログでコンポーネントとモデルのピンマッピングを確認します。

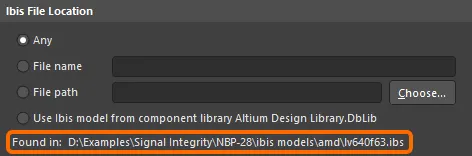

IBISファイルの場所

モデル名が定義されている場合に、ソフトウェアがモデルをどのように位置づけるかを指定するオプションがIBISモデルダイアログのこの領域に用意されています:

-

Any - 利用可能なすべてのライブラリ(プロジェクトライブラリ、インストールされたライブラリ、および定義された検索パスで見つかったライブラリ)がモデルを探すために使用されます。

-

File name - モデルが存在する完全なファイル名を入力してください(例:

lv640f63.ibs)。利用可能なすべてのライブラリがモデルを探すために使用されます。ここで見つからない場合は、デフォルトのライブラリパス(PreferencesダイアログのSystem – Default LocationsページのLibrary Pathフィールド)が調べられ、指定されたファイルがそこにあるかどうかが確認されます。

-

File path - ファイルの完全なパス/名前を入力してください。Chooseボタンをクリックしてファイルを参照します。このオプションは、ファイルがそのディレクトリに残っている限り、モデルを常に見つけることができます(明示的であるため)。

-

Integrated/Database Library - 配置後、コンポーネントが統合またはデータベースライブラリから配置された場合、そのライブラリが利用可能なライブラリセットの一部である限り、同じライブラリから直接モデルを取得できます。

モデルが正常に見つかった場合、そのモデルが見つかった場所の表示がされます。

IBISモデルの検索方法を指定します。

ピンモデル

このダイアログの領域では、選択されたIBISモデルに定義されているピンモデルのリストが表示専用で表示されます。ただし、Model TypeをデフォルトのTypical Caseから、Strong CaseまたはWeak Caseに変更することができます。

選択したIBISモデルのピンモデル。

モデルセレクタ

Model Selectors領域は、選択したIBISモデルにモデルセレクタが含まれている場合に表示されます。これにより、使用するモデルを選択できます(例えば、ピンには異なる電圧レベルのモデルがあるかもしれません;3.3V、5Vなど)。

定義されたモデルセレクタを持つ例示的なIBISモデル。

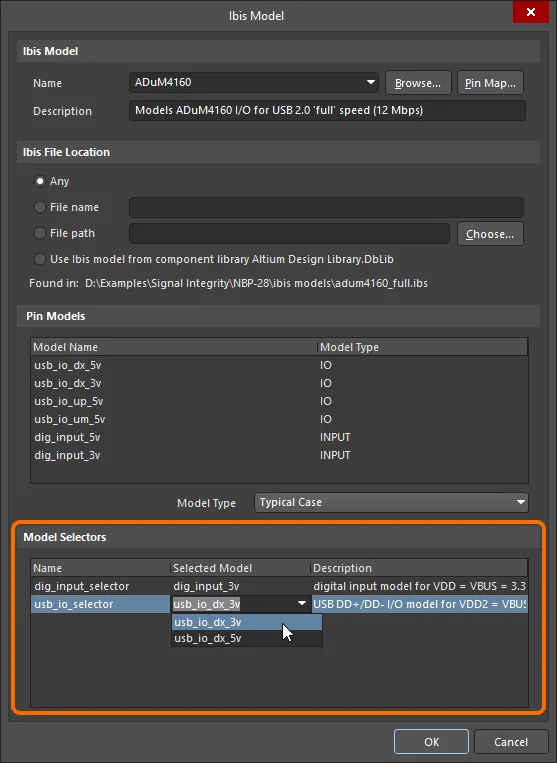

回路図における信号完全性設計ルール

信号完全性に関するPCB特有の設計ルールは、パラメータとして追加される場合、回路図内で定義することができます。

電源ネット設計ルール

シグナルインテグリティ解析のために、パラメータセットディレクティブを使用して、供給ネットとその電圧を識別するためのPCBルールを追加する必要があります。回路図に供給ネットの設計ルールを追加するには:

-

パラメータセットディレクティブ(Place » Directive » Parameter Set)を適切なネットに配置します。

-

配置されたディレクティブが選択されたら、PropertiesパネルのParameters領域でAddボタンをクリックし、ドロップダウンメニューからRuleを選択します。

-

デザインルールタイプの選択ダイアログが開き、ルールタイプを選択できます。スクロールダウンしてSignal Integrityルールを選び、Supply Netsを選択してからOKをクリックします。

-

Edit PCB Rule (From Schematic) - サプライネットダイアログが表示されます。このサプライネットの電圧を入力し、OKをクリックします。ルールエントリがPropertiesパネルにリストされます。

シグナルインテグリティ設計ルールは、パラメータセットディレクティブを使用して回路図内に直接追加することができます。

設計をPCBレイアウトに転送した後、そのルールはPCB設計ルールに追加されます(PCB Rules and Constraints Editor ダイアログからアクセスできるPCBエディタ内で表示および編集可能です。このダイアログは、Design » Rules コマンドを使用してアクセスします)。

回路図エディタでは、ルールの対象範囲(ルールがターゲットとするオブジェクトのセット)は、パラメータが追加される場所によって定義されます。例えば、ワイヤーやピン上です。PCBエディタでは、ルールの対象範囲はルール自体内で定義されます。

信号反応設計ルール

回路図エディタ内から設定できるもう一つの設計ルールは、信号反応ルールです。このルールを実行すると、解析されているネット上の各出力ピンの反応が挿入されます。これには「all」というスコープを使用する設計ルールが必要なので、このルールのためにシートパラメータを作成する必要があります。このルールを設定しない場合、デフォルトのルールオプションが使用されます。

-

回路図シートでオブジェクトが選択されていない場合、Propertiesパネルを開きます。パネルのParametersタブで、Ruleボタンをクリックし、ドロップダウンメニューからルールを選択します。

-

Choose Design Rule Typeダイアログが開き、ルールタイプを選択できます。スクロールダウンしてSignal Integrityルールを選び、Supply Netsを選択してからOKをクリックします。

-

Edit PCB Rule (From Schematic) - Signal Stimulusダイアログが表示されます。反応の種類、開始レベル、時間を選択してからOKをクリックします。ルールエントリーがPropertiesパネルにリストされます。

シグナルインテグリティ設計ルールは、回路図シートのパラメータとして追加できます。

PCBにおけるシグナルインテグリティ設計ルール

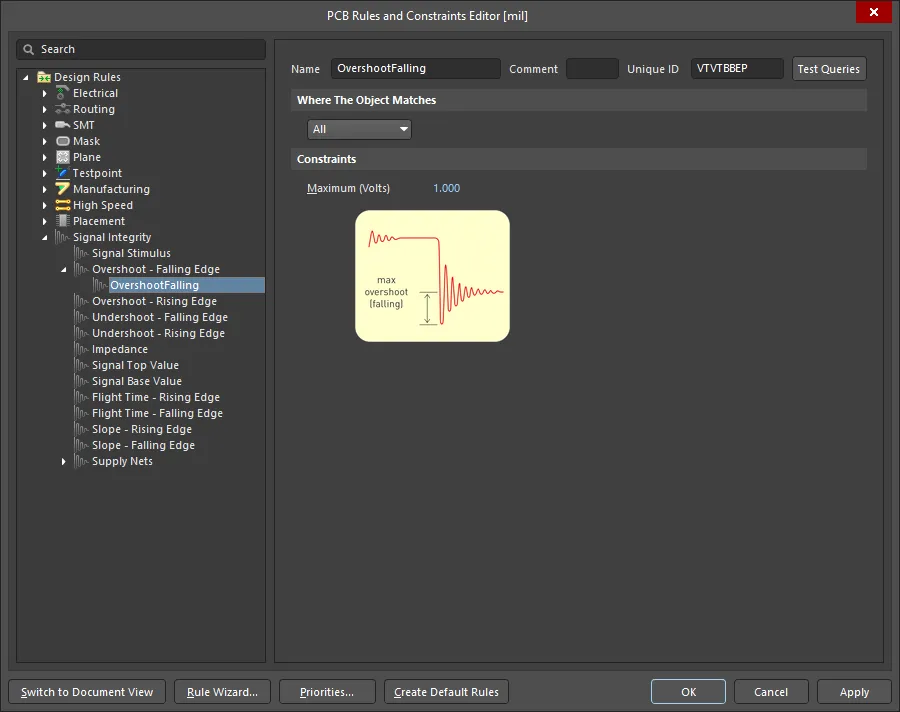

オーバーシュート、アンダーシュート、インピーダンス、信号勾配要件などのシグナルインテグリティパラメータは、標準のPCB設計ルールとして指定できます。Design » RulesをPCBエディタで選択し、PCBルールと制約エディタダイアログにアクセスしてこれらのルールを設定できます。これらのルールは、回路図エディタでパラメータを使用して設定することもでき、設計をPCBレイアウトに転送した後、PCB Rules and Constraint Editorダイアログに表示されます。

オーバーシュート - 落下エッジ設計ルールを閲覧する際のPCB ルールと制約エディタダイアログ

これらのルールには2つの目的があります。1つ目は、PCB内で標準のDRCチェックを実行する際に、ボードがこれらのルールに対して標準的なスクリーニング解析を使用してチェックされることです。2つ目の用途は、Signal Integrityパネルを使用する場合です。これらのルールはテストとして設定および有効化され、どのネットがどのテストに失敗したかをパネルがグラフィカルに表示します。

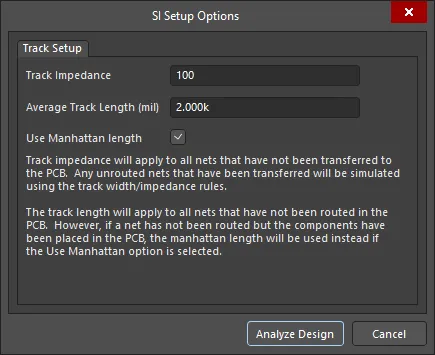

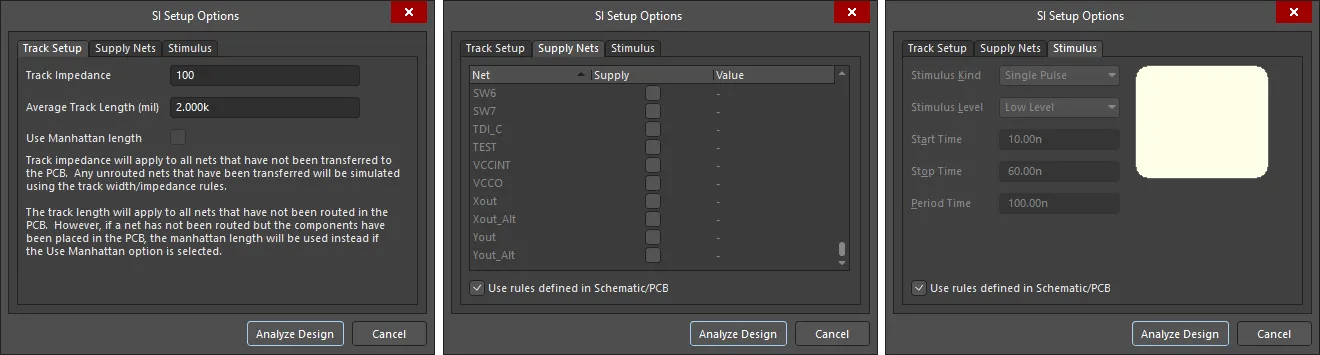

SI設定オプションの構成

Tools » Signal Integrityを選択し、すべてのコンポーネントにモデルが割り当てられている場合、プロジェクトを開いてこのコマンドを初めて実行すると、SI設定オプションダイアログが表示されます。

SI設定オプションダイアログ

-

トラックのインピーダンスと平均トラック長を必要に応じて設定してください。これらの配線特性は、PCBにまだ転送されていないネットやPCB内の未配線ネットがある場合にのみ必要です。

回路図専用モードでは、Supply NetsとStimulusタブのみが表示されることに注意してください。

-

設計の解析をクリックして、初期のデフォルトスクリーニング解析を実行し、Signal Integrityパネルを表示します。そこからさらに、反射またはクロストークのために解析するネットを選択できます。

デフォルトの許容ルール4つと、回路図またはPCBに設定された信号完全性ルールは、設計が初めて解析されるときにすべて有効になり、実行されます。これらの許容値は、Signal IntegrityパネルでMenuボタンをクリックし、許容値の設定を選択することで後から設定できます。

回路図のみモードでのシグナルインテグリティ設定オプション

プロジェクトにPCBが存在しない場合、シグナルインテグリティパネルのMenuボタンをクリックして、いつでもSI設定オプションを変更できます。Setup Optionsを選択すると、SI Setup Options dialogダイアログが表示されます。

Track Setupタブでは、シミュレーション時のトラックのデフォルト長を設定できます。これはPCBが存在する場合には使用されません。なぜなら、PCBは幅のルールを使用するからです。例えば、Use Manhattan lengthオプションが無効の場合、PCBはこの値を使用します。このタブでTrack Impedanceも設定します。

Supply NetsとStimulusタブをクリックすると、ネットとスティミュラスのルール情報を表示して有効にできます。これらのタブは、PCBや回路図上でルールを提供する通常の方法以外に、これらの特性を定義するための別のインターフェースを提供します。

回路図のみモードでアクセスした際のSI Setup Optionsダイアログのタブ

シグナルインテグリティパネルの使用

初期設定を行った後、シグナル・インテグリティパネルは、実行されたばかりのスクリーニング解析からのデータで読み込まれます。この解析の結果と、さまざまなテストに合格したネットが左側のパネルのリストに表示されます。問題のあるネットは、高速反射とクロストーク解析を実行することで、さらに詳細に解析することができます。仮想終端を追加する機能により、これらの問題領域を解決するために設計に追加する必要がある追加の回路を特定でき、したがって最も効率的なシグナル・インテグリティ性能を得ることができます。

シグナル・インテグリティパネルは、シグナル・インテグリティ解析プロセスを設定および制御するために使用されます。

スクリーニング結果の表示

初期スクリーニング解析は、多くのネットを迅速にシミュレーションして、より多くの情報を得て、詳細な反射やクロストーク解析など、より詳細な検査が必要な重要なネットを特定することを可能にします。左側のリストには、この解析の結果が表形式で表示されます。設計内の各ネットについて、次の列情報が表示されます:

ネット

|

ネット名とその状態のグラフィカルな表現。この列は常に表示されます。

|

状態

|

ネットのスクリーニング解析状態のテキスト表現。この列はデフォルトで表示されます。

|

解析エラー

|

ネットが解析できない理由に関する情報。

|

基準値

|

ネット上の信号が低状態で安定する電圧。

|

下降エッジの飛行時間

|

ネット上の信号がしきい値電圧まで下がるのにかかる時間、参照負荷(出力に直接接続されたもの)がしきい値電圧まで下がるのにかかる時間を差し引いた時間。

|

下降エッジのオーバーシュート

|

信号の下降エッジにおける最大オーバーシュート(基準値以下のリンギング)。この列はデフォルトで表示されます。

|

下降エッジの勾配

|

ネット上の信号がしきい値電圧(VT)から有効な低電圧(VIL)まで下がるのにかかる時間。

|

下降エッジのアンダーシュート

|

信号の下降エッジにおける最大アンダーシュート(基準値以上のリンギング)。この列はデフォルトで表示されます。

|

長さ

|

ネットの全長(ネット内の全ての配線トラックセグメントの合計)。

|

インピーダンス

|

ネットの平均インピーダンス(オーム単位)。これは、各トラックセグメントのインピーダンスの平均であり、その長さによって重み付けされます。

|

上昇エッジの飛行時間

|

ネット上の信号をしきい値電圧まで駆動するのにかかる時間、参照負荷(出力に直接接続されたもの)をしきい値電圧まで駆動するのにかかる時間を差し引いた時間。

|

上昇エッジのオーバーシュート

|

信号の上昇エッジにおける最大オーバーシュート(最高値以上のリンギング)。この列はデフォルトで表示されます。

|

上昇エッジの勾配

|

ネット上の信号がしきい値電圧(VT)から有効な高電圧(VIH)まで上がるのにかかる時間。

|

上昇エッジのアンダーシュート

|

信号の上昇エッジにおける最大アンダーシュート(最高値以下のリンギング)。この列はデフォルトで表示されます。

|

配線済み

|

設計内でネットが配線済み(完全または部分的)か(True)、完全に未配線か(False)を示します。

|

最高値

|

ネット上の信号が高状態で安定する電圧。

|

右クリックまたはMenuボタンを使用して、Show/Hide Columnsサブメニューにアクセスし、必要に応じてデータ列の表示を有効/無効にできます。 各ネットは、Passed、Failed、またはNot Analyzedのいずれかのカテゴリに属することができます。

|

Passed と表示されたネットは、テストで定義された範囲内のすべての値を持っていました。 |

|

Failed と表示されたネットは、定義された許容範囲外の値を少なくとも1つ持っていました。失敗した値は黄色で色付けされます。 |

|

Not Analyzed と表示されたネットは、何らかの理由でスクリーニングできませんでした。理由を表示するには、Analysis Errors列を有効にしてください。 |

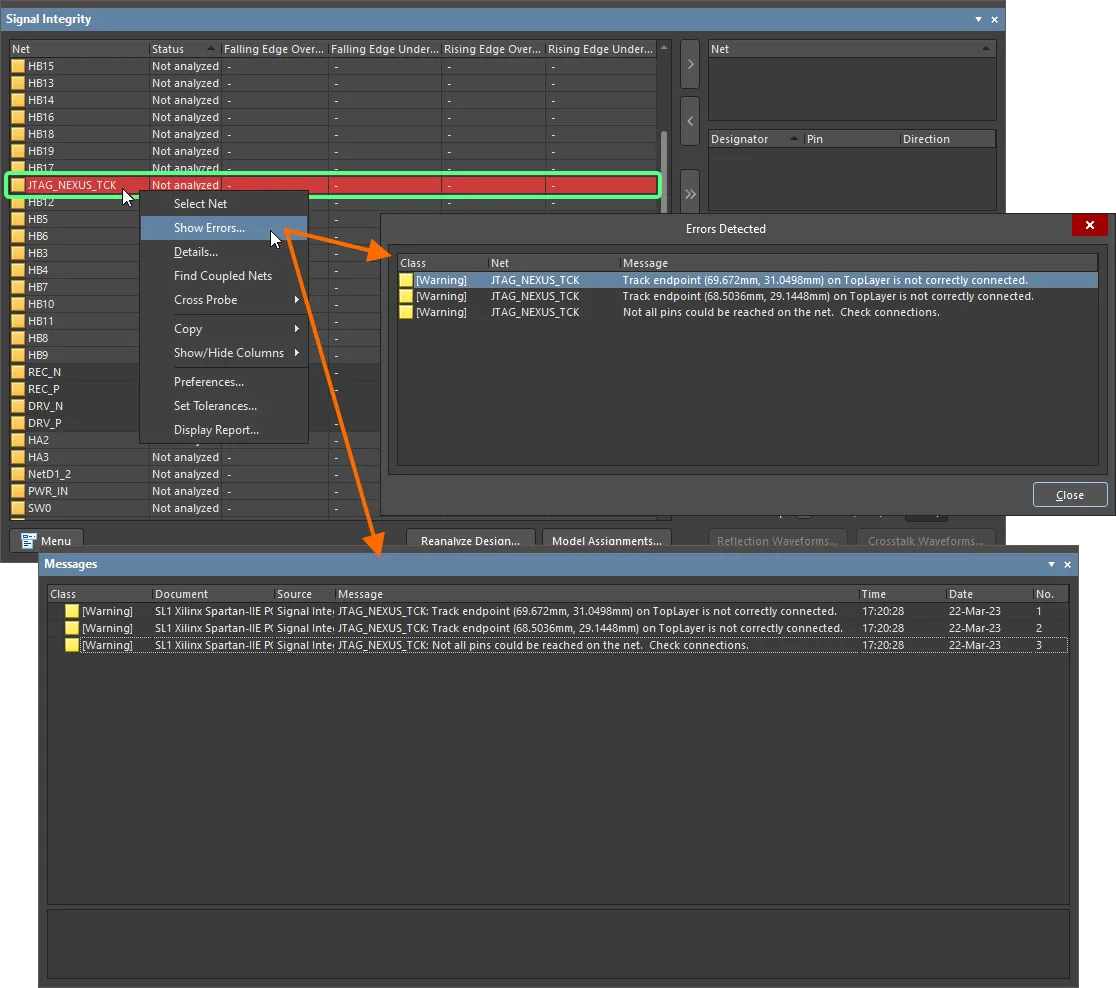

ネットの失敗

ネットの解析に失敗する一般的な理由には、コネクタ、ダイオード、トランジスタが含まれていること、出力ピンがないか複数の出力ピンがあることが含まれます。双方向ピンを含むネットがスクリーニングされる場合、ネット内に専用の出力ピンがない場合、各双方向ピンは出力ピンとして個別にシミュレートされます。これらのシミュレーションからの最悪の結果が表示されます。

ネットがスクリーニングのために解析できなかったとしても、反射やクロストークのシミュレーションでチェックできる可能性があることに注意してください。コネクタを含むネットの場合、このネットに追加された等価インピーダンスモデルを使用してコネクタをシミュレートできます。

ネットには、スクリーニングおよびそれ以降のシミュレーションの両方で不正確な解析結果につながる他のエラーが存在する可能性があります。これらのネットは、その全行が赤色で表示されます。また、シミュレートされたネット(つまり、PCB上にまだ配線されていないネット)は、薄い灰色で表示されます。

失敗したネットまたは解析されていないネットの確認

失敗したネットまたは解析されていないネットの原因を表示するには:

-

ネットの全行が赤くハイライトされている場合は、それを選択して右クリックし、Show Errorsを選択します。これにより、メッセージパネルにメッセージが追加され、問題を修復するためにクロスプローブできます。

-

選択したネットの利用可能なすべての情報を表示するには、右クリックしてDetailsを選択します。Full Detailsダイアログには、結果テーブルに表示できるすべてのスクリーニング解析結果が表示され、以下が含まれます:

-

Component Count – 選択したネットに接続するパッドを持つコンポーネントの数。

-

Track Count – 総配線されたネットを構成する個々の配線されたトラックセグメントの数。

-

Minimum Impedance (Ohms) – ネットの最小インピーダンスで、ネット内のすべてのトラックセグメントの個々のインピーダンスを考慮します。

-

Maximum Impedance (Ohms) – ネットの最大インピーダンスで、ネット内のすべてのトラックセグメントの個々のインピーダンスを考慮します。

-

右クリックメニューからCross Probeを選択する(またはMenuをクリックする)ことで、選択したネットを回路図またはPCB上でクロスプローブできます。

F4 ショートカットキーを使用して、シグナルインテグリティパネル(および現在「フローティング」モードにある他のパネル)の表示を切り替え、パネルと設計の間を迅速に切り替えることができます。

-

単一のネットまたは一連のネットに結合されているネットを表示するには、目的のネットを選択してから右クリックし、Find Coupled Netsを選択します。これにより、これらの選択されたネットに結合されているすべてのネットが選択されます。どのネットが結合されていると見なされるかの基準は、Signal Integrity Preferencesダイアログ(MenuボタンをクリックしてSignal IntegrityパネルでPreferencesを選択することでアクセス)で設定できます。

-

必要なネットを選択し、右クリックメニューからCopyを選択することで、有用な情報をクリップボードにコピーし、他のアプリケーションに貼り付けてさらなる処理や報告に使用できます。表示される情報は、右クリックメニューからShow/Hide Columnsコマンドを選択して、表示される列をカスタマイズすることでカスタマイズできます。

-

解析によって生成された結果を強調表示するレポートも、Signal Integrityパネルの右クリックメニューからDisplay Reporを選択することで利用可能です。これにより、レポートファイル

Signal Integrity Tests Report.txtがテキストエディタで開かれ、プロジェクトに追加されます。

設定の編集

定義したすべての解析に適用されるさまざまな設定を指定できます。これには、一般的な設定、統合方法、精度の閾値が含まれます。設定を変更すると、すべてのプロジェクトに適用されます。

Signal IntegrityパネルのMenuボタンをクリックし、Preferencesを選択してSignal Integrity Preferencesダイアログを開きます。

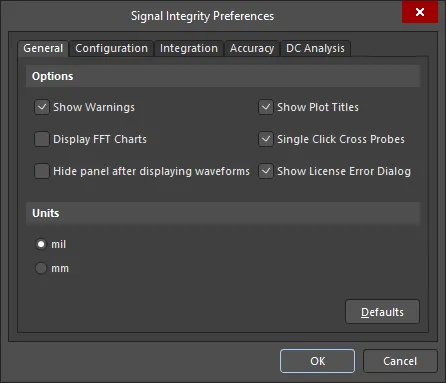

Signal Integrity Preferencesダイアログ

すべてのシグナルインテグリティの設定は、ダイアログ内のDefaultsボタンをクリックすることで、デフォルト値に戻すことができます。

-

Generalタブを使用して、シグナルインテグリティ解析を実行する際に設計内のエラーに関連するヒントや警告を表示するエラーハンドリングオプションを設定します。遭遇したヒントや警告は、Messagesパネルにメッセージとしてリストされます。Show Warningsオプションが有効であり、警告が存在する場合、Signal Integrityパネルにアクセスしようとすると警告確認ダイアログが表示されます。さらに、波形を表示するように選択した後にSignal Integrityパネルを非表示にすることもできます。シグナルインテグリティ測定のデフォルト単位を定義したり、結果の波形がSimDataエディタに表示されるときにプロットタイトルとFFTチャートが表示されるかどうかも設定できます。

-

Configurationタブでは、結合されたネット間の最大距離や結合セクションとみなされる最小長さなど、さまざまなシミュレーション関連のしきい値を定義します。

-

Integrationタブでは、解析に使用される数値積分法を定義します。Trapezoidal法は比較的速く正確ですが、特定の条件下では振動する傾向があります。Gear法はより長い解析時間を要しますが、より安定している傾向があります。より高いギアオーダーを使用すると理論的にはより正確な結果が得られますが、解析時間が増加します。デフォルトはTrapezoidalです。

-

Signal Integrity PreferencesダイアログのAccuracyタブでは、解析に関わるさまざまな計算アルゴリズムの許容誤差しきい値と制限設定を定義します。

-

DC Analysisタブを使用して、DC解析に関連するさまざまなパラメータの許容誤差しきい値と制限設定を定義します。

トレランスの設定

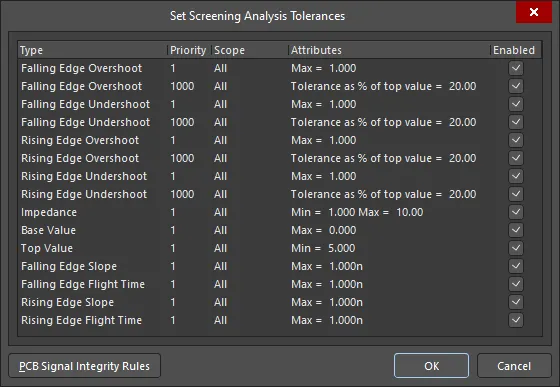

デフォルトのオーバーシュートとアンダーシュートのテストは、どのネットが最も問題になりそうかを判断するのに最適な特性として定義されています。4つのデフォルトのトレランスルールと、回路図やPCBに設定された任意のシグナルインテグリティルールが全て有効になり、設計が初めて解析されるときに実行されます。これらのルールを有効または無効にするには、シグナルインテグリティパネルのMenuボタンをクリックし、Set Tolerancesを選択します。Set Screening Analysis Tolerancesダイアログが表示されます。

Set Screening Analysis Tolerancesダイアログ

設計が解析されるときにそのルールが実行されるようにするには、ルールタイプの隣にあるEnabledチェックボックスをクリックします。

(回路図のみのモードでない場合)PCB Signal Integrity Rulesをクリックして、必要な信号整合性ルールを追加または変更できるPCBルールと制約エディタダイアログを開きます。OKをクリックして、信号整合性パネルに戻ります。

解析の準備

解析を実行する前に、さらに解析する必要があるネットを選択する必要があります。また、コンポーネントの部品技術やピンの特性を表示または変更するためにバッファを編集したり、必要に応じてネットに終端を追加したりすることもできます。

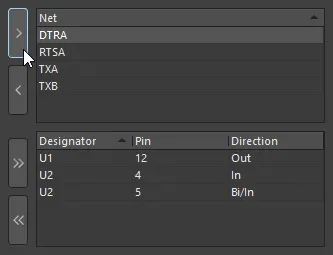

解析するネットの選択

ネット(反射および/またはクロストーク)に対してさらに解析を行うには、シグナルインテグリティパネルの右側のリストでネットを選択する必要があります。左側のリストにあるネットをダブルクリックして選択し、それを右側のリストに移動します。または、矢印ボタンを使用して、この選択状態へのネットの移動を行います。左側のリストでネットを複数選択するには、ShiftキーまたはCtrlキーを押し続けます。

関連する回路図やPCBドキュメント上で選択されたネットにクロスプローブするには、右クリックメニューからCross Probeオプションを選択します。ターゲットドキュメントがデザインスペースでアクティブになり、選択されたネットがPreferencesダイアログのSystem – Navigationページで定義されたハイライト方法に従って表示されます。

ネットがこの選択状態にある場合、シミュレーションを実行する前にさらに設定を行うことができます。

被害ネットと加害ネットの設定

クロストーク解析の場合、被害ネットまたは加害ネットを設定する必要があります。この解析の性質上、この機能は2つ以上のネットが選択されている(右側のリストに移動されている)場合にのみ利用可能です。 右側のネットリストでネットを選択し、右クリックしてSet AggressorまたはSet Victimを必要に応じて選択します。ネットの状態が更新されます。ネットの設定を解除するには、右クリックメニューからClear Statusを選択します。

双方向ピンの方向設定

指定されたネット内の双方向ピンの方向を設定することができます。方向を設定するには、右上のリストで影響を受けるネットを選択します。これにより、そのネットに属するピンのリストが下に表示されます。ピンのリストから、選択した双方向ピンの入出力ステータスを、右クリックして右クリックメニューからステータスを選択して変更します。これらの入出力設定は、次回このパネルを使用するときのためにプロジェクトと共に保存されます。

また、右クリックメニューからCross Probeオプションを選択することで、関連する回路図またはPCBドキュメント上のピン/パッドにクロスプローブすることもできます。ターゲットドキュメントがデザインスペースでアクティブになり、選択したピン/パッドが、PreferencesダイアログのSystem – Navigationページで定義されたハイライト方法に従って表示されます。

バッファの編集

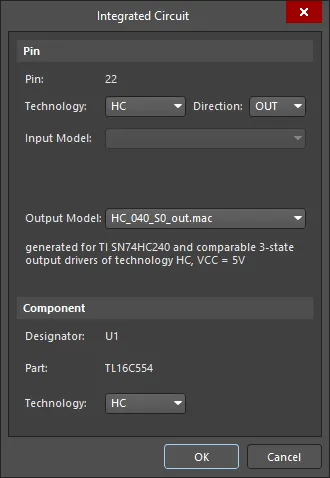

コンポーネントの部品技術やピンのプロパティ(入力および出力モデルやピンの方向など)を表示または変更したい場合があります。現在選択されているネットに接続されているコンポーネントのみを変更できます。ピンのリストで右クリックメニューのEdit Bufferオプションを使用すると、コンポーネントのデータダイアログにアクセスできます。

表示されるダイアログとオプションは、ピンが属するコンポーネントのタイプ(例えば、抵抗器、IC、BJTなど)によって異なります。Integrated Circuitダイアログは、ICコンポーネントタイプ用に示されています。

Integrated Circuitダイアログ

ピンのTechnologyとDirectionを選択すると、選択するための関連する入力および/または出力モデルのリストが表示されます。技術と方向の変更は解析内でのみ使用され、パネルがリセットされたときには保存されません。

パートのTechnology、Input Model、Output Modelフィールドはコンテキストに依存します。コンポーネントパートのテクノロジーを選択すると、そのパートのデフォルトモデルはこのテクノロジーから取得されます。ただし、特定のピンモデルが既に割り当てられている場合(例えば、IBISモデルのインポートの一部として)、コンポーネントパートのテクノロジーを変更しても、それらのピンのピンモデルは再割り当てされません。

ピンのプロパティを編集しているのであって、コンポーネント全体を編集しているわけではないことに注意してください。たとえ、コンポーネントのテクノロジーを変更できるとしてもです。シグナルインテグリティモデルを回路図で設定した際に作成されたテクノロジー/ピンモデルの設定には、Edit Bufferコマンドを使用する(またはピンをダブルクリックする)ことで加えた変更が優先されます。

このアプローチを使用して加えた変更は、解析セッション間で保持されないことに注意してください。この機能は、割り当てられたピンモデルを迅速に変更して、何が起こるかをテストするために使用されることを意図しています。割り当てを保持したい場合は、ピンモデルを編集するのではなく、コンポーネントに割り当てられたモデルを編集してください。

終端

信号波形に見られる振動は、関連する伝送線(トレース)上の複数の反射によるものです。これらの反射、または「リンギング」は、通常、低インピーダンスのドライバーと高インピーダンスのレシーバーがある場合に、PCB設計で最も頻繁に発生します。

負荷で良好な信号品質を得るには、理想的には反射がゼロ(リンギングなし)であることを意味します。リンギングのレベルは、終端を使用して設計に受け入れられるレベルまで減少させることができます。

シグナルインテグリティパネルには、終端アドバイザーが組み込まれており、定義した場所にネットに「仮想終端」を挿入できるようになっています。この方法では、ボードに物理的な変更を加えることなく、さまざまな終端戦略をテストする自由があります。

利用可能な終端シミュレーションは以下の通りです:

-

直列抵抗

-

VCCに対する並列抵抗

-

GNDに対する並列抵抗

-

VCCとGNDに対する並列抵抗

-

GNDに対する抵抗とキャパシタ

-

GNDに対する並列抵抗とキャパシタ

-

並列ショットキーダイオード

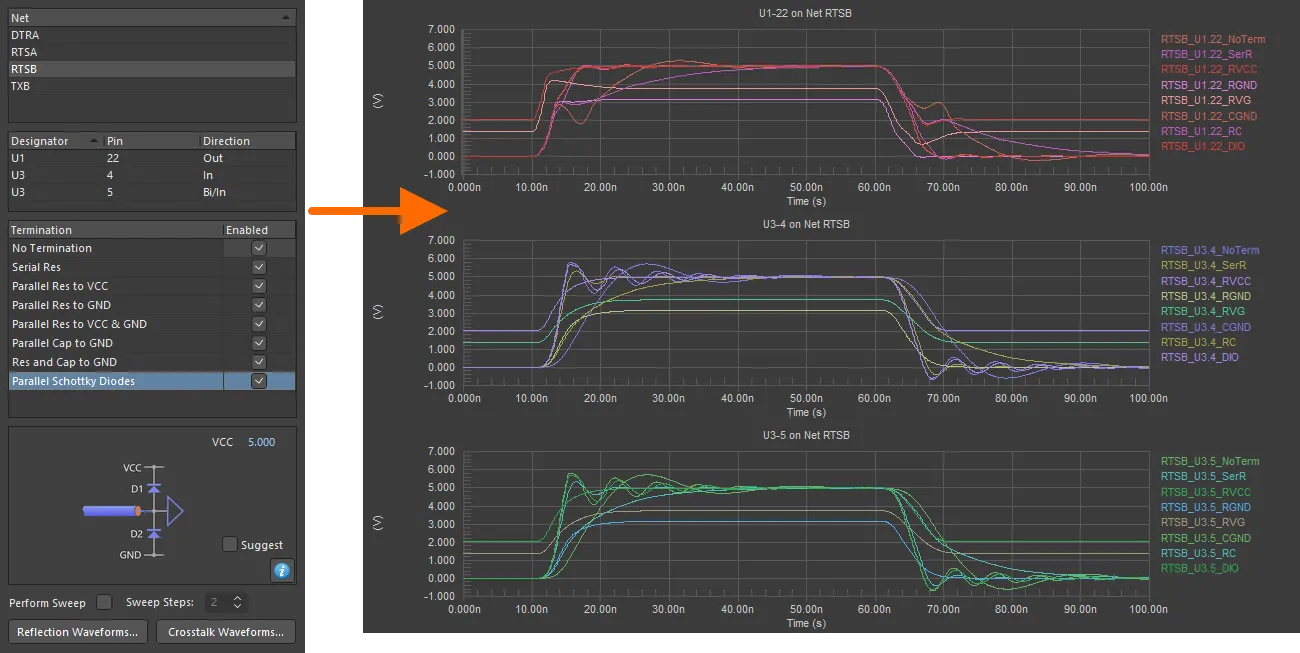

各終端タイプは、終端リストで有効または無効にすることができます。反射とクロストーク解析を行う際には、複数の終端タイプを有効にすることができ、それぞれに対して別々の波形が生成されます。これにより、伝送線上の信号品質を最適化し、反射(リンギング)を許容レベルまで減少させるために、設計に追加する最適な終端を決定することができます。

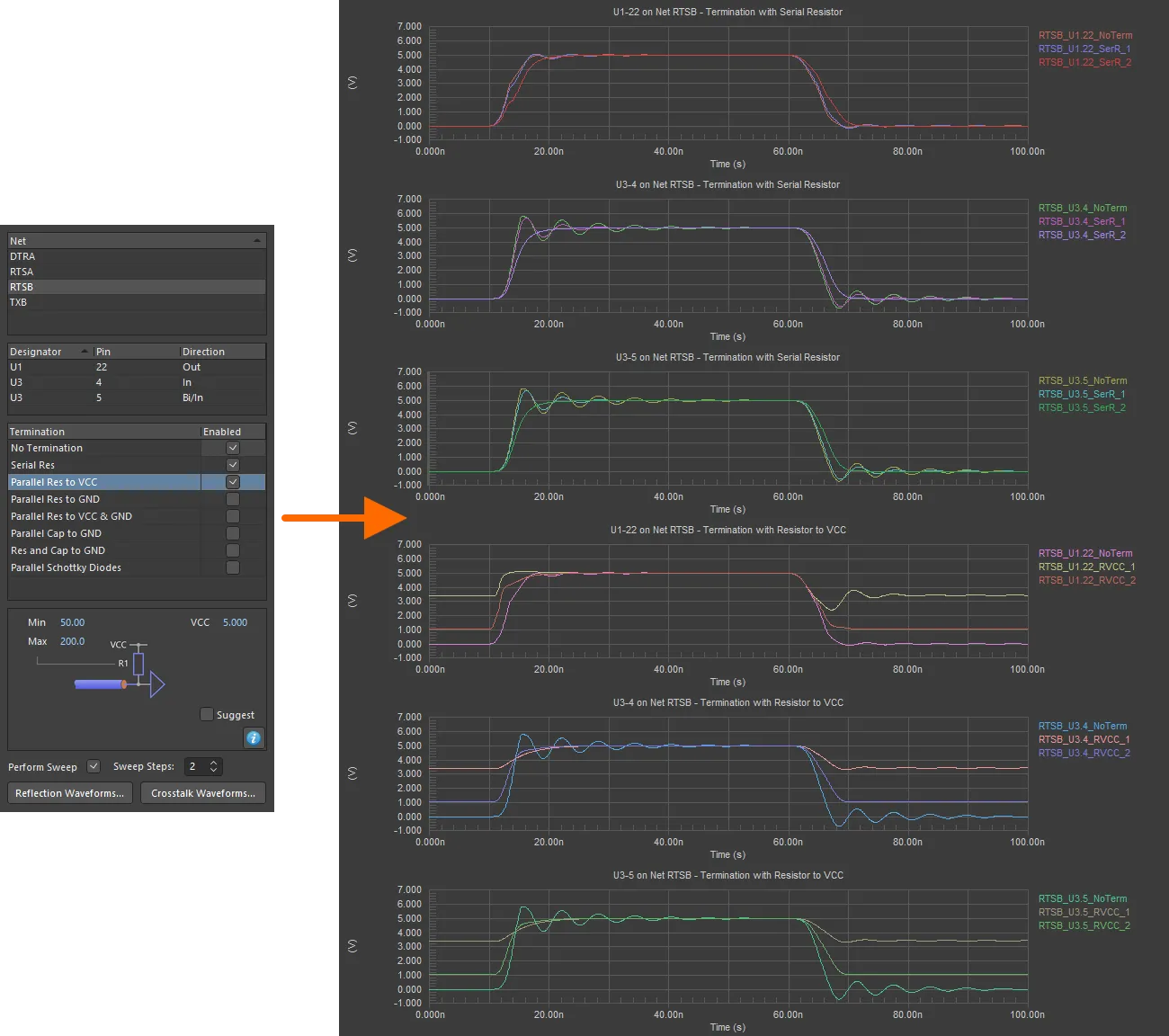

反射またはクロストーク解析を実行すると、有効にされた終端タイプごとに別々の波形セットが生成されます。Serial Res終端が使用される場合、選択されたネットのすべての出力ピンに配置されます。他の終端タイプの場合、終端はネット内のすべての入力ピンに配置されます。 終端の最適な結果を得るためには、ネットの特性に基づいて関連する部品の値を設定することも必要になります。

-

終端が選択されると、その終端を示す図が下に表示されます。この図では、終端に使用される抵抗器とコンデンサの最小値と最大値の設定が可能です。

-

最小値と最大値は、終端のリストに表示されるスイープ数が1より大きい数に設定されている場合に使用されます。

-

終端のタイプについての詳細情報を知りたい場合は、それを選択して?(ヘルプ)ボタンをクリックしてください。 Suggestオプションを有効にすると、各終端タイプの情報ポップアップに記載されている式に従って計算された推奨値が灰色で表示されます。これらの値を受け入れることも、Suggestオプションを無効にして必要に応じて自分の値を入力することもできます。

-

終端コンポーネントの値の範囲をスイープして解析を実行したい場合は、Perform Sweepオプションが有効であることを確認し、解析を実行する際に必要なSweep Stepsの数を設定してください。解析の各スイープで使用される値は、入力された最小値と最大値、およびSweep Stepsフィールドで選択された値に依存します(例えば、Sweep Stepsが2に設定されている場合、解析の最初のパスでは最小値が、2番目では最大値が使用されます)。各スイープごとに比較目的のために別々の波形が生成されることに注意してください。

回路図上での終端の配置

波形が作成され、最適な終端が検出されたら、その終端を直接回路図シート上に配置することが望ましい場合があります。これは、Terminationリストの右クリックメニューを介して実現できます。配置は現在選択されているネットにのみ適用されることに注意してください。

選択した終端回路を「仮想終端」として使用するのではなく、実際に回路図上に配置したい場合:

-

Terminationセクション内で右クリックし、Signal IntegrityパネルでPlace on Schematicを選択します。

-

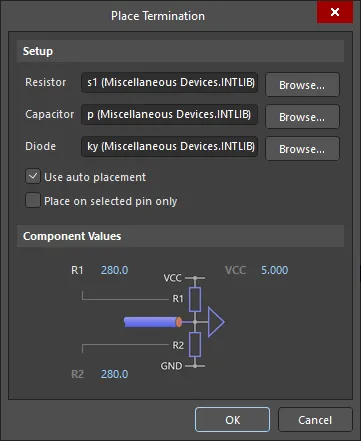

Place Terminationダイアログが表示され、終端部品に使用するライブラリコンポーネント、自動配置か手動配置か、適用可能な全ピンに配置するか選択したピンのみに配置するか、部品の正確な値を設定するなど、さまざまなプロパティの設定が可能です。OKをクリックして続行します。

終端配置ダイアログ

-

信号完全性アナライザーは、ピンが属するソース回路図ドキュメントを見つけます。次に、ドキュメントの空いているスペースに、必要な部品(抵抗、コンデンサー、または必要に応じたもの)と電源オブジェクトを正しい値で追加します。この終端回路を回路図の適切なピンに接続します。

この後も、ピンにコンポーネントを正しく配線する必要があるでしょう。さらに、PCBが関与している場合は、これらを同期させてPCB内で配線する必要があります。Design » Update PCBを選択して、これらの部品をPCBにも追加同期させてください。

解析の実行

必要に応じてネットが設定され(終端オプションが選択された場合)、Signal IntegrityパネルのReflectionsまたはCrosstalksボタンをクリックして、波形を生成します。

-

反射解析の場合、1つ以上のネットをシミュレートできます。ただし、解析するネットの数は合理的な範囲に保つ必要があります。多くのネットを解析すると、解析時間が大幅に増加します。

シグナルインテグリティアナライザーは、PCBおよび関連するドライバーおよびレシーバーI/Oバッファーモデルからの配線とレイヤー情報を使用して、ネットのノードでの電圧を計算します。2Dフィールドソルバーは自動的に伝送線の電気的特性を計算します。モデリングは、DCパス損失が無視できるほど小さいと仮定します。

-

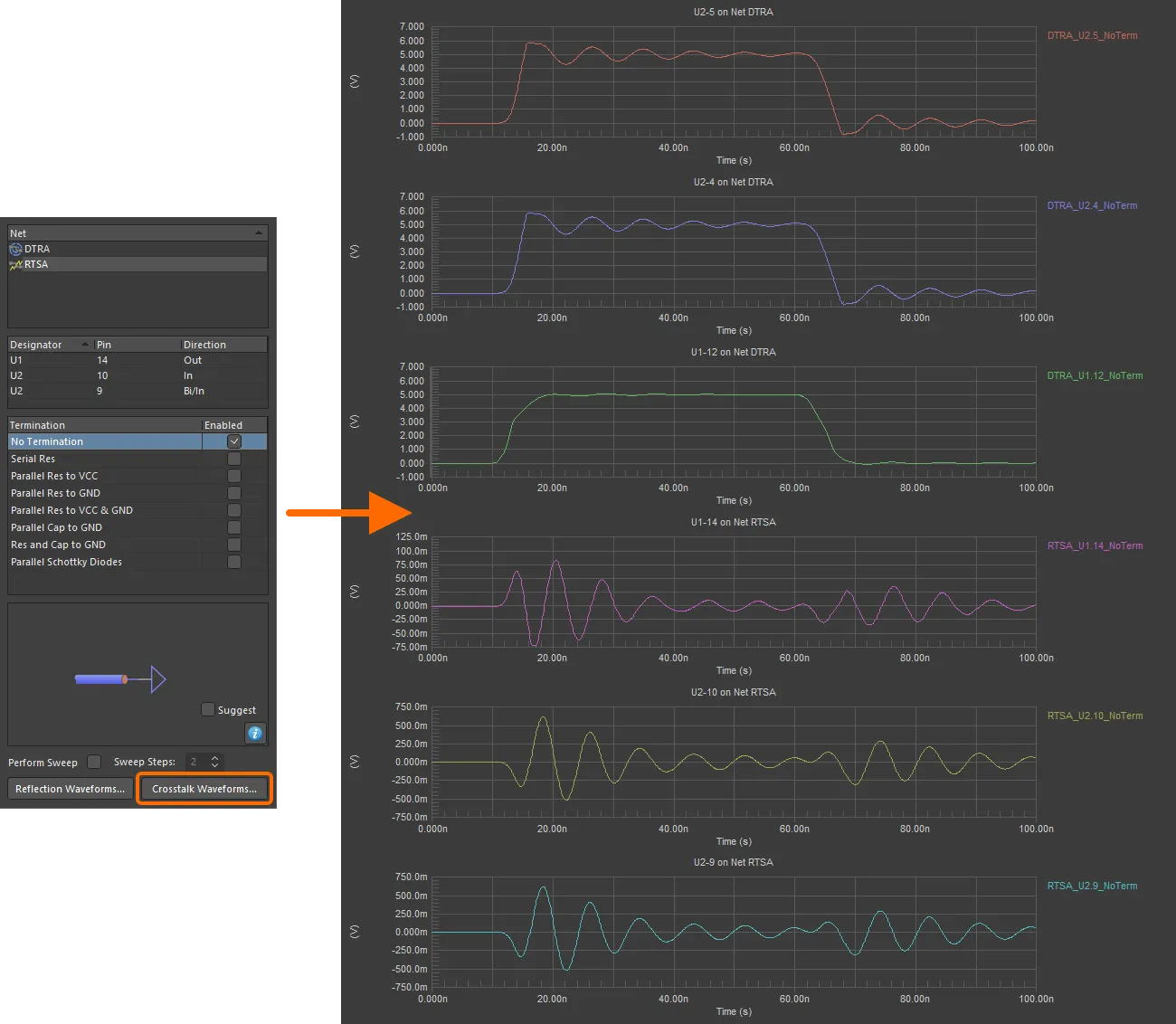

クロストーク解析の場合、少なくとも2つのネットを対象にする必要があります。通常、クロストーク解析を行う際には、1つのネットとその直接隣接する2つのネットが考慮されます。

クロストークのレベル(またはEMIの程度)は、信号線上の反射に直接比例します。信号品質条件が達成され、正しい信号終端によって反射がほぼ無視できるレベルまで低減された場合、つまり信号が最小限の信号漂流で目的地に届けられる場合、クロストークも最小限に抑えられます。終端についての詳細をご覧ください。

クロストーク解析は、PCB設計ドキュメントからのレイアウト後のシグナルインテグリティ解析を実行する場合にのみ可能です。これは、このタイプの解析には配線されたネットが必要であるためです。

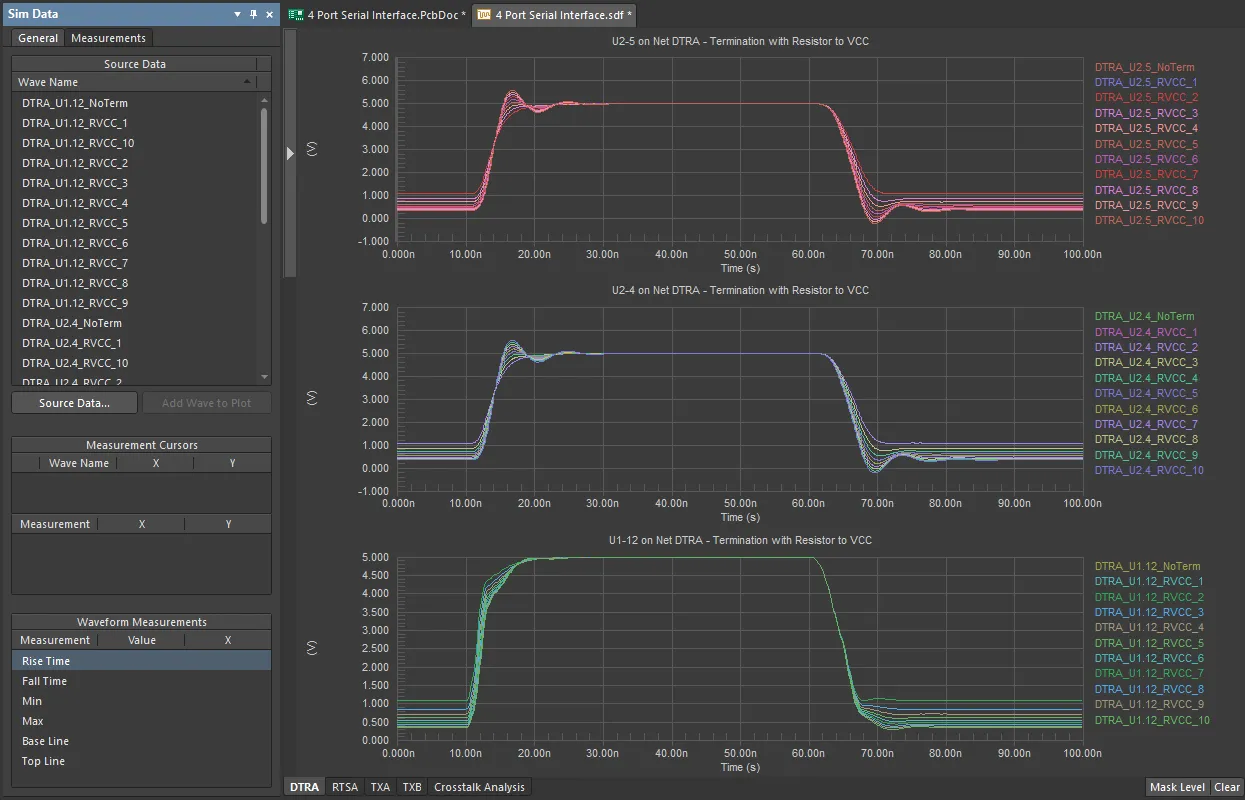

ボタンをクリックすると、解析が開始され、シミュレーションデータファイル(<ProjectName>.sdf)が生成されます。このファイルは別のタブとして開き、SimDataエディタで解析結果が表示されます。 生成されたSDFドキュメントには、解析対象として選択したネットに対応する1つ以上のタブが含まれています。各タブには、複数の波形プロットを含むことができるチャートが含まれています。波形プロットには複数の波形が含まれ、波形はシミュレーションデータを表します。

信号整合性解析結果へのアクセス。下部のタブをクリックして、各解析タイプの結果にアクセスします。

反射解析データ

選択された各ネットについて、シミュレーションの結果として生成されたチャートが、そのネットの名前でマークされたSDFドキュメントのタブに表示されます。チャートには、すべての終端オプションに関する波形が含まれます。

反射解析チャートに表示されるデータは、以下に依存します:

-

テスト対象のネットに含まれるピンの数

-

有効にされた特定の終端タイプ(Signal Integrityパネル上)

-

解析の一部として(仮想)終端コンポーネント値のスイープが含まれているかどうか(再び、Signal Integrityパネル上で有効にされ、定義されている)

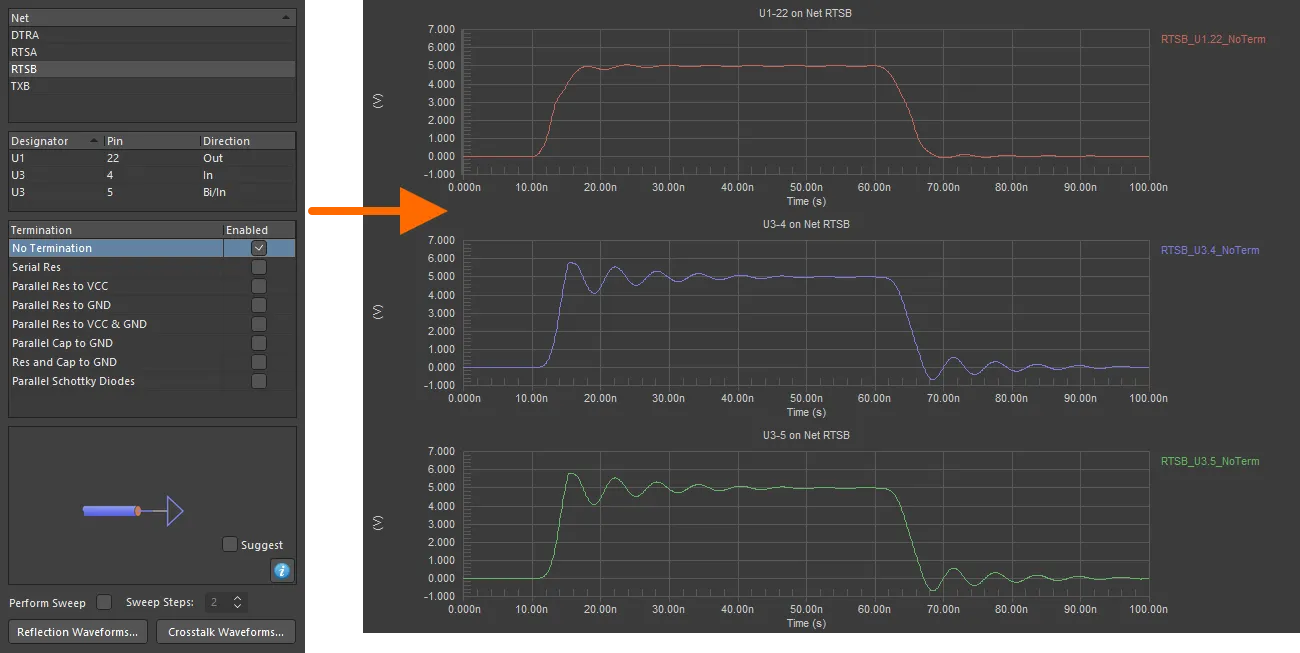

終端コンポーネントなしで反射解析を実行した場合、チャートにはテスト対象のネット内の各ピンに対して1つのプロットが含まれます。各プロットには、終端を使用せずにそのピンの解析に関連する1つの波形が含まれます。例えば、次のピンを含むネットRTSBの反射解析を考えてみましょう:

終端を有効にしない場合、このネットに対して以下のチャート(プロットと波形)が作成され、表示されます。波形名は、ネット名、特定のピン、および終端のタイプ(この場合、終端なし)に基づいて作成されます。

反射結果 - 終端なし

特定の終端タイプを有効にし、値のスイープを有効にしない場合、それぞれの終端を使用した結果を表す追加の波形が各プロットに追加されます。下の画像は、すべての終端タイプが有効になっている場合を強調して示しています。

反射結果 - 終端有効(スイープなし)

終端を有効にし、かつ終端値のスイープ(2つ以上のスイープステップで)を行うと、テスト対象のネット内の各ピンについて、有効にした各終端のプロットが得られます。各プロット内に表示される波形は、その特定の終端に対する各スイープステップのもの、および比較用の終端なし波形(ノー終端波形)です。下の画像は、この表示を例示しています。私たちの例であるRTSBネットに対して、2種類の終端(Serial ResとParallel Res to VCC)が有効にされ、スイープ機能がSweep Stepsを2に設定して有効にされています。

反射結果 - 端子処理有効、スイープあり。

クロストーク解析データ

クロストーク解析では、すべてのネットがCrosstalk Analysisという名前のチャートに表示されます。クロストーク解析チャートのデータ表示は、反射解析チャートのそれと本質的に同じです。唯一の違いは、この解析タイプには単一のチャートのみが存在し、解析に考慮される各ネットの各ピンに対するプロットが含まれることです。下の画像は、クロストーク解析で2つのネットが考慮されている例を示しています - DTRA(攻撃ネットとして設定)とRTSA(被害ネットとしてデフォルト設定)。特定の終端タイプは有効にされていません。

クロストーク結果 - 端子なし

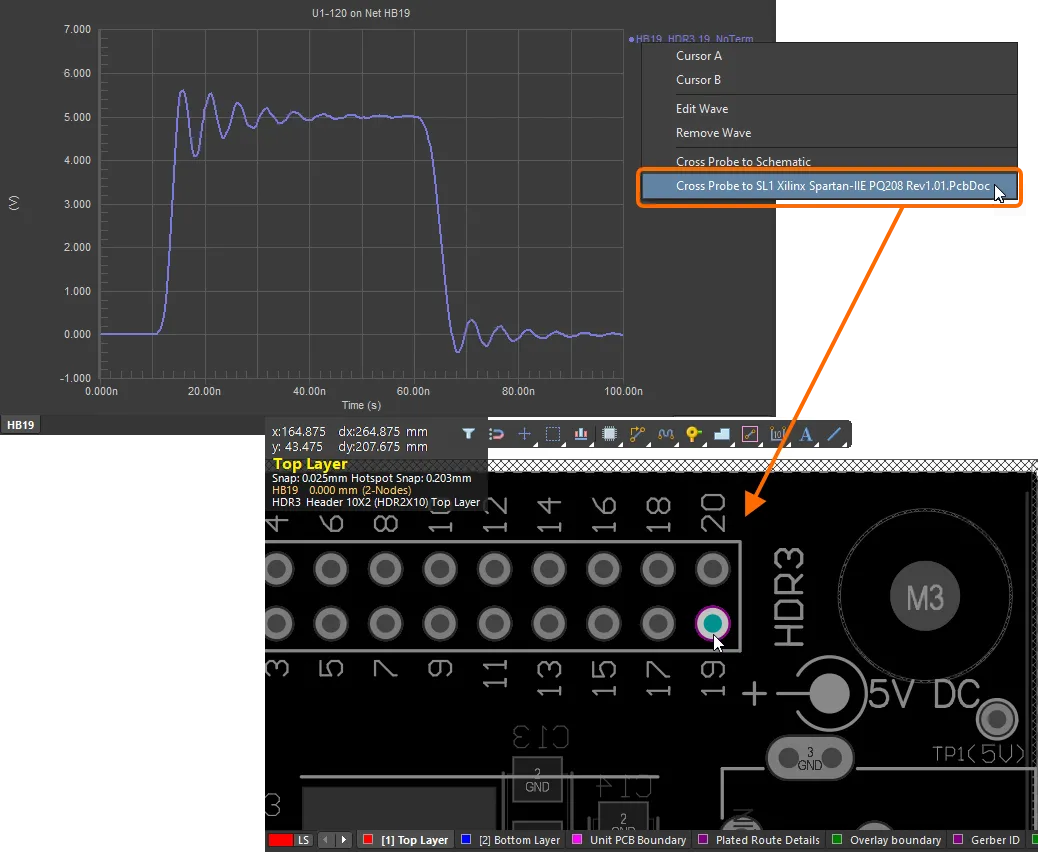

PCBへのクロスプロービング

設計のポストレイアウト信号整合性解析を実施した場合、選択した波形からPCBへクロスプローブする機能が利用できます。

クロスプローブを行うには、必要な波形名を右クリックして、Cross Probe to <DocumentName>.PcbDoc コマンドを選択します。PCBドキュメントがアクティブになり、解析されたネットの対応するピンが、PreferencesダイアログのSystem – Navigationページで定義されたHighlight Methodsに従って、再度ハイライトされます。

PCBにクロスプロービングする例で、コンポーネントHDR3のパッド19(ネットHB19に関連付けられている)がハイライトされています。

結果を解析した後

結果を解析したら、選択したネット上のリンギングを減らすために、さまざまな終端を試してみるなどの実験を行うことができます。回路やPCBを変更し、望ましい結果が得られるまで信号完全性解析を再実行する必要があるかもしれません。

異なるネットに対して反射とクロストーク解析を繰り返し実行すると、結果は同じシミュレーションデータファイルに追加され、新しいチャート(SDFドキュメントの下部にあるタブ)として表示されることに注意してください。