設計構造が接続性に与える影響

Copy Link

Copied

関連ページ: マルチシート&階層設計

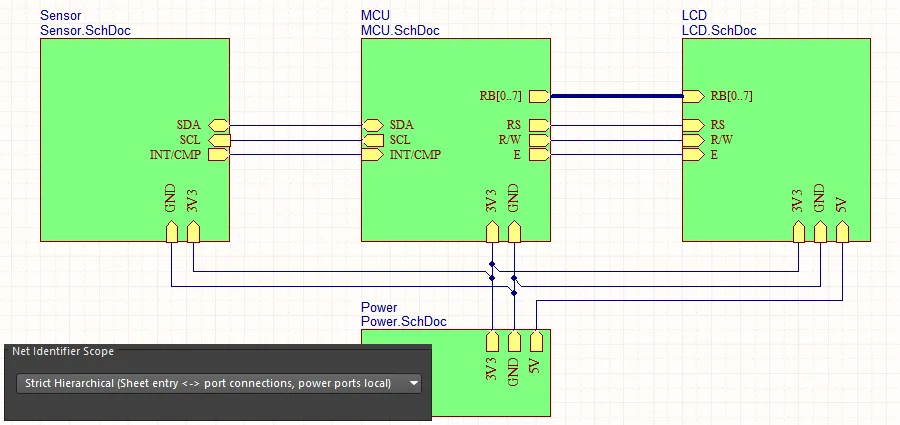

設計が1枚の回路図シートに収まらない場合、複数のシートに分割して配置することができます。マルチシート回路図の組織化と接続性の作成には、2つの異なるモデルがあります。一つはフラットデザインで、これは1枚の大きな回路図シートがいくつかの小さなシートに切り分けられたと考えることができます。もう一つは階層設計で、シートが祖父母-親-子のタイプの構造でリンクされています。

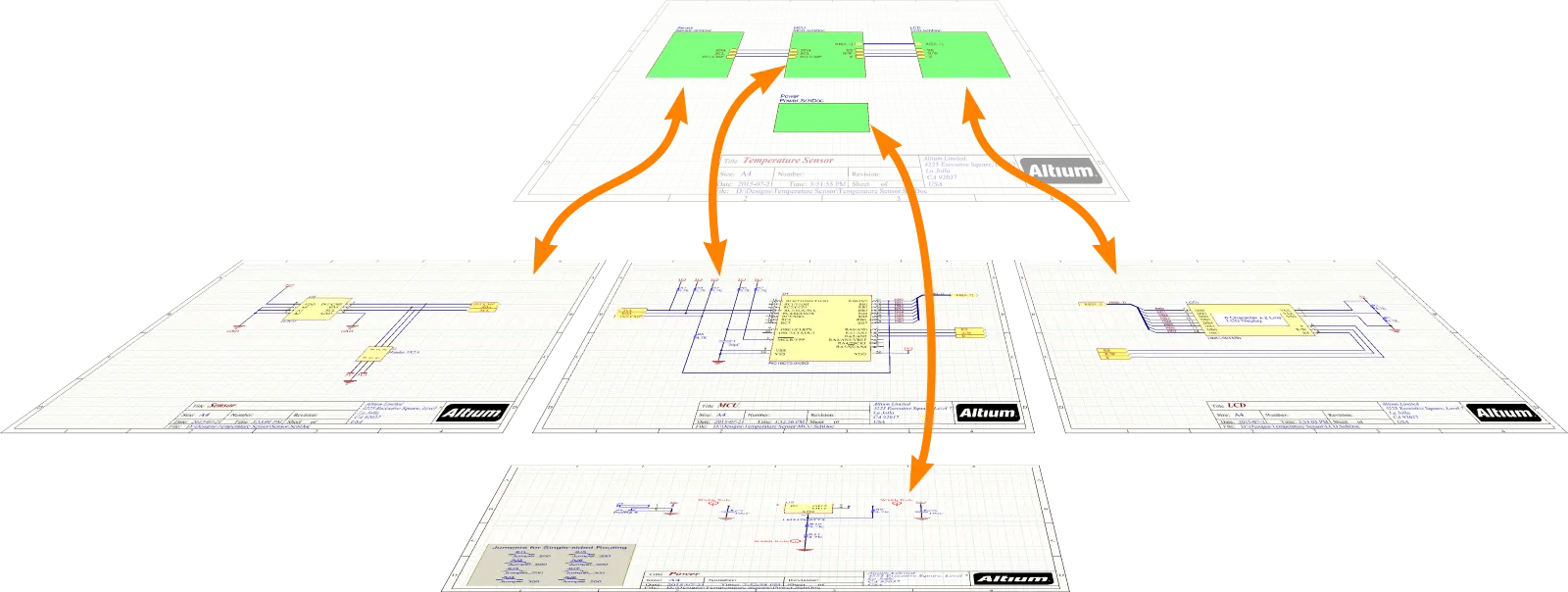

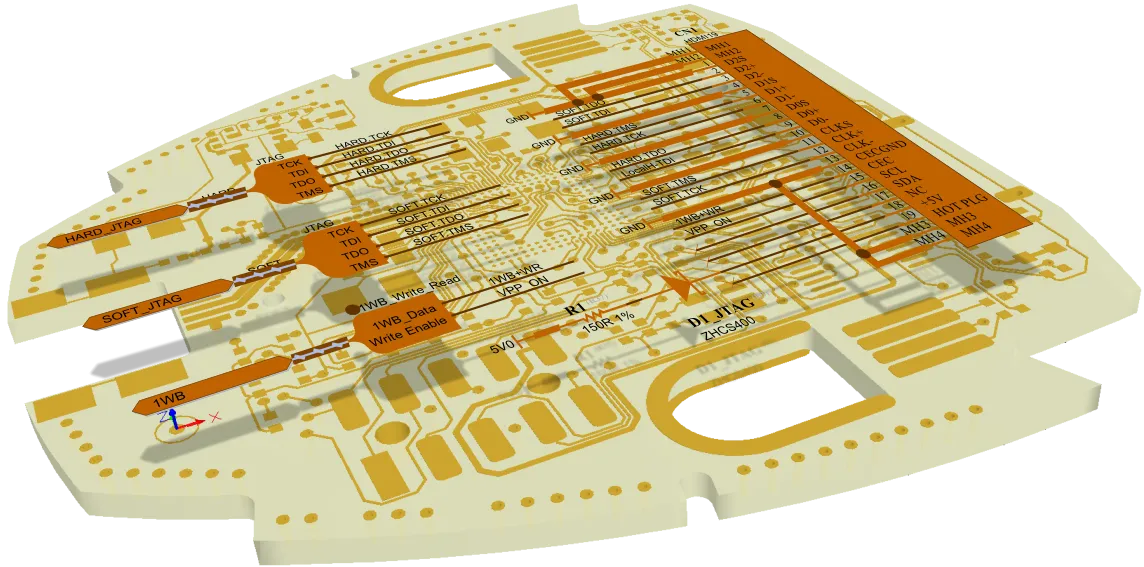

マルチシート設計は、親シートにシートシンボルを配置することで実装され、これは子シートを表し、リンクするものです。下の画像に示されています。

シートシンボルは下位レベルのシートを表し(そしてリンクします)。フラットデザインでは、この構造は1レベルの深さしか持てませんが、階層型デザインでは深さに制限はありません。

設計がフラットか階層的かを決定するのは何かというと、これはネット識別子スコープの設定によって行われ、シート間の接続がどのように作成されるかを定義します。これは、Project Optionsダイアログのオプションタブで設定します。

階層設計の場合、プロジェクトにはトップシートが 1 枚しか含まれないことを覚えておくことが重要です。他のすべてのソース ドキュメントは、シート シンボルで参照する必要があります。デザイン検証を実行するときに、複数のトップレベルドキュメント違反チェックを使用して、違反が当てはまらない場合はフラグを立てることができます。さらに、シート記号は、それが載っているシートや上の階層のシートを参照することはできません。これにより、構造に解決できないループが作成されるためです。

フラットデザイン

関連ページ: マルチシート&階層設計

フラットデザインとは、接続が一つのシートから別のシートに直接作成される設計のことを指します。これは、親シート上のシートシンボルを通過しません。フラットデザインでは、シートシンボルは単に子シートを表す(そして参照する)ものです。設計内の全てのシートは階層がないため、Projectsパネルで同じレベルに表示されます。以下の画像2つは、フラットデザインを示しています。

フラットデザインは作成が簡単です。フラットデザインには、各子シートに対するシートシンボルを含むトップシートが含まれる場合がありますが、このトップシートはシート間の接続を作成するために使用されないため、オプションです。小規模な設計で、回路図シートが2枚または3枚しかない場合、トップシートが価値を加えないと判断するかもしれません。シートの数が多くなると、トップシートは論理ブロック(シートシンボル)がシート上にどのように配置されているかによって、回路設計の機能性を読み手が理解するのに役立ちます。

同じデザインが、トップシートなし(左)とトップシート付き(右)で示されています - どちらもフラットデザインの例です。

フラットデザインでは、シート間の接続は、上の画像にある虫眼鏡で示されているように、ポート、オフシートコネクタ、パワーポート、ネットラベルによって作成できます。推奨されるアプローチは、各シート内ではネットラベルを使用し、シート間ではポートを接続することです。ポートはオフシートコネクターよりも多くの機能を提供し、ポートクロスリファレンスを追加する機能を含みます。これにより、各ポートにSheetName[GridReference]が追加され、下の画像に示されているように、別のシートの対応するポートを参照します。

フラットデザインのシート数に制限はありません。

各ポートの隣にポート相互参照が追加され、対応するポートのターゲットシートとグリッド参照が示されています。

設計がフラットであるとは、接続が一枚のシートから別のシートへ直接行われることを意味します。この接続動作は、ネット識別子スコープの設定によってAutomatic、Flat、またはGlobalに設定することで定義されます。シート間の接続を作成するためにポートとネットラベルの混在を使用する場合、Automaticオプションは使用できないことに注意してください。この状況では、Net Identifier Scopeを手動でGlobalに設定する必要があります。

階層型設計

メインページ: マルチシート&階層型設計

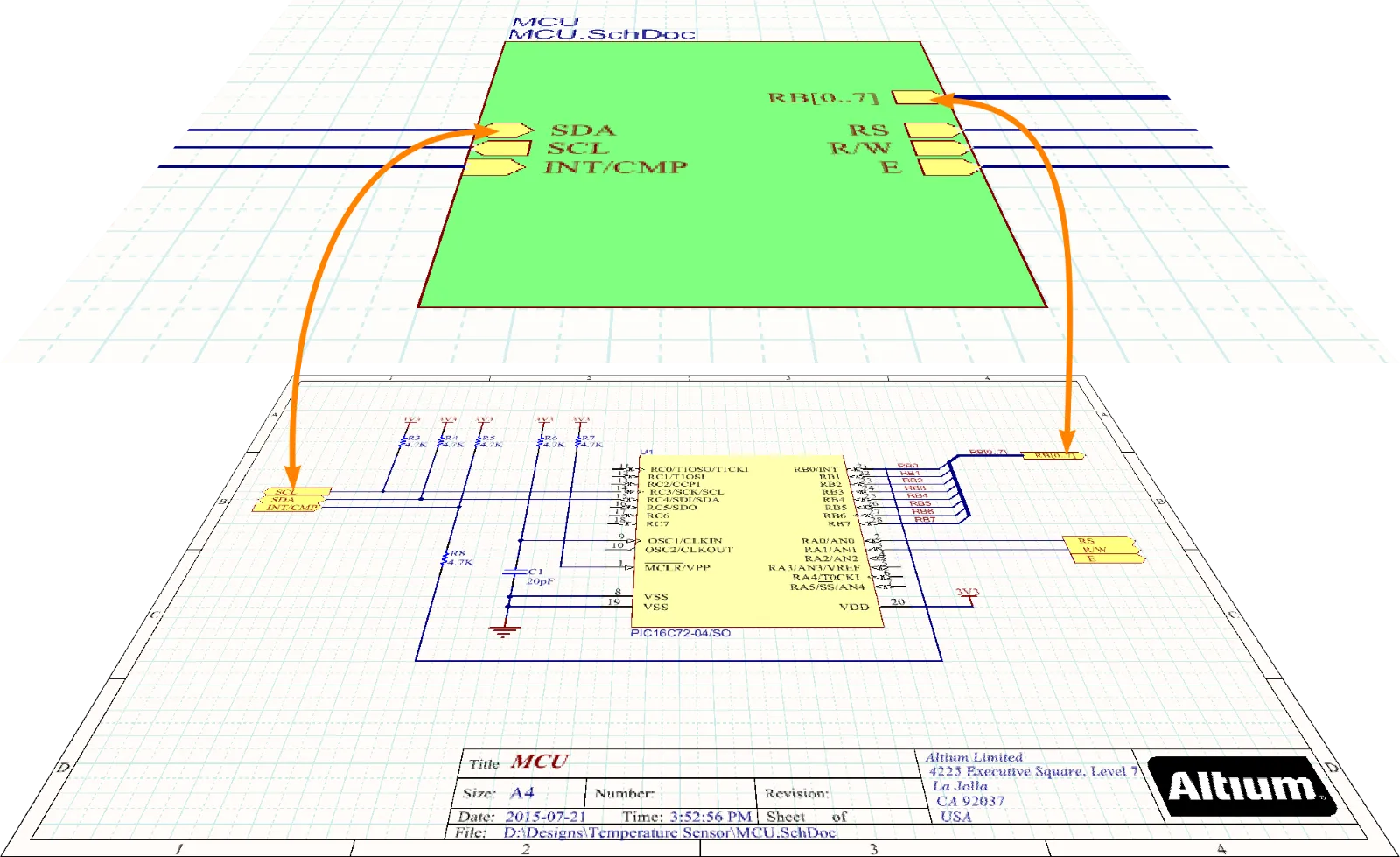

設計が階層的と言われるのは、シート間の接続がシートシンボルからそのシートシンボルによって参照される子シートへと下降する場合です。ネットレベルでは、そのシートシンボル内のシートエントリと、子シート上の同じ名前のポートとの間に接続が作成されます。このタイプの接続は、作成されるシート間の接続が親シートとその子シートの間でのみ上下するため、垂直接続とも呼ばれます。

階層設計では、親シートのシートエントリーから子シートの対応するポートへと、ネットレベルの接続があります。

階層設計には二つの大きな強みがあります。

-

最初のポイントは、設計の機能性を読者に示す能力であり、それは回路図シートが論理ブロック(シートシンボル)として構造化され、提示される方法によります。トップレベルの回路図は、設計を一連の高レベル機能ブロックとして提示し、ブロックの配置は、全体の回路の伝統的な左から右への、入力から出力への流れを反映しています。これらのブロックは、必要に応じてさらに小さなブロックに分割することができ、最下位レベルの回路図がコンポーネントを持つことができるように、比較的シンプルな構造で、低いコンポーネント数を維持できます。各シートが比較的シンプルであるため、測定されたシートサイズを小さく保つことができ、これは回路図を印刷する際に大きな利点となります。

-

もう一つの大きな利点は、階層的な設計を通じて信号を追跡することが一般的にはるかに簡単であることです。なぜなら、読者は親シート上のシートエントリーを子シートのポートに一致させるだけでよく、各シート内の配線に沿って信号を追跡することができるからです。

階層設計を構築するには追加の作業が必要です。シートシンボルにはシートエントリが必要であり、トップシートは、あるシートシンボルから別のシートシンボルへ信号を伝達するために配線されなければなりません。ソフトウェアには、シートエントリを子シートのポートと同期させるのに役立つツールが含まれています(Design » Synchronize Sheet Entries and Portsで全てのシートシンボル、またはシートシンボルを右クリックしてSheet Symbol Actions » Synchronize Sheet Entries and Portsを選択して単一のシートシンボル)。また、大きな設計を小さなチャンクに分割するのに役立つツールも含まれています(Edit » Refactor » Move Selected Subcircuit to Different Sheet)。これらの再構築およびリファクタリングツールについて詳しくは、デザインリファクタリングページを参照してください。

階層設計は任意の深さであり、任意の数の回路図シートを含むことができます。

設計が階層的であるとは、シート間の接続が親シートのシートエントリと子シートのポートとの間でのみ発生することを意味します。この接続動作は、ネット識別子スコープの設定をAutomatic、Hierarchical、またはStrict Hierarchicalに設定することによって定義されます。

マルチチャネル設計

メイン記事: マルチチャネル設計の作成

電子設計において、回路の繰り返し部分を含むことは珍しくありません。それはステレオアンプであったり、64チャンネルのミキシングデスクであったりします。このタイプの設計は、マルチチャネル設計として知られる機能セットによって完全にサポートされています。マルチチャネル設計では、繰り返される回路を一度キャプチャし、その後、複数のシートシンボルを配置してすべてが同じ子図面を参照するようにするか、または単一のシートシンボルを設定して、必要な回数だけ参照された子図面を繰り返すように指示します。コンパイルされた設計は、コンピュータのメモリ内で展開され、ユーザー定義の命名規則に従って、すべてのコンポーネントと接続性が必要な回数だけ繰り返されます。

左側では、4つのシートシンボルが同じ子シート(PortIO.SchDoc)を参照しています。右側では、InputChannel.SchDocがRepeatキーワードによって8回繰り返されています。

左側では、4つのシートシンボルが同じ子シート(PortIO.SchDoc)を参照しています。右側では、InputChannel.SchDocがRepeatキーワードによって8回繰り返されています。

キャプチャした論理設計は実際にはフラット化されることはなく、常にマルチチャネルの回路図として保持されます。PCBレイアウトに転送すると、物理的なコンポーネントとネットが必要な回数だけステップアウトされ、回路図とボード間の作業に利用可能なクロスプロービングやクロスセレクティングツールに完全にアクセスできます。PCBエディタには、1つのチャネルの配置と配線を他のすべてのチャネルに複製するツールがあり、1つのチャネル全体を簡単に移動させたり、向きを変えたりすることができます。マルチチャネル設計のドキュメントを参照して、マルチチャネル設計についてさらに学んでください。

マルチチャネル設計は、ソフトウェアがこの構造モデルを使用してメモリ内でチャネルをインスタンス化するため、階層的でなければなりません。

マルチチャネル設計の場合、Net Identifier ScopeをAutomatic、Hierarchical、またはStrict Hierarchicalに設定します。

コンポーネントとネットの重複は、Project Optionsダイアログのマルチチャネルタブで選択された命名規則を使用してソフトウェアによって解決されます。

ネット識別子スコープの設定

ダイアログページ: プロジェクトのオプション

このソフトウェアは、Net Identifier Scopeの現在の設定を使用して、回路図シート間の接続を確立する方法を計算します。Net Identifier Scopeは、Project OptionsダイアログのOptionsタブ(Project » Project Options)で設定されます。

設計の構造に合わせてNet Identifier Scopeモードを選択します。

Global、Flat、Hierarchicalオプションの動作は、以下の画像で示されています。

3つの主要なモード、Global、Flat、Hierarchicalそれぞれで接続がどのように作成されるかの簡単な例。

上記の3つのオプションに加えて、Automaticオプションもあります。一般的に、Net Identifier ScopeはAutomaticに設定した方が良いです。ソフトウェアはシートの構造とポートやシートエントリの有無に基づいて、3つのオプションの中から最も適切なものを選択します。

Automaticに設定されている場合、ソフトウェアは以下の基準に基づいて、3つの主要なネット識別モードのどれを使用するか自動的に選択します:

-

トップシートにシートエントリがある場合、

Hierarchicalが使用されます。

-

シートエントリがないがポートが存在する場合、

Flatが使用されます。

-

シートエントリもポートもない場合、

Globalが使用されます。

Strict Hierarchicalモードでは、すべての電源ポートを各シートに局所化します。このモードでは、ポートとシートエントリを使用して、すべての電源およびグラウンドネットを各子シートに配線する必要があります。また、Strict Hierarchicalモードを使用しないで、電源ネットを局所化したいシートに対してのみ、シートエントリとポートを配置することもできます。

ネットの命名方法

Copy Link

Copied

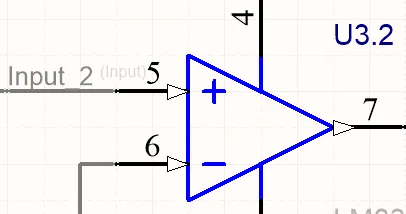

コンポーネントのピン間にワイヤーを配置するたびに、接続性を作り出しています。設計内のすべてのネットには名前が付けられます。ネットに名前を付けるために使用できるネット識別子を配置していない場合、ソフトウェアはそのネットをネット内のピンの1つに基づいて名付けます。例えば、下の画像に示されているようにNetR7_1です。コンポーネントの指定子が何らかの段階で変更された場合、そのシステム生成されたネット名も変更され、これらの変更は回路図とPCBの間で伝達され、すべてを同期させる必要があります。

ネット識別子がないネットには、ネット内のピンの1つに基づいてシステム生成された名前が割り当てられます。

ネットラベルは常に、それが接続されているネットの名前を示します。ネットラベルのデフォルトの接続点は、移動中に小さな十字で示される左下の角です。

その他のネット識別子については、Project Optionsダイアログの

Optionsタブの

Netlist Options セクションで適切なオプションが有効になっている場合、ネットに名前を付けます。

異なるタイプのネット識別子は自動的に互いに接続されません。例えば、ResetというポートはResetというネットラベルに接続されません。たとえプロジェクトのオプションダイアログでポートによるネットの命名を許可するオプションが有効になっていてもです。それらはワイヤーによって接続されなければなりません。下の画像に例を示します。

ネット上の複数のネット識別子

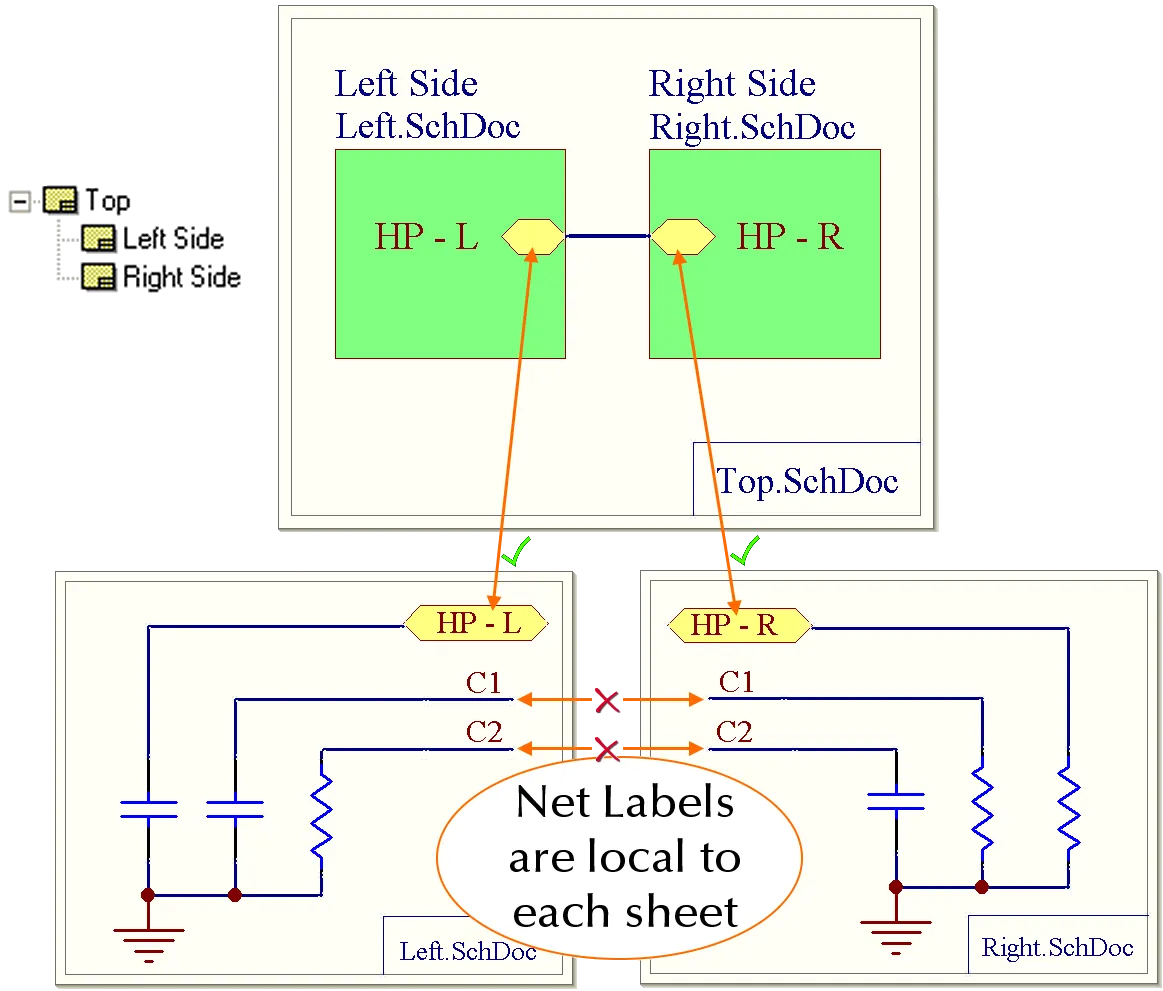

同じ回路網内で異なる名前の複数のネットラベルを持つことはできません。この状況は検証中に検出され、エラーとしてフラグが立てられます。しかし、異なるシート上でネットに複数のネット識別子を持つことは正当です。

この機能により、以下が可能になります:

-

そのシート上での機能をよりよく反映するために、階層の異なるレベルでネットの名前を変更します。

-

子回路図シートを再利用する際に、それに対するネットの名前を変更する必要がありません。

デフォルト設定では、複数のネット識別子が許可されていないと仮定されます。検証中に検出された場合、警告が表示されます。設計でそれらが必要な場合は、次のいずれかを行う必要があります:

-

エラー報告タブのProject OptionsダイアログでNets with multiple namesのエラーチェックの設定を変更するか、

-

特定の警告を抑制するために、各警告にNo ERC マーカーを配置し、No ERC モードで特定の違反を選択して、抑制するエラーを定義します。No ERC マーカーは、メッセージパネルにリストされている警告を右クリックするか、回路図シート上の違反をマークする波状の色付き線を右クリックすることで配置できます。No ERC マーカーが選択されているときに、Propertiesパネルでその形状と色を変更できます。

ネットの命名を制御するオプション

ダイアログページ: プロジェクトオプション

最終的に、PCB上の各ネットは1つの名前しか持つことができません(ネットタイを使用して2つのネットを意図的に接続する場合を除き、1つのPCBネットが2つの名前を持つことはありません)。複数の名前を持つネットは、プロジェクト内で単一の名前を持つようにソフトウェアによって自動的に解決されますが、期待した名前でない可能性があります。Project OptionsダイアログのOptionsタブのNetlist Optionsセクションには、名前が選択される方法を制御するためのいくつかのオプションがあります。 Project Optionsダイアログページを参照して、各オプションの詳細について確認してください。

これらのオプションを設定する良い方法は、

Allow Ports to Name Netsと

Higher Level Names Take Priorityオプションを有効にすることです。これらを各シート上の重要なネットに対するネットラベルの適切な使用と組み合わせることで、シートをまたがるネットを含むすべての重要なネットが命名され、上位レベルの回路図で割り当てられた名前が下位レベルの回路図で使用されることを保証します。

複数のネット命名オプションが有効になっている場合、ネットの命名順序は以下の通りです:

-

Power Port Names Take Priorityオプションがオフの場合、順序はネットラベル、電源ポート、ポート、ピンです。

-

Power Port Names Take Priorityオプションがオンの場合、順序は電源ポート、ネットラベル、ポート、ピンです。

同じ名前を持つ2つの別々のネット

Copy Link

Copied

別のネット命名の問題として、異なる回路図シート上で異なるネットに同じネット名が使用されている場合があります。これは、Duplicate Netsのエラーチェックによって検証中に検出されます。この状態が存在する場合、設計をPCBに転送することはできません。これら2つの別々のネットは、設計転送中に単一のPCBネットにマージされます。

この状況は、Project OptionsダイアログのOptionsタブでAppend Sheet Numbers to Local Netsオプションを有効にすることで解決できます。このオプションを有効にすると、すべてのローカルネットの名前にSheetNumberパラメータの値が追加されます。下の画像に示されています。

ネットラベルInputが複数のシートで使用されているため、ローカルネットにシート番号を追加オプションが有効になっており、重複ネットのエラーを防いでいます。

これの効果は、コンパイルされたシートタブ(右の画像)をクリックすることで確認できます。ネット名には_2が追加されています。

Append Sheet Numbers to Local Netsオプションは、各回路図シートに一意のSheetNumberが割り当てられている場合にのみ機能します。SheetNumberパラメータは、各回路図シートのPropertiesパネルのドキュメントオプションモードのParametersタブで割り当てられます。各回路図シートに一意の番号を手動で割り当てる代わりに、Tools » Annotation » Number Schematic Sheetsコマンドを実行することで、プロジェクトのシート番号付けダイアログが開きます。このダイアログを使用して、すべてのシートに一意のSheetNumbers(各シートに対する単純な数値)とDocumentNumbers(通常は会社が割り当てる文書番号用)を割り当てることができます。

意図的に二つのネットを接続する

Copy Link

Copied

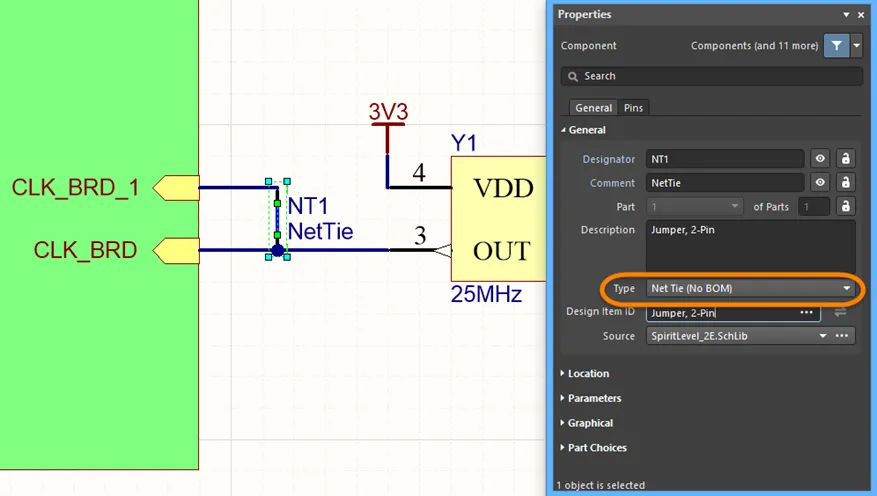

異なるネットを意図的に接続する必要がある状況があります。これは単なる命名の問題ではありません。2つのネットを設計要件としてショートさせる必要がある場合です。例えば、アナロググラウンドとデジタルグラウンドを制御された方法で接続する必要がある場合がこれに該当します。

これは、2つのネットをネットタイコンポーネントを介して接続することで実現されます。ネットタイコンポーネントとは、制御されたショートサーキットに過ぎず、ネットが接続される基板上の位置を決定することができます。回路図上では、ネットタイコンポーネントには2つ以上のピンがあり、各ピンがショートさせるネットの1つに接続されています。コンポーネントのコンポーネントタイププロパティは、以下のようにNet Tieに設定されます。

回路図上で単一のクロックを2つのFPGAクロックピンに配線するために使用されるネットタイコンポーネント。

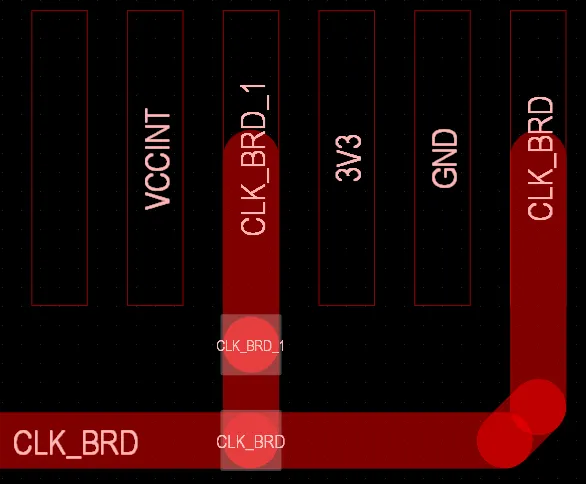

ピンは回路図上で互いに配線されていません(回路図上でショートしていません)が、PCBフットプリント内で接続されています。

PCB側では、フットプリントは回路図シンボルのピン数と同じ数のパッドを持ち、それらの間には銅が配置されています。下の例の画像では、2つの四角いパッドをトラックの長さで接続することでこれが達成されています。これはPCBライブラリエディタ内のフットプリントで行われます。PCBのComponent TypeプロパティもNet Tieに設定されます。

ソフトウェアはNet Tie PCBコンポーネント内で作成されたショートサーキットを自動的に無視するため、DRCエラーは発生しません。

PCB上の同じネットタイコンポーネント;ネットタイのフットプリント内のパッド(選択された)はトラックでショートされます。

ネットタイコンポーネントが異なる2つのネットを接続するために使用される場合、各ネットは回路図とPCB上でそれぞれ独自の名前を保持します。

-

ネットタイのシンボルとフットプリントを作成する際には、ネットタイをBOMに含めるかどうかを選択する2つのネットタイコンポーネントタイプモードがあります(例えば、ネットタイがショートジャンパーの場合はBOMに含め、ネットタイが単なる銅線の場合はBOMから除外します)- 必要なコンポーネントタイプを選択してください。

-

ボード上でネットタイを配線する場合、ネットタイパッドから離れるためにはどの配線モードも使用できます。ネットタイパッドに向かって配線するには、Ignore Obstacleモードに切り替える必要があります。

► ネットタイコンポーネントの配線デモンストレーション

パワーネット

Copy Link

Copied

設定のデフォルト動作は、パワーネットがグローバルであると仮定することです。つまり、すべての回路図シートでそれらを利用できるようにしたいと考えています。パワーネットにアクセスするには、必要なネット名でパワーポートを配置し、そのパワーポートにコンポーネントを配線します。

電源ポートがどのネットに接続されるかは、シンボルのスタイルではなくネット名によって決定されます - ハイライトされた3つの電源ポートはすべてGND電源ネットに接続されています。

電源ポートがどのネットに接続されるかは、シンボルのスタイルではなくネット名によって決定されます - ハイライトされた3つの電源ポートはすべてGND電源ネットに接続されています。

電源ネットのローカライズ - グローバルに

前述の通り、階層設計においては、

Net Identifier Scopeで

Strict Hierarchicalオプションを選択することにより、電源ネットを各回路図シートに局所化することができます。このアプローチでは、全ての電源ネットが各シート上で局所化されるため、信号ネットと同じアプローチを使用して手動で接続する必要があります。接続されていない場合、各回路図シート上に存在する各電源ネットに対して

Duplicate Net Nameエラーが発生します。また、ポートを電源ポートに接続できるように、

接続マトリックスの設定を調整する必要があります。

Net Identifier ScopeがStrict Hierarchicalに設定されている場合、使用される各シートに対してすべてのパワーネットを配線する必要があります。

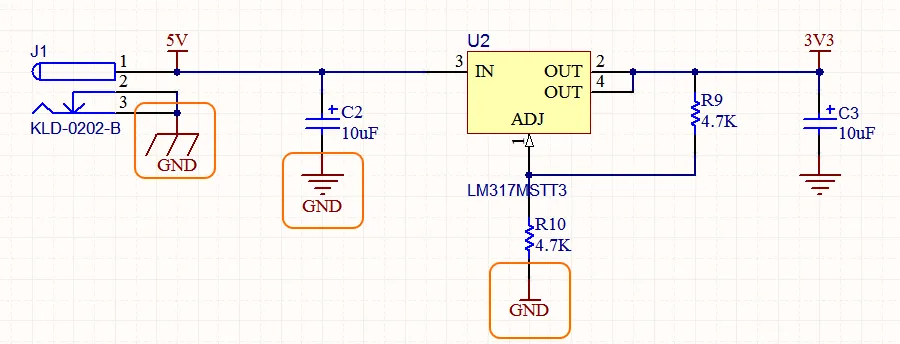

パワーネットのローカライズ - 個別に

特定の電源ネットは、その回路図シート上のポートに電源ポートを配線することで、特定のシート上で局所化することもできます。

ここでは、3V3電源ネットがこのシートのためだけに局所化されているため、親シート上でも手動で配線する必要があります。GNDと5Vのネットはグローバル電源ネットとして残ります。

パワーネットと隠されたパワーピン

Altiumの設計ソフトウェアの古いバージョンには、隠された回路図コンポーネントピンの使用をサポートする機能やオプションが含まれていました。この機能は、設計に単一のパワーネットと単一のグラウンドネットがある場合に便利で、すべてのデバイスのパワーピンをそれぞれのネットに自動的に接続することができました。これは、これらのコンポーネントのパワーピンを回路図に表示する必要がないため、マルチパートコンポーネントで最も人気がありました。

今日の電子設計では、通常、複数のパワーおよびグラウンドネットがあります。これらのネットは単に関連するパワーピンに配線されるだけでなく、パワー供給は成功したボード設計の重要な側面となっています。

パワーデリバリーネットワークの設計の性質が変わったため、コンポーネントピンを隠してソフトウェアが自動的に接続する必要性はほとんどなくなり、ほとんどの設計者がこの慣行に反対しています。このため、ソフトウェアはもはやピンを隠してネット名を事前に割り当てることをサポートしていません。この設計アプローチを使用する古いプロジェクトは、Altiumの設計ソフトウェアの最新バージョンで開いたときにも、正しくネットリストされます。

動的コンパイル

Copy Link

Copied

関連ページ: 設計プロジェクトの検証

2つのピンをワイヤーで接続するとき、実際のネットを作成しているわけではなく、設計意図を描いているだけです。プロジェクトがコンパイルされるまでネットは作成されません。コンパイルによって、コンポーネントの詳細や接続方法だけでなく、詳細なコンポーネントと設計のパラメトリック情報も抽出されます。プロジェクトのコンパイルされたモデルは、統合データモデルとして参照されます。

Altium Designer 20.0より前のバージョンでは、Unified Data Modelを構築するためにプロジェクトを手動でコンパイルする必要がありました。それ以降、デザインデータモデルはユーザー操作ごとに動的コンパイルを通じてインクリメンタルに更新され、これをDynamic Data Model (DDM)と呼んでいます。プロジェクトの手動コンパイルは一切関与せず、すべて自動的に行われます。デザインの接続モデルも、動的コンパイルのおかげでユーザー操作ごとにインクリメンタルに更新されます。デザインプロジェクトにおいて、自動コンパイルプロセスは以下の三つの機能を実行します:

-

設計階層をインスタンス化する。

-

すべての設計シート間のネット接続を確立する。

-

設計の内部Dynamic Data Model (DDM)を構築する。

これにより、行われた設計変更がすぐにナビゲーターおよびProjectsパネルに反映されます。

DDMとコンパイラ設定の間の論理的、電気的、および製図エラーをチェックするには、プロジェクトを検証する必要があります。このコマンドは、メインメニューからProject » Validate Projectコマンドを選択するか、Projectsパネルでプロジェクトのエントリを右クリックして、コンテキストメニューからプロジェクトの検証コマンドを選択することでアクセスできます。

コンパイラによって検出された違反は、Messagesパネルに警告および/またはエラーとしてリストされます。コンパイラは、ソースドキュメントの違反をチェックする際に、プロジェクトタイプに応じてProject Optionsダイアログの

エラーレポートおよび

接続マトリックスタブで定義されたオプションを使用します。

ダイナミックデータモデル

ソフトウェアの基本要素は、統合データモデル(UDM)です。このモデル内のデータは、ソフトウェア内のさまざまなエディターやサービス、回路図やPCBを含む、によってアクセスおよび操作することができます。各設計ドメインごとに別々のデータストアを使用するのではなく、UDMは、コンポーネントとその接続性を含む、設計のすべての側面からのすべての情報を収容するように構造化されています。この単一で統合されたモデルは、設計プロセスの中心に位置し、動的設計コンパイルの結果として作成されます。つまり、統合データモデルはプロジェクトが開かれた瞬間から利用可能であり、追加の手動コンパイルを必要としない、真のダイナミックデータモデル(DDM)です。したがって、モデルはユーザー操作ごとにインクリメンタルに更新(コンパイル)されます。回路図の設計から自由に配置、配線、並べ替え、名前の変更、追加、削除が可能です。

PCBデザインのコンパイルプロセスは、回路図やPCBエディターの外部でコードによって管理されます。このアプローチにはいくつかの利点がありますが、最大の利点は、デザインの統合データモデルが個々の回路図やPCBエディターの外部にあることです。UDMには、デザイン内のすべてのコンポーネントの詳細な説明と、それらがどのように接続されているかが含まれています。

ソフトウェアは、回路図とPCB間の接続データを管理します。

以下の場所と操作では、デザインのコンパイルが動的であるため、追加の手動アクションは必要ありません:

-

ナビゲーター と プロジェクト パネル

-

ActiveBOM

-

ECOの実行

-

クロスプロービング

-

ネットカラーハイライト

-

ピンスワッピング

-

コンポーネントクロスリファレンス

たとえば、設計を通じてネットをトレースするには、Unified Data Modelとどのようにやり取りしますか?それはNavigatorパネルを通じて行います。

接続性の検討

パネルページ: Navigatorパネル

設計が大きくて多くのシートにまたがっている場合、設計の接続性を追跡して確認するのが難しくなることがあります。このプロセスを支援するために、Navigatorパネルを使用できます。このパネルは、コンパイルされた設計全体のビューを提供します。

パネルを使用する基本的なアプローチは次のとおりです:

-

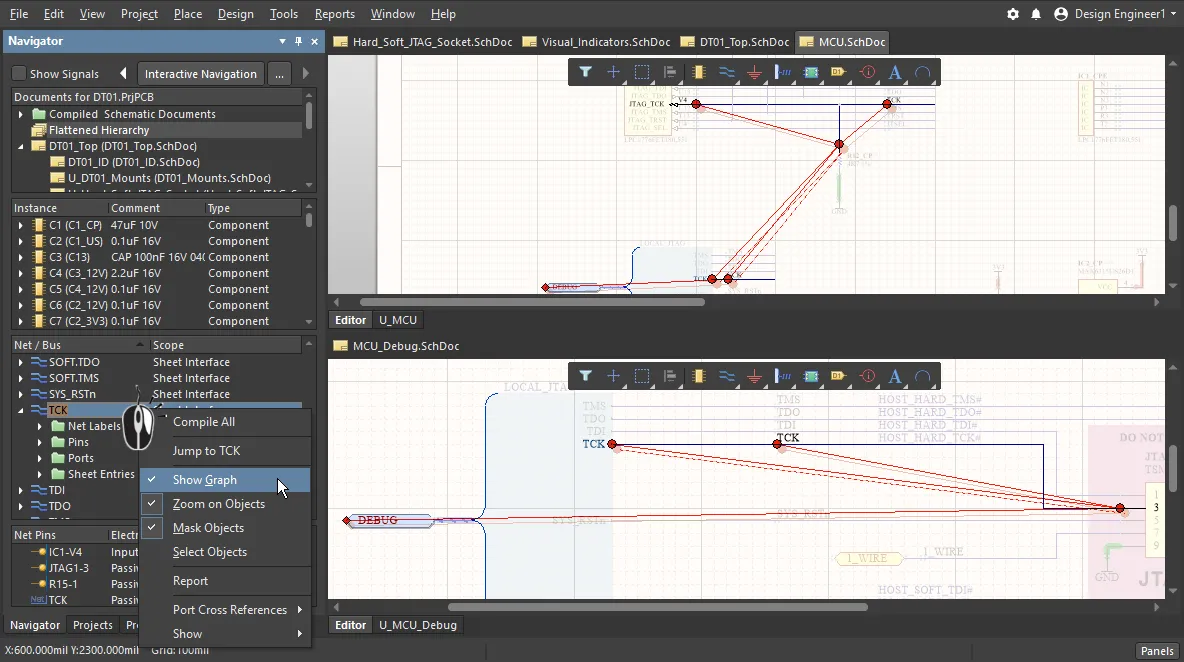

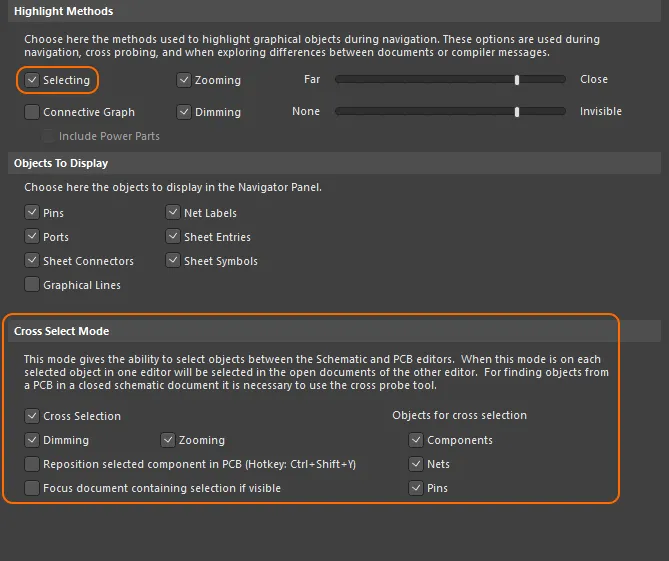

パネル上部の  ボタンをクリックしてブラウジング動作を設定し、Preferencesダイアログを開いて好みのHighlight Methodsを有効にします。または、パネル内の興味のあるオブジェクトを右クリックし、下の画像に示すようにメニューオプションを使用してナビゲーション動作を設定します。

ボタンをクリックしてブラウジング動作を設定し、Preferencesダイアログを開いて好みのHighlight Methodsを有効にします。または、パネル内の興味のあるオブジェクトを右クリックし、下の画像に示すようにメニューオプションを使用してナビゲーション動作を設定します。

-

パネルのDocuments for領域でブラウジングの範囲を設定し、全体の設計をブラウズするにはFlattened Hierarchyを選択します。

-

Instanceセクションのリストでコンポーネントをクリックすると、そのコンポーネントにジャンプし、コンポーネントを展開して所在地を見つけるか、またはピンにジャンプします。

-

Net /Busセクションでネットまたはバスをクリックすると、そのネットまたはバスにジャンプします。

-

Altキーを押しながらクリックすると、そのオブジェクトに回路図とPCBの両方でジャンプします。

Navigatorパネルでコンポーネントまたはネットをクリックして、そのコンポーネントやネットを見つけ、設計を通じて接続を追跡します。表示オプションにアクセスするには、右クリックします。画像上にカーソルを合わせると、回路図とPCB上のコンポーネントに同時にナビゲートする様子が表示されます(PCBオブジェクトを含めるには、NavigatorパネルでクリックするときにAltキーを押し続けます)。

基板上のコンポーネントのナビゲーション

Navigatorパネルから、回路図とPCB上のコンポーネントを位置決めするだけでなく(Altキーを押しながら)、回路図から直接、PCB上のピン/コンポーネント/ネット/バス/ハーネスをナビゲートすることもできます。

例えば、回路図上でコンポーネントを探すときに、その同じコンポーネントをPCB上でも見つけることができます。

これを行うには:

これらのオプションは、ナビゲーションとクロスセレクションの動作を設定します。

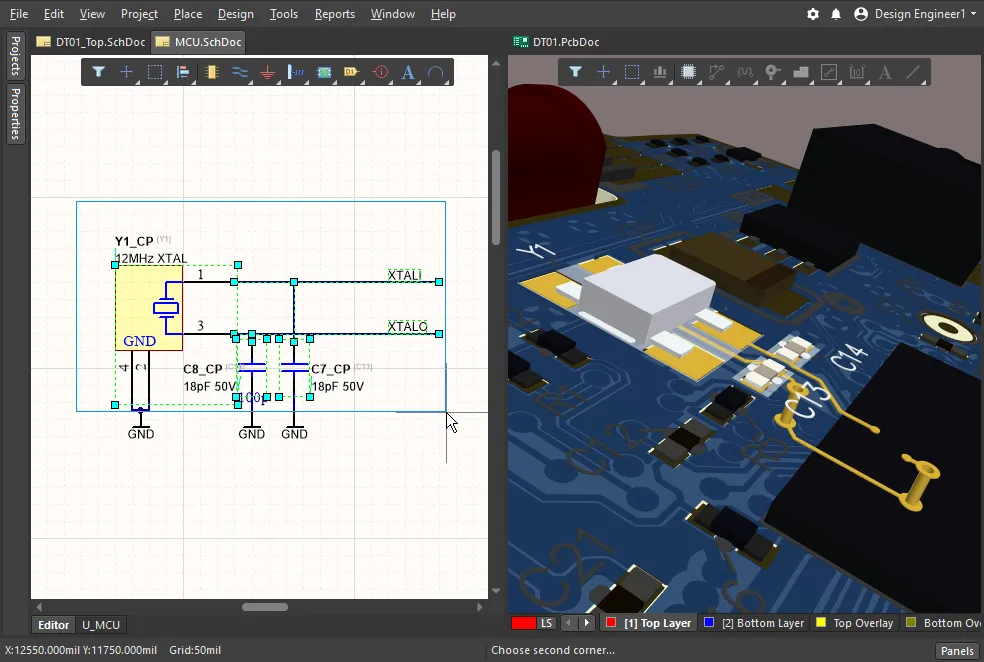

これで、回路図上でピン/コンポーネント/ネット/バス/ハーネスを選択すると、下の画像に示すように、それらのオブジェクトもPCB上で選択されます。

回路図でコンポーネントとネットを選択すると、それらのオブジェクトがPCB上でも選択されます。PCBから回路図へのクロス選択も機能します。

クロスプロービングとクロスセレクティング

エディタ間での選択(クロスセレクション)が可能であるだけでなく、ソフトウェアはクロスプロービングもサポートしています。クロスプロービングには、連続(ソースエディタに留まる)モードとジャンプ(ターゲットエディタにジャンプ)モードの2つのモードがあります。また、MessagesパネルやEngineering Change Orderダイアログなど、さまざまなパネルやダイアログからクロスプローブすることもできます。詳細については、クロスプロービングとセレクティングページを参照してください。

ネットの色の設定

Copy Link

Copied

メインページ: ネットに色を適用する

回路図をより読みやすくし、PCBエディタでネットやルートの作業を容易にするために、回路図の配線やPCBのネットおよびルートに色を適用できます。

回路図エディタでは、下の画像に示されているように、View » Set Net Colorsサブメニューのコマンドを使用して、ネットやバスにハイライト色を適用できます。これらの色は、いつでもUpdate PCBコマンドを介してPCBエディタに転送できます。

PCBエディタでは、Connection Linesのデフォルト色と可視性は、PCB View ConfigurationパネルのSystem Colorsセクションで設定されます。このデフォルト色は、ネットが作成されるとき(回路図からの初期設計転送中)に適用されるため、このオプションが変更されても、既存の接続線の色は変わりません。

PCBエディタでは、各ネットに適用された色は、PCBパネルのNetsモードで表示されます。下の画像の右下隅に示されているように、ネット名の隣のチェックボックスの背後にある色を探します。

色は常に未配線のネット(接続線)に適用されます。配線済みのネットに色を表示するには、PCBパネルのネット名の隣にあるチェックボックスを有効にし、PreferencesダイアログのBoard Insight Color Overridesページで表示オプションを設定します。下の画像では、オーバーライド色の基本パターンがSolidに設定され、ズームアウト動作がOverride Color Dominatesが優先に設定されています。

回路図に適用されたネットの色は、Update PCBコマンドによってPCBに転送されます。PCB Color Override機能を設定して、ボード上での表示方法を制御します。

回路図に適用されたネットの色は、Update PCBコマンドによってPCBに転送されます。PCB Color Override機能を設定して、ボード上での表示方法を制御します。

F5キーを押して、回路図とPCBエディターの両方でNet Color Override機能をオン/オフ切り替えます。画面のリフレッシュ(Endキー)も必要になる場合があります。

PCBのネットの色を変更する

回路図の配線に色を適用してPCBに転送することは常に可能ではありません。この状況では、PCBエディタ内で接続線と配線に色を適用することができます。設計が転送された後にネットの色を変更するには、PCBパネルのNetsモードでネット名をダブルクリックします。個々のネットの色は、Edit Netダイアログで編集できます。

複数のネットの色を変更するには、PCBパネルのNetsモードを使用します:

-

複数のネットクラスや個別のネットを選択するには、標準のWindowsマルチセレクト技術(Shift+クリックまたはCtrl+クリック)を使用します。

-

選択したオブジェクトを右クリックし、コンテキストメニューからChange Net Colorコマンドを選択して、選択したネットに新しい色を割り当てます。

-

もう一度右クリックして、Display Override » Selected Onを選択し、選択したネットに対して色のオーバーライド機能を有効にします。

接続線の色を変更し、表示オーバーライド機能を有効にすることで、ネットの視認性を向上させます。