Parent page: Finalizing the Board Design

Testing is an important part of the board manufacturing process. After fabrication, the board is typically tested to ensure no short or open circuits. Once fully populated with all its components, a board is often tested again to ensure signal integrity and device operation. To aid in this process, it is fundamentally beneficial to have a scheme of points on the board - Testpoints - which the testing equipment can probe and perform the required tests.

The location of testpoints on a board will depend on factors including the mode of testing (including bare-board fabrication testing, in-circuit assembly testing, etc..) and the method of testing (including automated testing using flying probe and bed-of-nails fixtures, hand testing, etc..). For example, when performing bare-board fabrication testing, the board is not populated and so all pads and vias are 'fair game' when it comes to assigning testpoints. The locations used for testpoints when performing in-circuit assembly testing however, will almost always be different. As the board is populated, you may no longer have probe access to component pads and certainly no access to pads and vias under a component!

Altium Designer provides a powerful system to handle your testpoint needs and enhance the testability of your boards, allowing you to separately assign testpoints for bare-board fabrication testing and/or in-circuit assembly testing as required. Testpoints can be assigned manually, or in a more streamlined and automated fashion, by using the Testpoint Manager dialog.

Considering Your Testpoint Strategy

Before jumping into the assignation of pads and vias for use as testpoint locations, it is a good idea to step back and think about what is required. The following are just some pointers to consider when defining a strategy to incorporate testpoints into a design:

- When choosing the side of the board that testpoints will be allowed on, consideration should be given to the testing processes and associated fixtures that will be used. For example, will the board be probed from the bottom side only, the top side only, or both sides.

- A testpoint underneath a component (on the same side of the board as the component) is usually used at the bare-board testing stage. This should be taken into consideration when planning testpoint locations for assembled board testing.

- It is advisable to locate all testpoints on one side of the board only, using vias to achieve this if necessary. The reason for this lies in the fact that a dual-head test fixture incurs greater cost than a single-head test fixture.

- The more non-standard and complex your pattern of testpoints, the more costly it will be to configure a fixture with which to test the board. The best philosophy is to develop a methodology that will result in generic testability. A well-honed and adaptable testpoint policy will allow different designs to be tested efficiently and cost-effectively.

- Careful consideration should be given to any via tenting requirements of the design. Tenting a testpoint-designated via will effectively block test probe contact. Even partial tenting using a liquid photoimageable (LPI) solder mask will cause contact problems, as the mask liquid will tend to run away through the via hole. Peelable solder mask may indeed be used to provide temporary tenting of such designated vias, but this can often prove quite costly.

- Consult with your fabrication and assembly houses closely to make sure any specific design parameters are taken into account when specifying testpoints. These could include testpoint-to-testpoint clearances and testpoint-to-component clearances that may be more strict than normal placement and routing clearances.

The following sections take a closer look at fabrication and assembly testing, including specific testpoint constraints and considerations associated with each.

Fabrication Testing

Fabrication testing relates to the testing of a printed circuit board at the pre-assembly phase of manufacture, before any components have been placed onto the board. As such, it is often referred to as bare-board testing. This method of testing might typically involve the use of a flying probe device to perform net-by-net testing. Essentially, two probes are programmed to operate in concert, one to pulse a signal through a net and the other to detect the presence (or absence) of that signal.

Two common test scenarios for bare-board fabrication testing are:

- Test to ensure that intentional end-to-end contiguous copper carries a clean signal (under a maximum permissable impedance threshold) without any open-circuits.

- Test to ensure that nets are not shorted to each other.

Testpoint Location Constraints

- Dedicated testpoint pads/vias are usually not necessary for fabrication testing. As the board is not yet loaded with components, the probes enjoy free access to component pads. Since the pads tend to be free of solder mask at this stage, the testpoints are typically located directly on the pads themselves.

- Flying probe tests are not constrained by a grid, as flying probe devices are capable of quite precise locations.

- Each location pair is constrained by a minimum separation - due to the physical body size of the probe heads.

Exceptions and other Considerations

- For fine pitch devices, it may not be possible (or even practical) to probe a single component pad. Such copper features can be miniscule and delicate, so it is occasionally recommended that they avoid contact with test probes. In these instances, it can be a good idea for the designer to add dedicated test pads/vias to the board.

- A bed-of-nails fixture can also be used during bare-board fabrication testing. This is typically the case for high-volume manufacturing runs, where use of such a fixture involves less testing time than a flying probe. However, bed-of-nails testing can involve more rigid testpoint location constraints and, if the test fixture is not a customized one, will often require that the testpoints conform to a specific grid.

- There are occasions where specific pairs of testpoint locations are not tested in-concert by a flying probe. This is typically the case when there is no danger of a short (or crosstalk) between nets, as the nets are not adjacent to each other (all objects of both nets are mutually separated by their physical proximity).

Assembly Testing

Assembly testing relates to the testing of a printed circuit board at the post-assembly phase of manufacture, after the board has been populated with all components specified in its associated Bill of Materials (BOM). As such, it is often referred to as in-circuit or electrical testing. This method of testing typically involves (but is in no way limited to!) the use of a manually-configured bed-of-nails fixture. Depending on the type of testing being performed using the fixture, the board may or may not be powered up.

Two common test scenarios for in-circuit assembly testing are:

- Simultaneously probe one dedicated testpoint for each net (or net of interest). This is done by pulsing a signal through each probe individually and detecting signal reception results by all other probes.

- Test specific components/buses to ensure that the device itself is operating properly. These are specialized tests that can be conducted using a variety of testing methods. In the simplest case, a bed-of-nails fixture can be used to test across component pads.

Testpoint Location Constraints

- Testpoint locations typically need to conform to a minimum spacing requirement. Test equipment, such as bed-of-nails fixture probe heads, have a body size that constrains their proximity to each other. Unless a custom fixture is used, testpoint locations are often required to be on a specific grid. Fabricating a custom fixture is more costly and time-consuming than configuring a reusable bed-of-nails fixture.

- Testpoints can be required to be located according to a minimum clearance with respect to component bodies. The probe heads of most test fixtures tend to be larger nearest the fixture, tapering down to a smaller size as they approach the shank of the probe. Taller components require more clearance. It is therefore best to consider the maximum component height on the board and define an overall body clearance that factors in this worst-case scenario.

- Testpoint locations can be required to be positioned according to a minimum clearance with respect to the board edge. The process of contacting the board with a flying probe pair or a bed-of-nails array of probes can be tough on the board itself, and the board may flex to some extent under the strain of automated testing. For this reason damage to thin, fragile boards, is minimized when testpoints are located at a distance from the board edges.

- A dedicated probe-accessible testpoint pad/via is usually required to be added to each net during design for several reasons:

- Bare copper component pads are usually rendered inaccessible to the presence of placed components.

- Unless the board is specifically designed with testing in mind, component pads and vias are not likely to be located on the required testpoint grid.

- Even if a component pad itself seems suitable to be used as a testpoint location, clearance constraints to the component body often prevent its use.

Exceptions and other Considerations

- While bed-of-nails fixtures are a common method of assembly testing, it is by no means the exclusive method. Among the variety of alternatives are cases where flying probe devices are used - with care, so as not to collide with placed components.

- When performing an electrical test on a specific component, the component pads might be accessible by a test probe to some degree. However, it is important to note that the component body often obscures the center of such pads. In other words after the board has been assembled, the accessible portion of the pad rarely includes the pad center location.

Pad and Via Testpoint Support

Altium Designer provides full support for testpoints, allowing you to specify pads (thru-hole or SMD) and/or vias to be used as testpoint locations in fabrication and/or assembly testing. A Pad or Via is nominated for use as a testpoint by setting its relevant testpoint properties, and answering two key questions:

- Should the pad/via be used as a fabrication and/or assembly testpoint?

- On which side of the board should the pad/via be used as a testpoint - Top, Bottom, or both?

These properties can be found in the Properties panel, when a pad (see Pad Properties) or via (see Via Properties) object is selected in the design workspace, respectively.

A selected pad or via is specified for use as a testpoint through the relevant options available for it, through the Properties panel.

A selected pad or via is specified for use as a testpoint through the relevant options available for it, through the Properties panel.

To streamline the process and alleviate the need for setting the testpoint properties of pads/vias manually, Altium Designer provides a method to automatically assign testpoints based on defined design rules, and using the

Testpoint Manager. This automated assignment sets the relevant testpoint properties for the pad/via in each case. You of course have the option to manually specify testpoints - in essence, handcrafting at the individual pad/via level - giving you full control over the testpoint scheme employed for your board.

When opening PCB designs created in a release of the software prior to the Summer 09 release, any enabled testpoint options will become enabled Fabrication testpoint options.

Testpoint Design Rules

The constraints of a PCB design should be thought out and implemented as a well-honed set of design rules. To implement a successful testpoint scheme - where all defined testpoints can be accessed and used as part of the bare-board and/or in-circuit testing - governing constraints must be put in place. To this end, the following rule types are definable as part of the PCB Editor's Design Rules system:

Access and define rules of these types from the PCB Rules and Constraints Editor dialog (Design » Rules).

Define separate design rules to constrain which pads and/or vias in the design can be used as Fabrication testpoints and Assembly testpoints, and which nets require testpoints.

Define separate design rules to constrain which pads and/or vias in the design can be used as Fabrication testpoints and Assembly testpoints, and which nets require testpoints.

The Testpoint Style and Usage rules are identical, in terms of constraints, between the two testing modes (fabrication and assembly). The style rule essentially specifies constraints that a pad or via has to meet in order to be considered for selection as a testpoint location. The usage rule specifies which nets require a testpoint.

Default constraints for both Testpoint Usage (top) and Testpoint Style (bottom) rules.

Default constraints for both Testpoint Usage (top) and Testpoint Style (bottom) rules.

When defining a style rule, the rule scope can be quickly created to target the precise pad and/or via objects for testpoint consideration, using the options available in the Rule Scope Helper region.

The testpoint design rules are used by the Testpoint Manager, the Autorouter, Online and Batch DRC processes and also during output generation.

Default Fabrication and Assembly Testpoint Style and Testpoint Usage rules exist. You should check whether these rules meet your board requirements and make changes as necessary. If multiple rules of the same type are required, use the priority aspect of design rules to ensure that rules with more specific scoping are applied first (for example when running a DRC).

For the Testpoint Manager to successfully assign testpoints, there must always be at least one corresponding Testpoint Style rule with a scope of All.

When opening PCB designs or importing design rules created in a release of the software prior to the Summer 09 release, Testpoint Style rules will become Fabrication Testpoint Style rules and Testpoint Usage rules will become Fabrication Testpoint Usage rules.

Managing Testpoints

Assigning testpoints manually can be a painstaking and laborious job, and even more so on a complex board, populated with hundreds of components (and across both sides of the board). To cater for streamlined management of testpoints in your board designs, Altium Designer equips the PCB Editor with a Testpoint Manager. The Testpoint Manager allows you to assign testpoints - for bare-board fabrication testing and/or in-circuit assembly testing - in an automated fashion, based on defined design rules. This automated assignment sets the relevant testpoint properties for the pad/via in each case.

Access is made by choosing the Tools » Testpoint Manager command, from the main menus.

Manage your fabrication and assembly testpoint requirements quickly and efficiently using the Testpoint Manager.

Manage your fabrication and assembly testpoint requirements quickly and efficiently using the Testpoint Manager.

Use the dialog to automatically assign and clear testpoints from the one convenient location. A listing of all nets in the design is provided, with status to indicate testpoint coverage - either Complete or Incomplete - for both bare-board fabrication and in-circuit assembly testing. Click the Fabrication Testpoints or Assembly Testpoints buttons to access commands for assigning or clearing that type of testpoint. Note that you can manually select nets in the upper region of the dialog to selectively assign/clear testpoints.

Whether assigning testpoints for some or all of the nets in a design, the Testpoint Manager follows the style and usage rules defined for fabrication and assembly testpoints. To see the order that valid objects are searched, click the Search Order button.

To change the order, right-click on an entry in the search order list and use the floating menu commands, or the Shift+Up Arrow and Shift+Down Arrow shortcuts to move it up or down in the list.

The Status Summaries region provides a full summary of the testpoint status for the board, for both testing modes. This region updates with each assignment or clearance action performed. For more lower-level detail, use the Assignment Results region. This will give detail, for example, on the number of top/bottom pads/vias involved in an assignment/clearance, along with an indication of failures.

Checking the Validity of Testpoints

Defined fabrication and assembly testpoint rules are followed as part of the PCB Editor's Design Rule Checking (DRC) facility. Online and/or Batch DRC checking can be enabled for the various rule types from within the Design Rule Checker dialog (Tools » Design Rule Check).

Include testpoint design rules as part of the Online or Batch DRC processes.

Include testpoint design rules as part of the Online or Batch DRC processes.

Testpoint-related Query Fields

In support of the various fabrication and assembly testpoints that can be assigned in a design, the following keywords are available for use when targeting testpoints using logical query expressions. Each of the following can be found in the PCB Functions - Fields category, when using the Query Helper:

IsAssyTestpoint - is an assembly testpoint.IsFabTestpoint - is a fabrication testpoint.IsTestpoint - is a Top or Bottom side testpoint.Testpoint - is it a Top or Bottom side testpoint?TestpointAssy - is it an assembly testpoint?TestpointAssyBottom - is it a Bottom side assembly testpoint?TestpointAssyTop - is it a Top side assembly testpoint?TestpointBottom - is it a Bottom side testpoint?TestpointFab - is it a fabrication testpoint?TestpointFabBottom - is it a Bottom side fabrication testpoint?TestpointFabTop - is it a Top side fabrication testpoint?TestpointTop - is it a Top side testpoint?

Create logical expressions for queries to target and return testpoints in your design as required. Some examples of logical query expressions targeting fabrication and assembly testpoints are:

(ObjectKind = 'Pad') And (TestpointAssy = 'True')

Targets all pads that are assembly testpoints.IsPad And (TestpointAssyTop = 'True')

Targets all pads that are Top side assembly testpoints.(ObjectKind = 'Pad') And (TestpointFab = 'True')

Targets all pads that are fabrication testpoints.((IsPad Or IsVia)) And (TestpointAssy = 'True')

Targets all pads and vias that are assembly testpoints.((IsPad Or IsVia)) And IsFabTestpoint

Targets all pads and vias that are fabrication testpoints.

Generating Testpoint Reports

Altium Designer includes dedicated report generators for generation of fabrication and assembly testpoint reports respectively. These two report generators utilize the relevant testpoint properties for the pad and via primitives in a design.

A fabrication testpoint report will only use pad and via Fabrication testpoint settings. An assembly testpoint report will use only Assembly testpoint settings.

Reports can be generated in two ways:

- Directly from within the PCB document, using the File » Fabrication Outputs » Test Point Report and File » Assembly Outputs » Test Point Report commands.

- By using appropriately configured outputs defined in an Output Job Configuration file (

*.OutJob).

Include and configure fabrication and assembly testpoint report outputs within a self-contained and versatile Output Job Configuration file. Once defined, obtain your reports at the touch of a button!

Include and configure fabrication and assembly testpoint report outputs within a self-contained and versatile Output Job Configuration file. Once defined, obtain your reports at the touch of a button!

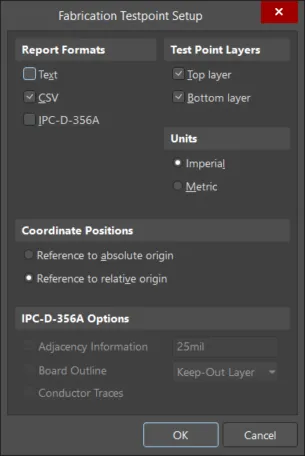

Regardless of the method used to generate a report, the report options themselves are defined in the same dialog. For a fabrication testpoint report, this involves the Fabrication Testpoint Setup dialog. For an assembly testpoint report, the Assembly Testpoint Setup dialog is used. Report options are identical between these dialogs.

Define report options, including generated file format, using the relevant report setup dialog.

The settings defined in a Testpoint Setup dialog when generating output directly from the PCB are distinct and separate to those defined for the same output type in an Output Job Configuration file. In the case of the former, the settings are stored in the project file, whereas for the latter they are stored in the Output Job file.

The options in the Coordinate Positions region of a dialog allow testpoint locations in all report formats to be exported relative to the absolute board origin, or the current board origin.

All testpoint report types support embedded board arrays. Multiple IPC-D-356A netlist files are produced when exported from a PCB document that contains multiple embedded board arrays.

Role of the IPC-D-356A Netlist File

One of the three flavours of testpoint report output formats is an IPC-D-356A netlist file. This file is typically used to target the bare-board fabrication testing mode. The IPC file is post-processed into commands that drive a flying probe testing device.

Regardless of which features are specifically identified as test point locations in an IPC-D-356A file, board fabrication houses can generally use the file data to achieve whatever type of testing that they want although, depending on circumstances and the content of the file, it may require some manual intervention to do so.