多图纸和多通道设计

软件的功能取决于您购买的Altium产品级别。您可以比较Altium Designer软件订阅的各个级别中包含的功能,以及通过Altium 365平台提供的应用程序所能实现的功能。

如果您在软件中找不到某个讨论过的功能,请联系Altium销售团队以获取更多信息。

父页面: 关于原理图的更多信息

原理图最初是在足够大的单张纸上捕获的,这张纸足以填满一个大型绘图台,然后在专用的大幅面复印机上复制。时代变了,现在原理图是在桌面电脑上捕获的,存储在服务器上,并通过小幅面激光打印机打印。

这种变化意味着,即使是简单的设计,如果能在多个原理图纸张上展示,也会更容易被显示和理解。即使设计并不特别复杂,在多个纸张上组织它也有优势。

例如,设计可能包括各种模块化元素。将这些模块作为单独的文档维护,可以让多个设计师同时在一个项目上工作。将设计分解成逻辑模块也极大地增强了设计的可读性,这对于那些需要在产品生命周期后期阅读和解释原理图的人来说是一个重要的考虑因素。另一个优势是,当设计在多个纸张上结构化,每张纸上的组件较少时,可以使用小幅面打印,例如激光打印机。

如果你计划将设计分布在多个纸张上,有两个决定要做:

- 纸张之间的结构关系,以及

- 在这些纸张上的电路之间实现电气连接的方法。

你的选择将根据每个项目的大小和类型,以及你的个人偏好而有所不同。

扁平或层次化设计 Copy Link Copied

如前所述,作为设计师,你需要决定原理图纸张是如何组织的,以及如何在这些纸张之间建立连接性。这些不是独立的决定,因为当你选择结构时,你也需要选择如何创建这些纸张之间的连接。

有两种方法来构建多纸张设计:要么是扁平,要么是层次化。

扁平设计

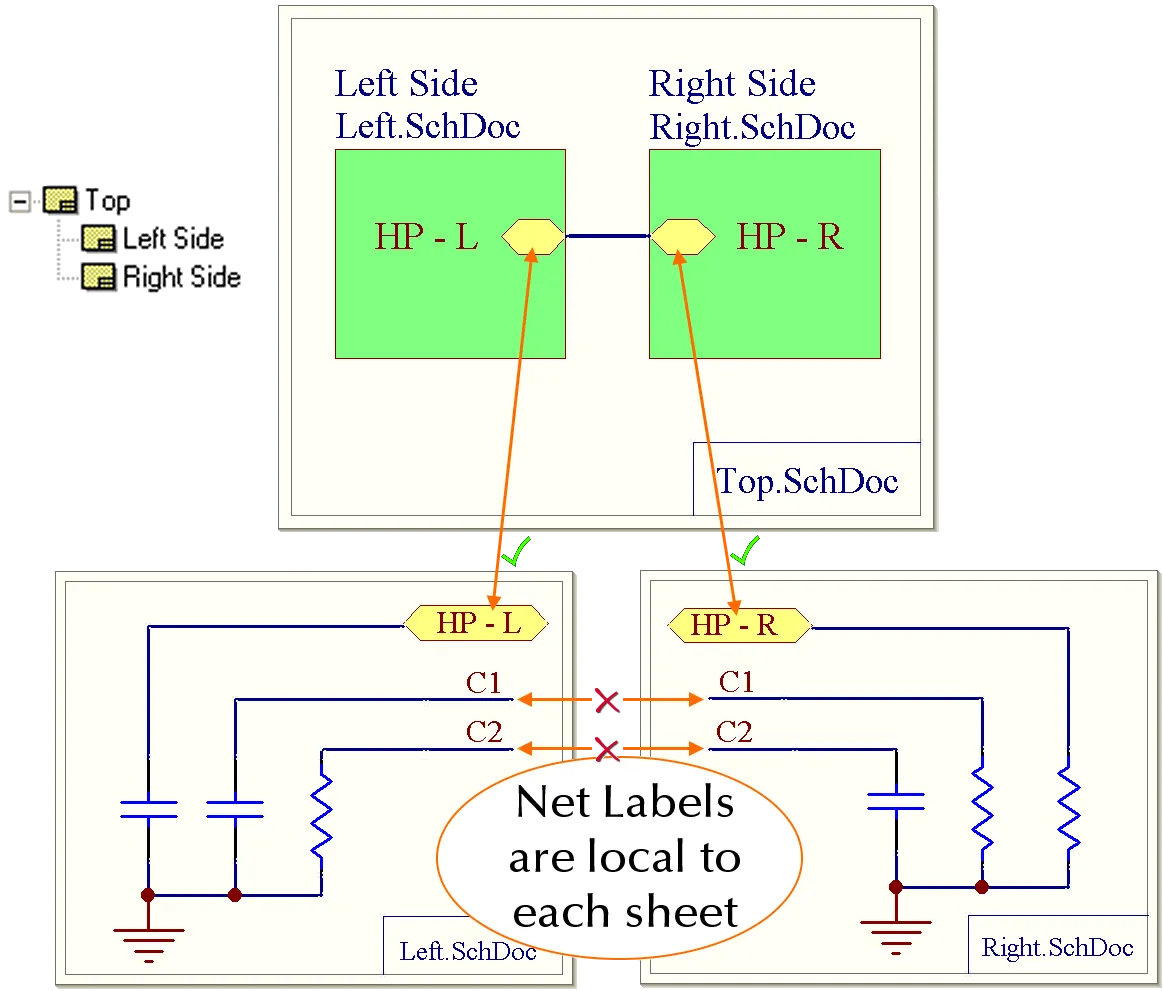

你可以将扁平设计想象为一个大的原理图纸张被切割成许多小纸张 - 在扁平设计中,所有纸张都存在于同一层面上。扁平设计中的连接性是直接从任何一张纸张到任何其他纸张创建的 - 这种类型的连接性被称为水平连接性。

在扁平设计中使用顶层纸张是可选的。如果包括一个顶层纸张,它将有一个纸张符号代表设计中的每一张纸张,但不能包括任何接线。扁平设计中可以有任意数量的纸张。

第一张图片 - 扁平设计没有顶层纸张;第二张图片 - 相同的设计有一个顶层纸张。注意顶层纸张没有接线。它只是显示了设计中的纸张。

上面的两幅图像都展示了一个平面设计,左边的版本没有顶层图纸,右边的版本有。对于只有两到三张原理图纸的小型设计,你可能会决定顶层图纸并不增加任何价值。一旦图纸数量增多,顶层图纸可以帮助读者从逻辑块(图纸符号)在图纸上的排列方式来理解电路设计的功能。所有的设计图纸在项目面板中显示在同一层级,因为没有层次结构。

层次化设计

层次化设计是指通过图纸符号创建图纸之间的父子类型关系,并且,连接是通过这些图纸符号中的图纸入口来实现的 - 而不是直接从一个图纸上的端口到另一个图纸上的端口。

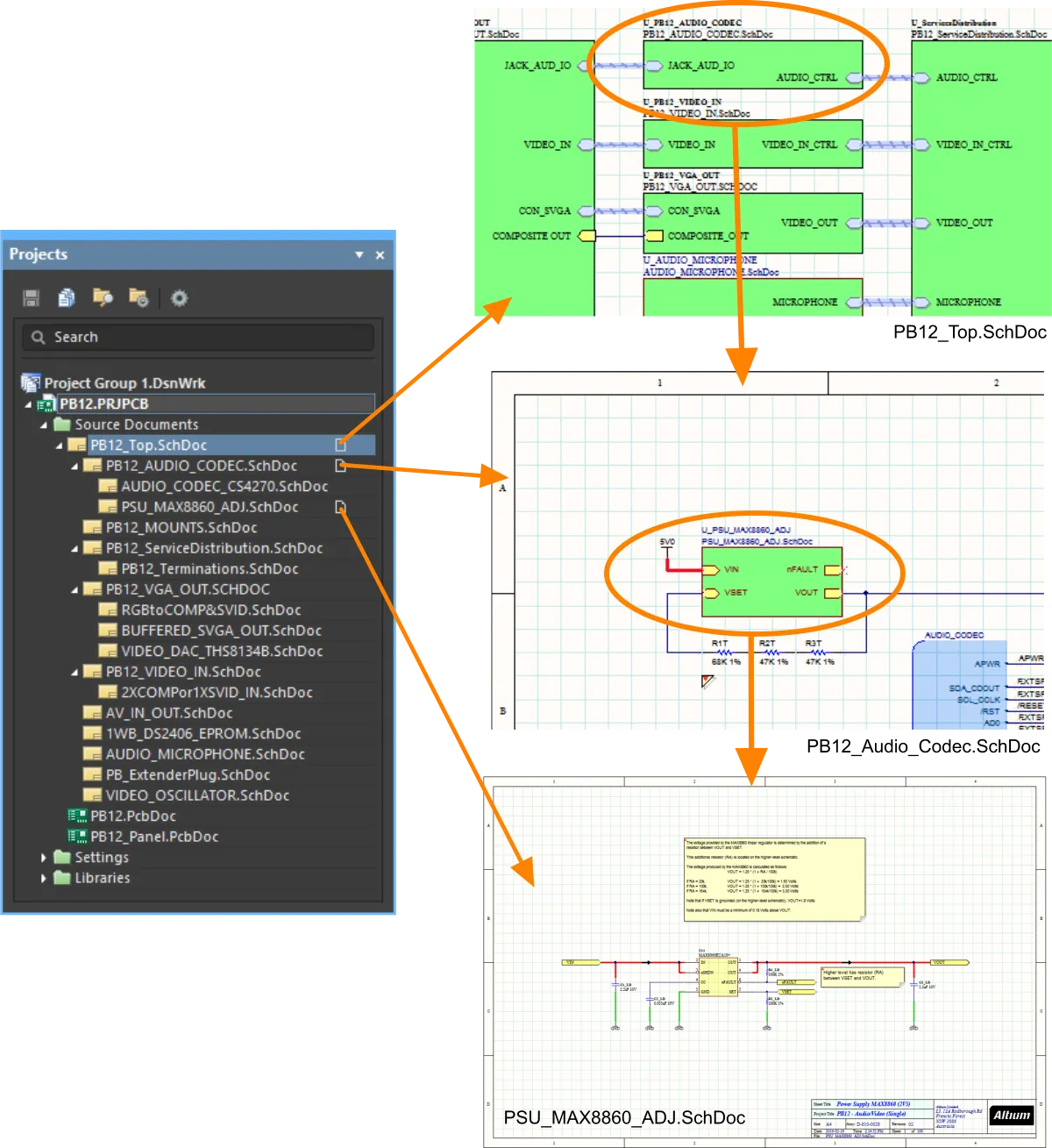

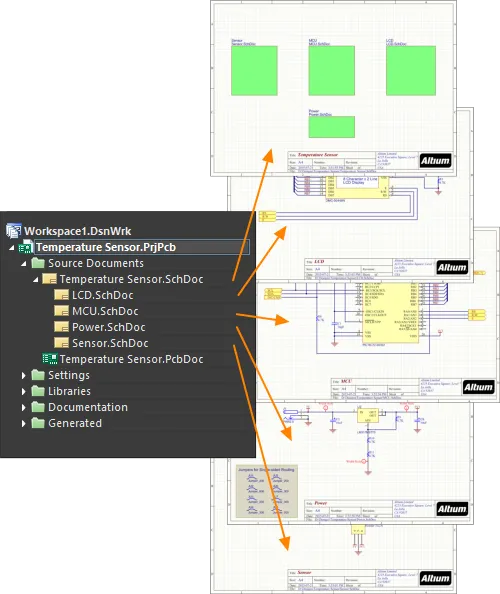

就像在平面设计中一样,通过在图纸符号中定义其文件名来识别子图纸。在层次化设计中,子图纸还可以包括图纸符号,引用更低级别的图纸,从而在层次结构中创建另一个层级。下面的图片显示了一个具有3个层次的层次化设计。

在层次化设计中,子图纸上的信号通过端口离开图纸,向上连接到父图纸上图纸符号中的匹配图纸入口。父图纸包括将子信号跨越到另一个图纸符号中的图纸入口的布线,然后它向下到第二个子图纸上的匹配端口,如下图所示。

这种父子图纸结构可以定义到任何深度,并且在层次化设计中可以有任意数量的图纸。

创建多表设计 Copy Link Copied

一旦您向项目中添加了第二个原理图表,您就创建了一个多表设计。如果您打算创建一个没有顶层表的平面设计,您只需继续向项目中添加原理图表,并确认网络标识符范围设置正确。

如果您想使用表符号来引用下级表,您可以放置表符号并手动编辑它以正确引用下级表,或者您可以使用下面描述的各种内置命令来帮助操作。

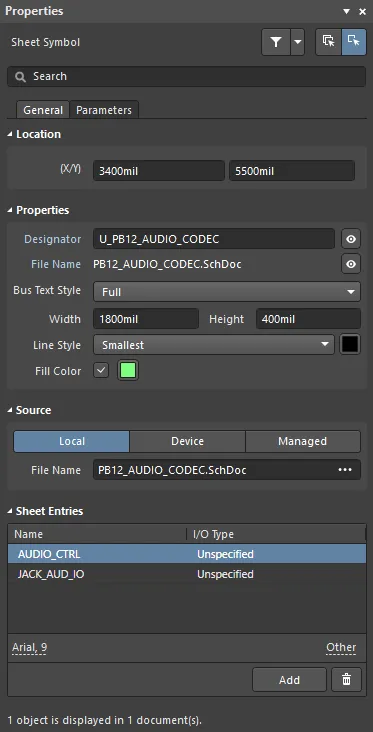

引用子表

是表符号的文件名属性引用了下级表。请注意,此字段应仅包括原理图文件名,而不是该文件位置的路径(该位置数据实际上存储在项目文件中)。

创建层次结构 Copy Link Copied

该软件包括许多命令,允许您快速高效地构建多文档的层次结构。您使用的命令将取决于您的个人设计方法 - 可以广泛分类为自顶向下或自底向上。这些命令比手动创建层次结构更有效,因为它们处理了过程中需要的所有元素,例如添加表条目,创建新的原理图表,放置端口等。

使用此命令以自顶向下的方式构建层次结构:

- 设计 » 从表符号创建表 – 使用此命令在指定的表符号下创建一个新的原理图表。子表中添加端口以匹配表符号中找到的任何表条目。如果您还没有在表符号中包含所有的表条目,也不用担心,随着时间的推移如果添加了更多的表条目,您可以重新同步表条目和端口,如下所述。

使用此命令以自底向上的方式构建层次结构:

- 设计 » 从图纸创建图纸符号 - 使用此命令从指定的原理图图纸创建一个符号。使用此命令前,首先切换到将包含新图纸符号的图纸,然后启动命令。图纸符号将包括一个与其发现的每个端口相匹配的图纸入口。如果端口或图纸入口在后期被添加或移除,它们可以重新同步,如下面讨论的。

使用此命令重新组织设计中电路的放置:

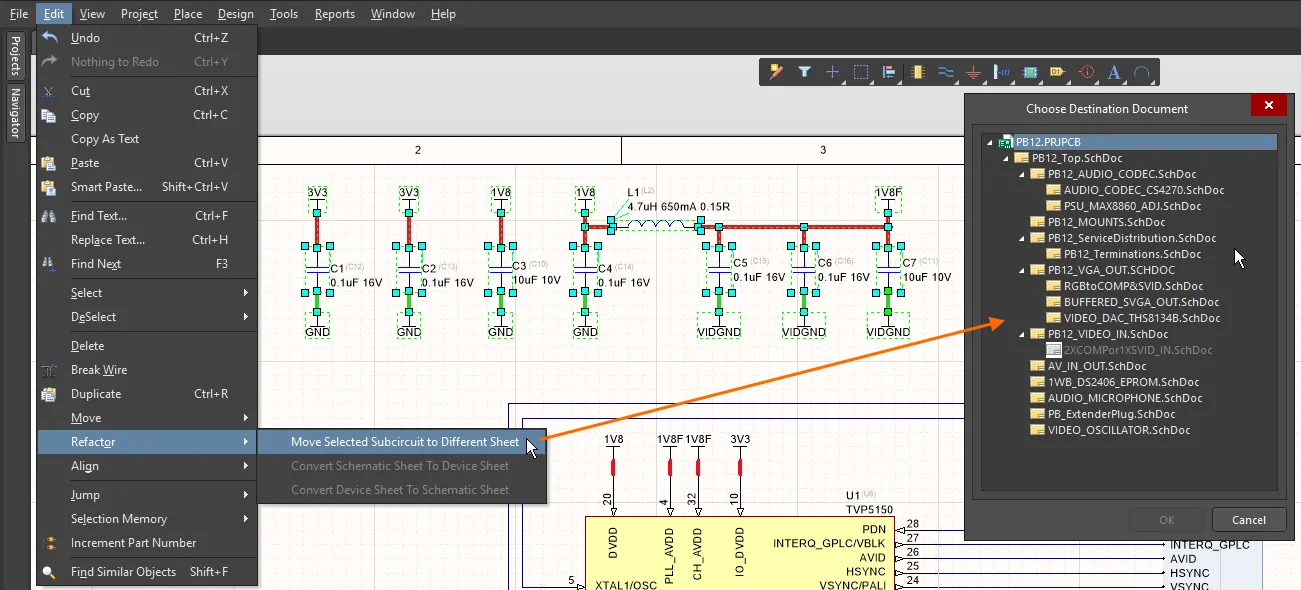

- 编辑 » 重构 » 将选定的子电路移动到不同的图纸 - 使用此命令将选定的组件和布线移动到项目中的不同图纸。将打开选择目标文档对话框,允许您选择项目中的任何现有原理图。此命令将在下面更详细地描述。

重构设计 Copy Link Copied

主文章: 设计重构

设计过程通常是非结构化和有机的,设计师可能同时在设计的多个部分构思想法,捕捉他们的想法演变的部分。这意味着,最初组织良好、布局整齐的原理图集可能变得拥挤且组织不良。虽然你可以剪切、复制和粘贴来重新组织原理图设计,但这并不总是最好的方法。

为什么不剪切和复制?因为每个组件放置时都会被分配一个唯一标识符,而这个标识符在组件被剪切/复制和粘贴时会自动重置。这种UID管理是为了确保设计中只使用了每个UID的一个实例,因为它是将原理图组件与PCB组件链接起来的关键字段。如果设计尚未转移到PCB编辑器,剪切/复制/粘贴方法是可以的,但如果已经转移,则最好使用重构工具。

将子电路移动到另一个图纸

将电路的一部分从一个图纸移动到另一个图纸的最简单方法是选择它,然后运行编辑 » 重构 » 将选定的子电路移动到不同的图纸命令。将打开选择目标文档对话框,选择目标图纸并点击确定后,目标图纸将出现,子电路将浮动在光标上,准备定位。

可以使用将选定的子电路移动到不同的图纸命令轻松地将选定的电路部分移动到项目中的不同图纸。

► 了解更多关于设计重构。

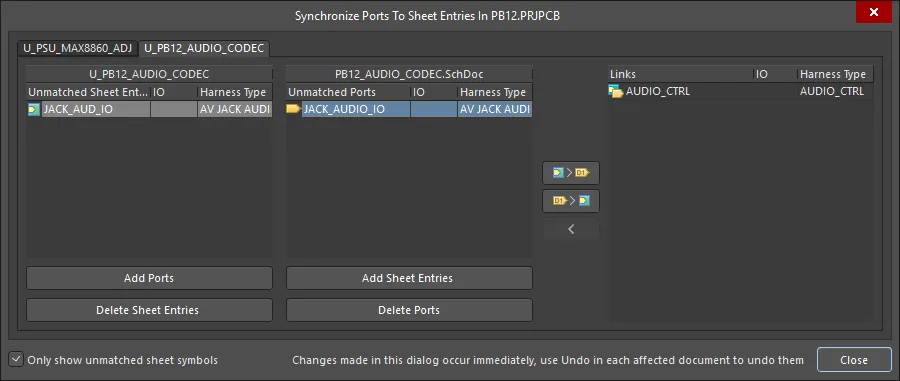

同步端口和表单项

如果您在重构设计时移动了组件和布线,那么您可能还需要重新同步子表单到其表单符号,以确保每个端口都有匹配的表单项。这可以通过使用同步表单项和端口命令来完成,您可以用它来:

- 特定的表单符号 - 右键点击表单符号以显示上下文菜单,并选择表单符号操作 » 同步表单项和端口命令来仅分析光标下的表单符号。

- 设计中的所有表单符号 - 选择设计 » 同步表单项和端口命令来分析整个设计中的所有表单符号,对话框将包括设计中每个表单符号的标签页,根据对话框底部的仅显示不匹配的表单符号选项。

对于这两个命令,同步端口到表单项对话框将会打开。它将在对话框的右侧列出已经匹配的端口/表单项,未匹配的端口和表单项将在对话框左侧的两列中列出。

同步端口到表单项对话框用于确保表单项与子表单上的端口匹配。

注意两个标签页,这意味着在这个设计中有两个表单符号存在表单项/端口不匹配。

关注对话框左侧显示的不匹配项,思路是在第一列中选择表单项,然后在第二列中选择正确的端口,然后点击对话框中间的所需按钮来更新其中一个,以便它们同步(并移动到对话框右侧的列表中)。

按钮的功能如下:

-

- 使用表单项的属性,并将它们推送到所选端口。

- 使用表单项的属性,并将它们推送到所选端口。 -

- 使用端口的属性,并将它们推送到所选表单项。

- 使用端口的属性,并将它们推送到所选表单项。

如果在左侧列中选择了多个表单项,软件将同步每个表单项与第二列中相邻的端口。如果没有相邻的端口(或表单项),将创建一个新的。

多通道设计 Copy Link Copied

电子设计中包含重复电路部分并不罕见。它可能是立体声放大器,也可能是64通道混音台。这种设计完全得到了一套称为多通道设计的功能集的支持。

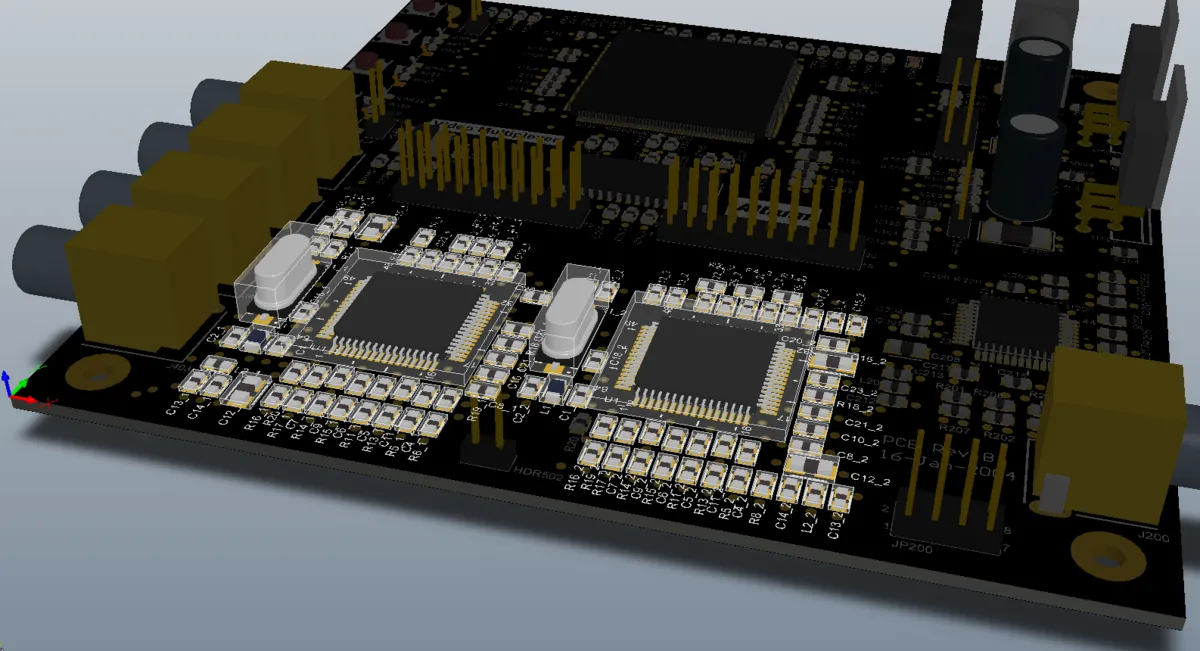

视频多路复用器的两个解码器通道,使用多通道设计结构意味着解码器通道只需捕获一次。

在多通道设计中,你只需捕获一次重复电路,然后指示软件重复所需次数。当设计自动编译时,它会在内存中展开,所有组件和连接都会根据用户定义的通道命名方案重复所需次数。

你捕获的逻辑设计实际上从未被展平,源始终保持为多通道原理图。当你将其转移到PCB布局时,物理组件和网络会自动按所需次数步进。你可以完全访问用于在原理图和PCB之间工作的标准交叉探测和交叉选择工具。PCB编辑器中还有一个工具可以复制一个通道的放置和布线到所有其他通道,并且可以轻松移动和重新定位整个通道。

动态编译 Copy Link Copied

相关文章: 编译和验证设计

设计连接模型在每次用户操作后通过动态编译逐步更新。你不需要手动编译项目,因为这是自动完成的。对于设计项目,自动编译过程执行三个功能:

- 实例化设计层次结构。

- 建立所有设计图纸之间的网络连接。

- 构建设计的内部统一数据模型(UDM)。

这确保所做的任何设计更改都会立即反映在导航器和项目面板中。

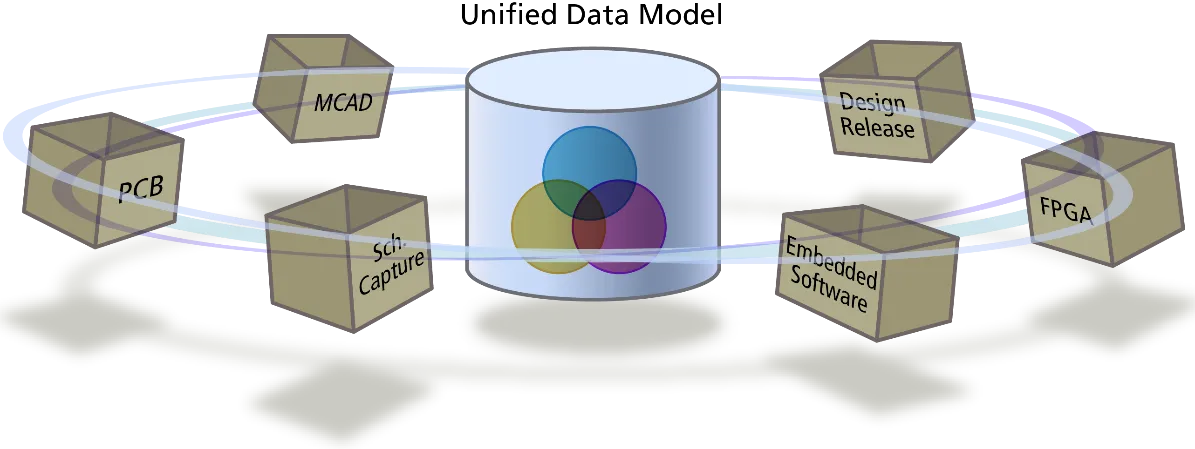

项目的编译模型被称为统一数据模型(UDM)。UDM包括设计中每个组件的详细描述,以及它们之间是如何连接的。

为了检查UDM和编译器设置之间的逻辑、电气和绘图错误,你必须验证项目。可以通过从主菜单选择项目 » 验证项目命令或右键单击项目面板中的项目条目,并从上下文菜单中选择验证项目命令来访问此命令。

编译器检测到的任何违规行为都将在消息面板中列为警告和/或错误。编译器在检查源文件中的违规行为时,使用在错误报告和连接矩阵选项卡上定义的选项(适用于项目类型)。

TRANSLATE:

统一数据模型

要理解多通道设计,有助于了解设计数据是如何管理的。软件的一个基本元素是统一数据模型(Unified Data Model,UDM)。当项目自动编译时,会创建一个单一的、连贯的模型,该模型位于设计过程的中心。然后可以使用软件内的各种编辑器和服务访问和操作模型中的数据。UDM的结构旨在容纳所有设计方面的所有信息,包括组件及其连接性,而不是为各种设计领域使用单独的数据存储。

统一数据模型使所有编辑器都能访问所有设计数据,并帮助提供像多通道设计这样的复杂功能。

UDM与分层设计系统结合使用,以实现多通道设计功能。"通道"是Sheet Symbol内的电路 - 在这个Sheet Symbol下面可以是单个图纸,或者可以是包含其他子图纸的项目结构的整个分支。您还可以在通道内创建通道,在两级多通道设计中,上层通道被称为银行,下层通道被称为通道。

因为这个完整的、准备好的PCB描述存在于内存中,所以只要有系统化的方式来处理重复对象,例如组件指定器和网络,就可以重复电路的一部分。系统化命名在项目选项对话框的多通道标签中定义,如下所述。

创建多通道设计

当电路的一部分被重复时,设计就是多通道的。这是在sheet symbol级别完成的,方法有:

- 放置多个都引用同一个子原理图的Sheet Symbols,或者

- 配置单个Sheet Symbol以重复所需次数的引用子原理图

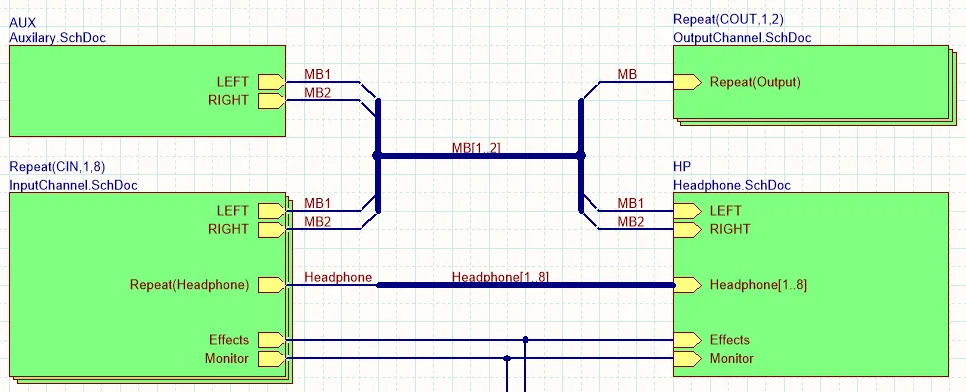

第一张图片 - 有四个Sheet Symbols,都引用同一个子图纸(PortIO.SchDoc)。第二张图片 - 通过使用Repeat关键字,InputChannel.SchDoc重复了八次,OutputChannel.SchDoc重复了两次。

上面的图片展示了创建多通道设计的两种方法。在第一张图片中,有四个表符号都引用了同一个子表(PortIO.SchDoc)。在第二张图片中,InputChannel.SchDoc重复了八次,OutputChannel.SchDoc重复了两次,这是通过表符号的设计器字段中的Repeat关键字实现的。

项目中重复的组件设计器和网络名称通过应用标准命名方案来解决。例如,一种命名方案是在重复的组件和网络标识符(网络标签和端口)中添加通道索引,如下图中的高亮部分所示。

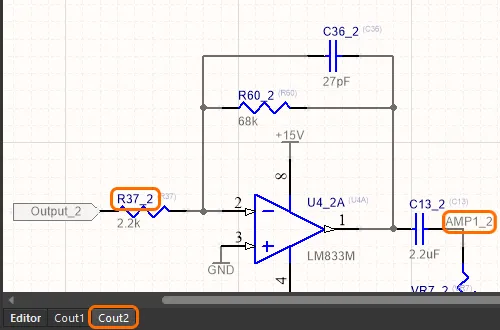

注意当项目打开时,原理图底部出现的标签页。 编辑器 标签页包含了您捕获的逻辑设计,其他编译后的标签页(COUT1 和 COUT2)也会出现,它们代表了将要转移到PCB编辑器的物理设计。每个物理通道都会有一个标签页。

编译后的项目,展示了逻辑视图的标签页,以及每个转移到PCB的物理通道的标签页。注意重复的设计器和网络标识符是如何管理的。

Repeat关键字

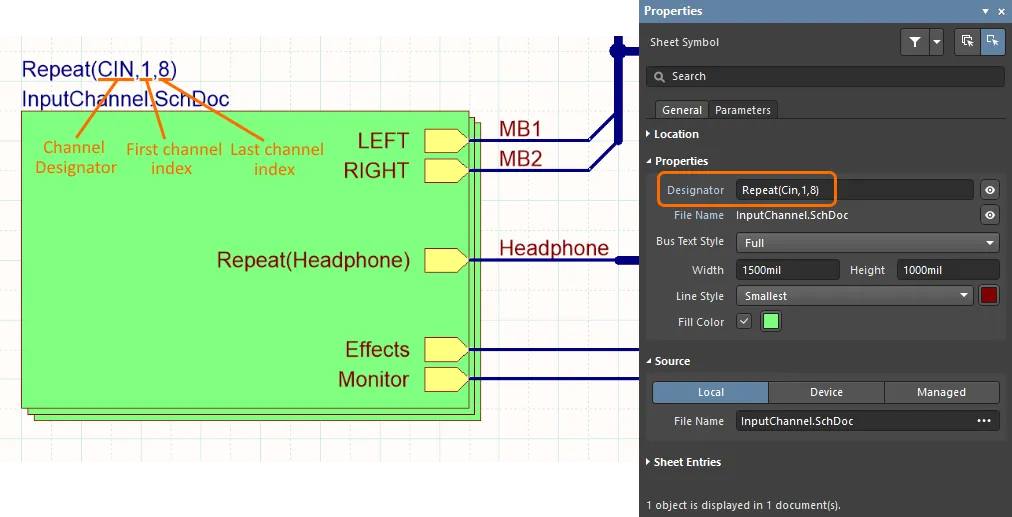

如前所述,通过放置多个引用相同子表的表符号,或者在表符号的设计器字段中包含Repeat关键字来重复一个通道。当使用Repeat关键字时,表符号被绘制为一组堆叠的表符号。

Repeat语句定义了通道设计器和通道数量。注意表符号是如何被绘制为一组堆叠的符号,以表示重复的通道。

每个通道由通道指示器标识,该指示器来自于设计符号的图纸符号。当通过放置多个图纸符号对设计进行通道化时,通道指示器是为每个图纸符号定义的设计符号值。如果设计是通过使用Repeat关键字进行通道化的,则通道指示器是由Repeat关键字定义的ChannelIdentifier+ChannelIndex。

当使用Repeat关键字时,设计符号字段的语法如下:

Repeat(<ChannelIdentifier>,<ChannelIndex_1>,<LastChannelIndex_n>)

多通道命名

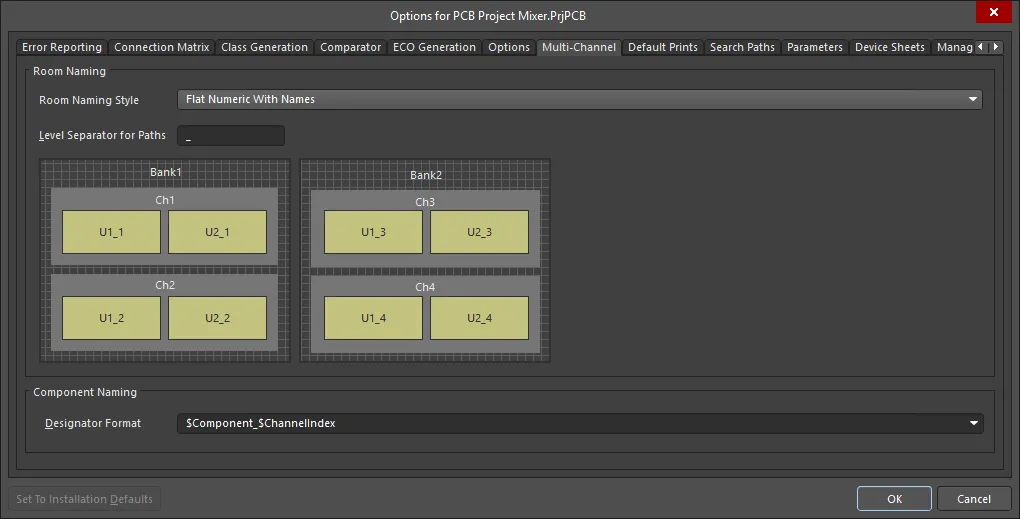

能够一次捕获然后重复 - 多通道设计 - 的概念是通过构建在软件的统一数据模型(UDM)上来实现的。重复的组件使用系统化的命名方案命名,该方案在项目选项对话框的多通道标签上进行配置,如下所示。

该对话框包括一个用于控制Room命名的上部分,以及一个用于控制这些Room内组件命名的下部分。在Room级别,有2种扁平命名风格和3种层次命名风格,通常情况下,如果设计中有通道内的通道,您只需要选择一个层次命名风格。否则,扁平Room命名风格更短,更容易理解。

对于组件命名,$Component$ChannelAlpha 或 $Component_$ChannelIndex 选项将提供最短且最容易解释的组件指示符。也可以使用可用关键字构建自己的指示符命名方案。

通过在项目选项对话框的多通道标签上选择一个系统化的命名方案,来管理重复的组件(和网络)。

Room的作用

Room是一个PCB设计对象,用于定义板上的一个区域,然后可以用两种方式使用: