ビアステッチングは、異なる層の大きな銅面積を結びつける技術であり、基板構造を通じて強力な垂直接続を作り出し、低インピーダンスと短いリターンループを維持するのに役立ちます。RF設計では、ビアステッチングはガードリングと組み合わせて使用され、ビアの壁を作り出し、電磁的に「静かな」PCBを作成するのに役立ちます。ビアステッチングは、そうでなければそのネットから隔離されてしまう銅の領域をそのネットに結びつけるためにも使用できます。

ビアシールディングは異なる機能を持ち、RF設計では、RF信号を運ぶルートでのクロストークと電磁干渉を減少させるのに役立ちます。ビアシールド、またはビアフェンス、ピケットフェンスとしても知られているものは、信号のルートパスに沿って一列または複数列のビアを配置することによって作成されます。Altium Designerでは、これをビアシールディングと呼びます。

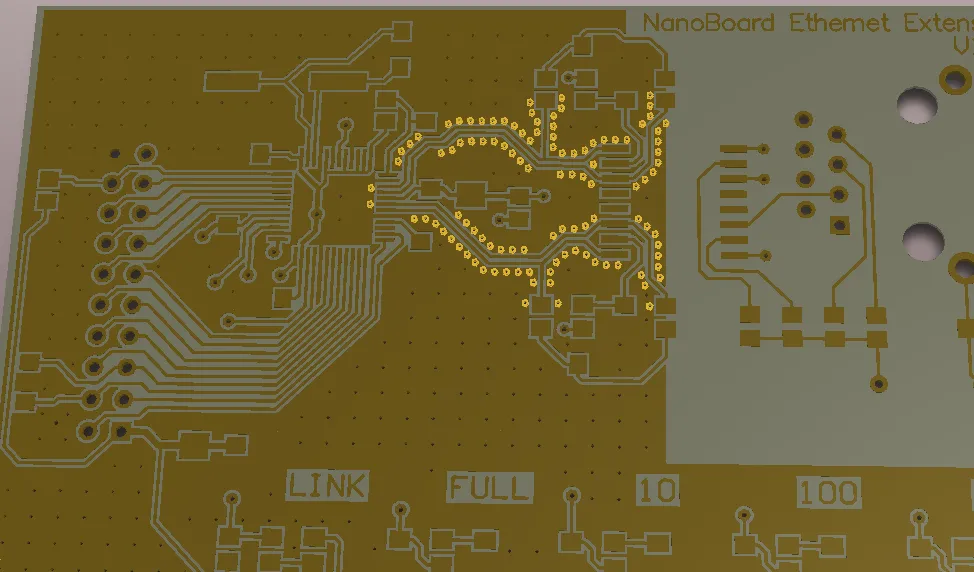

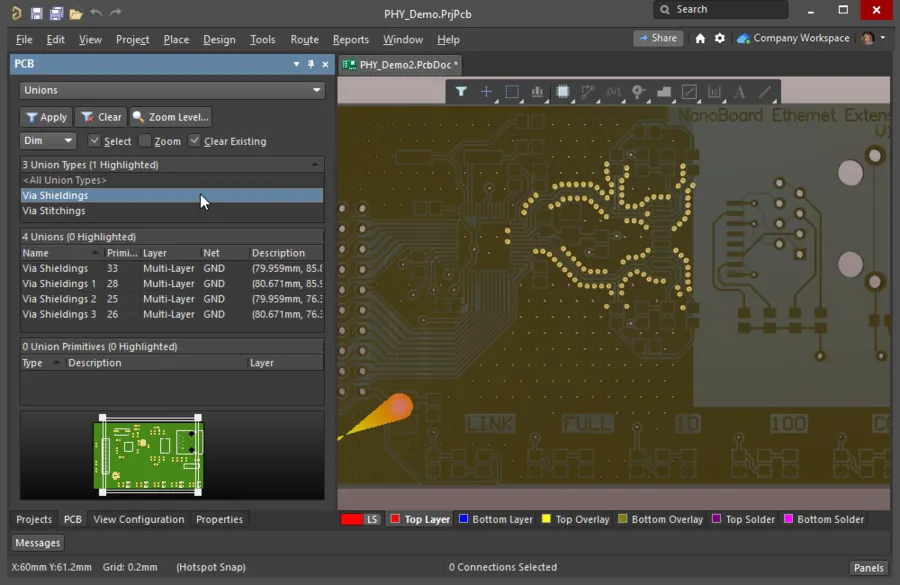

Altium Designerはビアステッチングとビアシールディングの両方をサポートしています。下の画像では、シールディングビアが強調表示されています。画像上でカーソルを動かすと、この基板に追加されたステッチングビアが強調表示されます。

異なる層の銅をステッチングし、ルートパスに隣接するシールディングビアの壁を追加するには、ビアステッチングおよびビアシールディングコマンドを使用します(ステッチングビアを強調表示するためにホバーします)。

異なる層の銅をステッチングし、ルートパスに隣接するシールディングビアの壁を追加するには、ビアステッチングおよびビアシールディングコマンドを使用します(ステッチングビアを強調表示するためにホバーします)。

まずステッチングビアを見て、次にシールディングビアを見ていきましょう。

ステッチングビアの追加

ビアステッチングはポストプロセスとして実行され、銅の空き領域をステッチングビアで埋めます。ビアステッチングが可能であるためには、異なる層にある指定されたネットに接続された銅の重なり合う領域が存在する必要があります。サポートされる銅の領域にはフィル、ポリゴン、パワープレーンが含まれます。

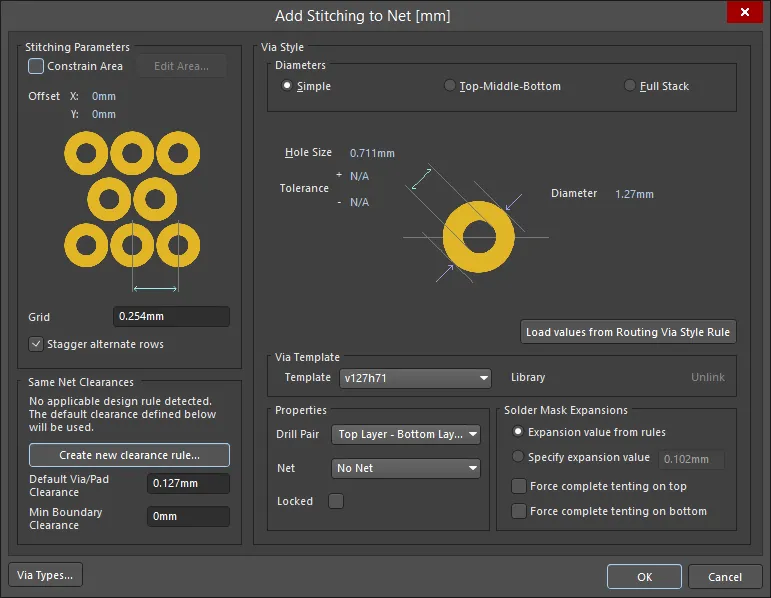

特定のネットにステッチングビアを追加するには、メニューからTools » Via Stitching/Shielding » Add Stitching to Netコマンドを選択します。Add Stitching to Netダイアログが開き、Stitching ParametersとVia Styleが指定されます。

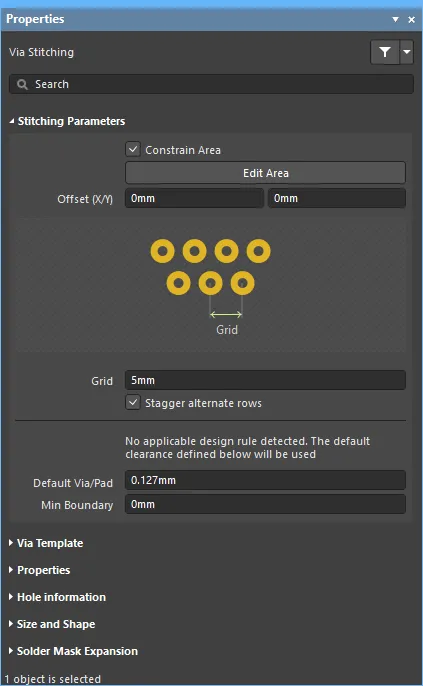

ネットにステッチングを追加ダイアログのオプションとコントロール

ステッチングパラメータ

ステッチングビアの配置パターンと他のネットおよび同じネットのオブジェクトからのクリアランスを制御します。

-

Constrain Area - 特定のエリアにビアステッチングを制約するために有効にします。オプションを選択した後、設計スペースに移動します。クロスヘアカーソルを使用して制約エリアを定義した後、ダイアログに戻るために右クリックします。

-

Edit Area - 制約エリアを編集するためにクリックします。

-

Offset - XおよびYのオフセット距離を入力します。

-

Grid - 隣接するステッチングビアの中心間の距離です。ステッチングビアは適用可能な設計ルールに違反しないように配置されます。違反を引き起こす可能性のあるビアサイトはスキップされます。

-

Stagger alternate rows - シールディングビアの交互の行は、Grid値の半分だけオフセットされます。

同じネットのクリアランス

同じネット上のビアとパッドへのステッチングビアのクリアランスを制御する方法は2つあります:適用可能なクリアランス設計ルールが使用されるか、またはここで指定されたDefault Via/Pad Clearanceが使用されます。ルールが存在する場合、これらの設定の厳しい方が使用されます。これらのオプションは次のように動作します:

-

Create new clearance rule - このボタンをクリックすると、ステッチングビア対他のビア/パッドの設計ルールが作成されます。このルール設定は、潜在的なステッチングサイトが有効であることを保証するために使用されます。クリックすると、PCB Rules and Constraints Editorダイアログが開き、その中でルールのConstraintsが設定されます。このルールは、ダイアログで選択されたネットを対象として名前付けられ、スコープされていることに注意してください。

-

Edit Clearance Rule - 適用可能な設計ルールが既に存在する場合、このボタンがCreate New Clearance Ruleボタンの代わりに表示されます。クリックしてConstraintsルール設定を変更します。

-

Default Via/Pad Clearance - スティッチングビアは、このクリアランスが存在する場合にのみ、スティッチング候補地に配置されます。潜在的なスティッチング部位はスティッチンググリッドによって決定されるため、この設定よりも離れている可能性があります。

-

Min Boundary Clearance - スティッチングビアは、ポリゴン/フィル/プレーン領域のエッジにこれだけのクリアランスが存在する場合にのみ、スティッチング候補地に配置されます。

ステッチビアから他のネット上のオブジェクトへのクリアランスは、適用可能なクリアランス設計ルールによって制御されます。スティッチングビアは、適用されるデザインルールに違反する場合、スティッチング候補地には配置されません。

ビアスタイル

ステッチングVia Styleは、手動で設定するか、Load values from Routing Via Style Ruleボタンをクリックして適用可能なルーティングビアスタイル設計ルールからインポートできます。このボタンをクリックすると、Preferredルール設定が読み込まれます。

Diameters

ビアテンプレート

プロパティ

-

Drill Pair - このビアが開始および終了するレイヤー。

-

Net - 現在ビアが割り当てられているネット。フィールドをクリックしてドロップダウンリストからネットを選択し、ネット割り当てを変更します。No Netを選択して、ビアがどのネットにも接続されていないことを指定します。プリミティブのネットプロパティは、PCBオブジェクトが合法的に配置されているかどうかを判断するために設計ルールチェッカーによって使用されます。

-

Locked - このオプションを有効にすると、ビアのグラフィカルな編集が防止されます。位置が重要なビアをロックします。ロックされたプリミティブを編集しようとすると、プリミティブがロックされていることと、アクションを続行するかどうかを尋ねるメッセージが表示されます。このオプションがチェックされていない場合、プリミティブは確認なしに自由に編集できます。

Start LayerとEnd Layerの設定は、ビアを以下のタイプのいずれかに定義します:

-

Multi-layer(Thru-Hole)- このタイプのビアはトップレイヤーからボトムレイヤーまで通過し、すべての内部信号レイヤーへの接続を可能にします。

-

Blind - このタイプのビアは基板の表面から内部の電気レイヤーに接続します。

-

Buried - このタイプのビアは一つの内部電気レイヤーから別の内部電気レイヤーに接続します。

はんだマスク拡張

-

Expansion value from rules - このパッドオブジェクトに既存のはんだマスク拡張ルールを適用するためにこのオプションを有効にします。はんだマスク拡張ルールを確認するために、Mask設計カテゴリをPCB Rules and Constraints Editorダイアログからチェックします。

-

Specify expansion value - このオプションを有効にして拡張値を編集し、はんだマスク拡張設計ルールをこのパッドに対して上書きします。

-

Force complete tenting on top - はんだマスク拡張設計ルールのはんだマスク設定を上書きし、このパッドの上層のはんだマスクに開口部がないようにします。

このオプションを無効にすると、このパッドははんだマスク拡張ルールまたは特定の拡張値の影響を受けます。

-

Force complete tenting on bottom - はんだマスク拡張設計ルールのはんだマスク設定を上書きし、このパッドの下層のはんだマスクに開口部がないようにします。このオプションを無効にすると、このパッドははんだマスク拡張ルールまたは特定の拡張値の影響を受けます。

追加のコントロール

ヒント

選択されたネットを使用して、ステッチングアルゴリズムはそのネットに接続されているすべてのフィル、ポリゴン、パワープレーンを識別し、指定されたビアとステッチングパターンを使用してボードを通じて接続しようとします。

ビアステッチングアルゴリズムは、ポリゴン、フィル、プレーンを以下の方法で扱います:

-

同じネット上のポリゴンとフィルは、異なるレイヤー上で重なっている場所でステッチングされます。そのエリア内で(別のレイヤー上に)他のネットのポリゴンやフィルが重なっている場合、その領域ではステッチングは適用されません。他のネットの重なっているプレーン領域は通過します。

-

ターゲットネットの重なっているプレーン領域は、他のネットに接続されたプレーン領域(別のレイヤー上)の存在に関係なく、常にステッチングされます。上記のルール1が同じ領域内でポリゴンやフィルが重なっている場合に適用されます。

To summarize these two rules - 別のレイヤー上の他ネットのプレーン層は常にステッチングビアによって貫通されますが、他ネットのポリゴンやフィルはそうではありません。設計に他ネットのポリゴンがステッチングビアが必要なエリア内に含まれている場合、一時的にそのポリゴンを棚上げし、ステッチングビアを定義した後、棚上げを解除してポリゴンを再配置してください。ポリゴンの棚上げと再配置についてもっと学ぶ。

ステッチングパラメータの設定

Add Stitching to Netダイアログ設定についての注意点:

-

スティッチに使用するNetを最初に選択します。これは、Load values from Routing Via Style Ruleボタンをクリックするなど、他のオプションの動作に影響します。Netドロップダウンは、ダイアログの下部の中央にあります。

-

Gridは、隣接するステッチビアの中心間の距離で、X方向とY方向に適用されます。ステッチビアは、潜在的なビアサイトが違反につながる場合、そのサイトはスキップされ、適用されるデザインルールに違反して配置されません。

-

Stagger alternate rowsオプションが有効になっている場合、ステッチングビアの交互の行はGrid値の半分だけオフセットされます。

-

Same Net Clearanceオプションは、同一ネット上のステッチングビアとビア、パッド間のクリアランスを制御します。同一ネットオブジェクト間のクリアランスを制御する方法は2つあり、適用可能なクリアランス設計ルールが使用されるか、ダイアログで指定されたDefault Via/Pad Clearanceが使用されます。適用可能なルールが存在する場合、これら2つの設定のうち厳しい方が使用されます。Create new clearance ruleボタンを使用して、Default Via/Pad Clearanceフィールドに入力した設定に基づいて、ルールダイアログに新しいクリアランス設計ルールを追加します。

-

ステッチングVia Styleは手動で設定することも、Templateドロップダウンから選択することも、Load values from Routing Via Style Ruleボタンをクリックして適用可能なルーティングビアスタイル設計ルールからインポートすることもできます。このボタンをクリックすると、Preferredルール設定が読み込まれます。

各ステッチングビアセットはユニオンに追加され、PCBパネルをUnionsモードに設定して、ビアステッチングセットに含まれるビアを検索して調べることができます。

ステッチングセットは、Tools » Via Stitching » Remove Via Stitching Groupコマンドを実行し、そのセット内の任意のビアをクリックすることで削除できます。

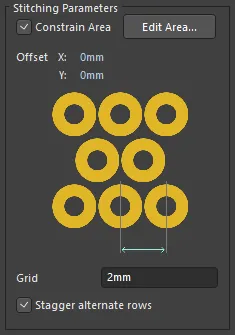

エリアへのビアステッチングの制約

ボード全体をカバーするだけでなく、ステッチングビアはユーザー定義エリアに制約することができます。ステッチングがユーザー定義エリア内にある場合、そのエリアのビアは必要に応じて対話的に移動およびサイズ変更することができます。

ユーザー定義エリアにステッチングビアを制限するには、エリア制約オプションを有効にします。

ユーザー定義エリアにステッチングビアを制限するには、エリア制約オプションを有効にします。

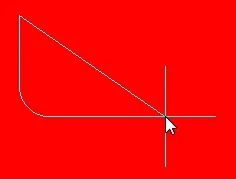

特定のエリアにビアステッチングを制約するには、上に示されているようにAdd Stitching to NeダイアログでConstrain Areaチェックボックスを有効にします。このオプションを有効にすると、ダイアログが閉じられ、カーソルが十字線に変わり、エリアを定義する準備ができます - ステータスバーに注意してください、Select the first point of the areaと表示されます。

ビアステッチングエリアを定義するプロセスは、ソリッドリージョンやポリゴンを定義するのと同じです。あなたは:

-

一連の頂点(コーナー)を定義するためにクリックし、

-

配置モードから抜けて自動的にエリアを閉じて完成させるために右クリックします。

配置中には、いくつかの異なるコーナーモードが利用可能です:

-

Shift+Spacebarを押してコーナーモードを切り替える(直角コーナーモードが最も適しているかもしれません)、

-

Spacebarを押してコーナーの方向を切り替える、

-

1のショートカットを押して、各クリックで1つまたは2つのエッジを配置するかを切り替える。

Shift+Spacebarを押してコーナーモードを切り替え、Spacebarを押してコーナーの方向を切り替え、1を押して各クリックで1エッジまたは2を配置するかを切り替えます。

Shift+Spacebarを押してコーナーモードを切り替え、Spacebarを押してコーナーの方向を切り替え、1を押して各クリックで1エッジまたは2を配置するかを切り替えます。

エリアが定義されると、Add Stitching to Netダイアログに戻るので、残りの設定を構成できます。これが完了したらOKをクリックします。Altium Designerはその後、エリアを分析し、潜在的なビアサイトを特定し、ステッチングビアを配置します。

ユーザー定義のビアステッチングエリアの修正

各ユニークなビアステッチングエリアのビアセットは、PCBエディタが単一のグループとして認識するオブジェクトのセットであるユニオンにクラスタリングされます。ユニオン全体を移動し、エリアもサイズ変更することができます。

エリアに制約されたビアステッチングを修正するには:

-

ステッチングビアの1つ以上を含むように左から右へ選択範囲をドラッグします。ステッチングエリアの境界が表示されます。

-

ステッチングユニオンを移動するには - エリア内にカーソルを位置させ、移動カーソル が表示されたらクリックして保持し、新しい位置にエリアを移動します。

が表示されたらクリックして保持し、新しい位置にエリアを移動します。

-

エッジを移動してステッチングユニオンのサイズを変更するには - エッジ上にカ頂点を移動してステッチングユニオンのサイズを変更するには、カーソルをエッジ上に置き、移動頂点カーソルが表示されたら クリックして保持し、頂点を新しい位置にスライドさせます。

クリックして保持し、頂点を新しい位置にスライドさせます。

-

マウスボタンを離すと、ステッチングを再生成しますか?というプロンプトが表示されますので、Yesをクリックして新しい位置/形状のビアステッチを更新します。または形状でビアステッチングを更新します。

ステッチングエリアを選択するために選択ウィンドウをドラッグし、正しいカーソルが得られるようにマウスを配置して移動またはサイズ変更します。

ネットにシールディングビアを追加する

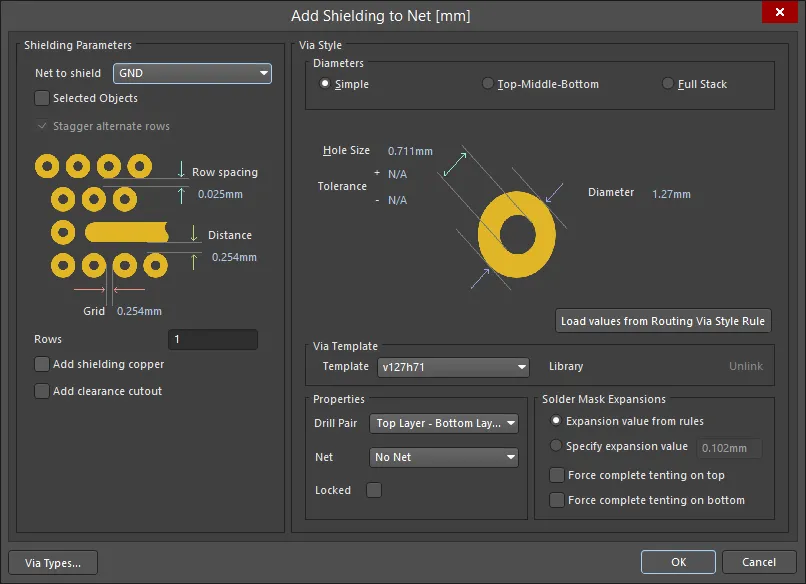

ルーティングされたネットの周りにビアシールドを配置するには、メニューからTools » Via Stitching/Shielding » Add Shielding to Netコマンドを選択します。Add Shielding to Netダイアログが表示され、必要に応じてShielding ParametersとVia Styleを設定できます。ビアは、適用可能な設計ルールに準拠するビアを配置できる場所であれば、選択したネットの両側に配置されます。

シールディングビアパラメータの設定

シールディングパラメータは、シールディングビアの配置パターンと他のネットおよび同じネットのオブジェクトからのクリアランスを制御します。

-

Net to shield - シールディングビアを配置するネット。

-

Selected Objects - Net to shieldフィールドで選択されたネットではなく、選択されたオブジェクトの周りにシールディングビアを配置します。また、複数の選択されたネットをシールドするためにも使用できます。

-

Stagger alternate rows - シールディングビアの交互の行は、Grid値の半分だけオフセットされます。

-

Row Spacing - Rowsの設定が1より大きい場合のシールディングビアの行間の間隔(エッジからエッジまでの分離)。

-

Distance - シールドされたネットのトラックセグメントのエッジからシールディングビアのエッジまでの分離。

-

Grid - 隣接するシールディングビアのエッジ間の距離。適用可能な設計ルールに違反する場合、シールディングビアは配置されません。潜在的なビアサイトが違反になる場合、そのサイトはスキップされます。

-

Rows - シールディングビアの行数。

-

Add shielding copper - シールディングビアが占める領域にポリゴンを配置し、Via Netフィールドで指定されたネットに接続します。ポリゴンは、適用可能なClearance constraintおよびPolygon Connect Style設計ルールに従って定義されます。

-

Add clearance cutout - シールドされたネットの周りにポリゴンカットアウトを含め、Distanceフィールドで指定された距離だけネットからセットバックします。適用可能なClearance constraint設計ルールとは異なるクリアランスが必要な場合に使用します。

ビアスタイル

シールディングのVia Styleは、希望のスタイルを手動で選択するか、Load values from Routing Via Style Ruleボタンをクリックすることで設定できます。このボタンをクリックすると、Preferredルール設定が読み込まれます。

直径

-

Simple - ビアスタイル(穴のサイズと直径)は全ての層で同じです。

-

Top-Middle-Bottom - トップレイヤー、ミドルレイヤー、ボトムレイヤーで異なる穴のサイズと直径を設定できます。

-

Hole size - Viaのホールサイズ値を指定します。

-

Tolerance Min/Max - ホールの許容差属性を設定することで、基板の適合と限界を決定するのに役立ちます。設計の最小 (-) および最大 (+) ホール許容差を指定します。

-

Top Layer - トップレイヤーのViaサイズを指定します。

-

Middle Layer - ミドルレイヤーのViaサイズを指定します。

-

Bottom Layer - ボトムレイヤーのViaサイズを指定します。

-

Full Stack - 各レイヤー(すべての信号層と平面を含む)で異なるホールサイズと直径を編集できます。

-

Hole size - Viaのホールサイズ値を指定します。

-

Tolerance Min/Max - ホールの許容差属性を設定することで、基板の適合と限界を決定するのに役立ちます。設計の最小 (-) および最大 (+) ホール許容差を指定します。

-

Edit Full Stack Via Sizes - Via Layer Editorダイアログを開くためにクリックし、各レイヤースタックのVia設定を指定できます。

Viaテンプレート

プロパティ

-

Drill Pair - このViaが開始および終了するレイヤー。

-

Net - 現在Viaが割り当てられているネット。フィールドをクリックしてドロップダウンリストからネットを選択し、ネット割り当てを変更します。No Netを選択して、Viaがどのネットにも接続されていないことを指定します。プリミティブのネットプロパティは、PCBオブジェクトが合法的に配置されているかどうかを判断するためにデザインルールチェッカーによって使用されます。

-

Locked - Viaがグラフィカルに編集されるのを防ぐためにこのオプションを有効にします。位置が重要なViaをロックします。ロックされたプリミティブを編集しようとすると、プリミティブがロックされていることが通知され、アクションを続行するかどうか尋ねられます。このオプションがチェックされていない場合、プリミティブは確認なしに自由に編集できます。

Start LayerおよびEnd Layerの設定は、Viaを以下のタイプのいずれかに定義します:

-

Multi-layer(Thru-Hole) - このタイプのViaはトップレイヤーからボトムレイヤーまで通過し、すべての内部信号層への接続を可能にします。

-

Blind - このタイプのViaは基板の表面から内部の電気層に接続します。

-

Buried - このタイプのViaは一つの内部電気層から別の内部電気層に接続します。

はんだマスク拡張

-

Expansion value from rules - このパッドオブジェクトに既存のはんだマスク拡張ルールを適用するために有効にします。はんだマスク拡張ルールを確認するために、PCB Rules and Constraints EditorダイアログのMaskデザインカテゴリをチェックします。

-

Specify expansion value - 拡張値を編集し、はんだマスク拡張デザインルールがこのパッドに対して上書きされるように有効にします。

-

Force complete tenting on top - はんだマスク拡張デザインルールの任意のはんだマスク設定を上書きし、このパッドのトップレイヤーのはんだマスクに開口部がないようにします。このオプションを無効にすると、このパッドははんだマスク拡張ルールまたは特定の拡張値の影響を受けます。

-

Force complete tenting on bottom - はんだマスク拡張デザインルールの任意のはんだマスク設定を上書きし、このパッドのボトムレイヤーのはんだマスクに開口部がないようにします。

このオプションを無効にすると、このパッドははんだマスク拡張ルールまたは特定の拡張値の影響を受けます。

追加のコントロール

ヒント

パラメータによるシールドの設定

Add Shielding to Net ダイアログとシールドビアの使用についての注意:

-

シールドするNetを最初に選択してください。これは、Load values from Routing Via Style Ruleボタンをクリックするなど、他のオプションの動作に影響します。

-

部分的なネットシールドや複数ネットのシールドには、Selected Objectsオプションを使用します:

-

差動ペアは、複数ネットの選択したオブジェクト技術を使用するか、Net to Shieldドロップダウンで差動ペアネットのいずれかを選択することでシールドできることに注意してください。

-

Add shielding copperオプションを使用して、シールドビアを囲むポリゴンを追加し、クリアランスカットアウトを追加オプションを含めて、ビアだけを囲むようにポリゴンをクリップバックします。ステッチングと一緒にシールド銅を含むトピックを読んで、これらのオプションについて詳しく学びましょう。

-

シールドVia Styleは手動で設定することも、Templateドロップダウンから選択することも、適用されるルーティングビアスタイル設計ルールからLoad values from Routing Via Style Ruleボタンをクリックしてインポートすることもできます。このボタンをクリックすると、Preferredルール設定が読み込まれます。

-

シールドビアのサイズと配置は正確な科学ではありませんが、経験的なテストに基づいて確立されたガイドラインがあります。

-

フォーラムの議論で指摘されているように(5)、オンボードアンテナを搭載したPCBでは、「ビア間の距離は、最大で共振波長の1/4であるべきです。」

-

フォーラムの議論では、技術ノート(6)も参照されており、「一般的な経験則として、ステッチビアはλ/10より遠くに配置せず、できればλ/20ごとに配置するべきです。」

M K Armstrongは彼の論文最低コストでEMCコンプライアンスを達成するためのPCB設計技術 パート1で(7)次のように推奨しています:

「ステッチングはλ/20を超えないようにし、スタブの長さもこれを超えないようにします。これは、実際にはマルチレイヤーデザインでグラウンドフィルをグラウンドプレーンにステッチングするための非常に良いルールです。λは、設計の最も重要な高周波数の波長であり、わからない場合は1GHzの周波数を仮定します。ここで:

f = C / λ

注: C(光速)は、FR4ダイエレクトリックPCBを通るEM放射の自由空間速度の約60%になります。"

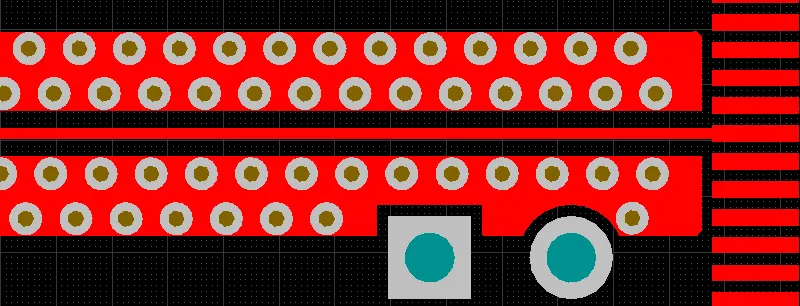

ステッチングと一緒にシールド銅を含む

ルーティングの両側にシールドビアを追加するだけでなく、下の画像に示すようにシールド銅も含めることができます。これを行うには、Add shielding copperオプションを有効にします。この銅はポリゴンとして作成されるため、適用されるクリアランスおよびポリゴン接続スタイル設計ルールに従います。

Add shielding copperオプションは、シールドビアを囲むポリゴンを追加します。シールドされたネットから離れたポリゴンエッジは、ビアのエッジに接触します。シールドされたネットに隣接するポリゴン エッジは、適用可能なクリアランスデザイン ルールによってネットから後退します。Add clearance cutoutオプションも有効になっている場合、ポリゴンはAdd Shielding to NetダイアログのDistance設定によってシールドされたネットから後退します。下の画像にカーソルを合わせると、違いが表示されます。

クリアランスカットアウトオプションが有効になっているネットの周りのシールドビア、画像上にカーソルを移動してクリアランスカットアウトオプションを無効にします。

クリアランスカットアウトオプションが有効になっているネットの周りのシールドビア、画像上にカーソルを移動してクリアランスカットアウトオプションを無効にします。

シールドビアからシールド銅線(ポリゴン)への接続スタイルは、シールドビアとポリゴンを対象とするポリゴン接続スタイルデザインルールを含めることで制御できます。InViaShieldingクエリキーワードを使用して、このデザイン ルールのスコープを設定し、それらのビアとそのポリゴンを具体的に対象とするようにします。

スティッチングまたはシールドアレイの一部であるビアの識別

ステッチングまたはシールディング配列にある各ビアは、ネット名に文字列を追加することで識別されます。例えば [VS1]のように、下の画像に示されているように、ここで:

-

VS - Via Stitchingで、数値はこのビアが同じ識別子を持つ他のビアと同じビアステッチング連合に属していることを示します。

-

VSH - Via SHieldingで、数値はこのビアが同じ識別子を持つ他のビアと同じビアシールディング連合に属していることを示します。

![配列に属するビアには、[Via Shieldingグループ1]の[VS1]や[Via SHieldingグループ4]の[VSH4]などの追加の文字列がネット名に付加されます。 配列に属するビアには、[Via Shieldingグループ1]の[VS1]や[Via SHieldingグループ4]の[VSH4]などの追加の文字列がネット名に付加されます。](https://files.doc.altium.com/sites/default/files/wiki_attachments/323938/ViaIdentifiers.webp?VersionId=GndmfOp3WOGKo4VTmUV2JiuTGetQPK49) 配列に属するビアには、[Via Shieldingグループ1]の[VS1]や[Via SHieldingグループ4]の[VSH4]などの追加の文字列がネット名に付加されます。

配列に属するビアには、[Via Shieldingグループ1]の[VS1]や[Via SHieldingグループ4]の[VSH4]などの追加の文字列がネット名に付加されます。

ステッチングまたはシールディングビアの選択または編集

ステッチング/シールディングビアの配列を扱うプロセスを簡素化するために、両方の種類は自動的に連合にクラスタリングされます。

PCBパネルを使用した選択

配列を選択するには、PCBパネルをUnionsモードに切り替え、必要なVia StitchingまたはVia Shielding連合を選択します。パネルでSelectチェックボックスが有効になっている場合(下の画像に示されているように)、その配列の一部であるすべてのビアが選択されます。または、配列内の任意のビアをダブルクリックしてProperties パネルを開き、配列を編集します。

PCBパネルをUnionsモードで使用して、ステッチングまたはシールディング配列内のすべてのビアを選択します。この画像では、4つのビアシールディング連合がすべて選択されています。

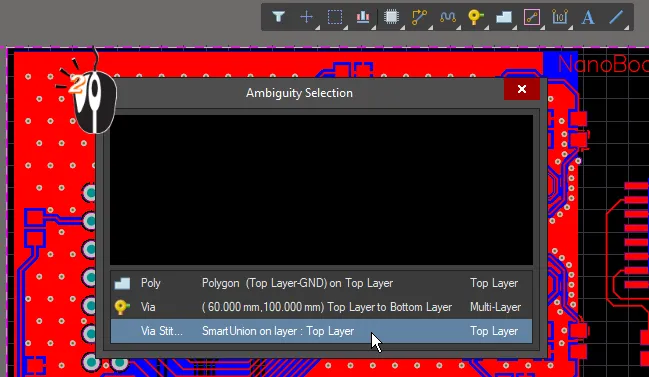

インタラクティブな選択

選択動作:

-

個々のステッチング/シールディングビアを選択して削除することができます。

-

Popup Selection Dialogオプションが有効になっている場合(PCB Editor - GeneralページのPreferencesダイアログ)、連合に属する個々のビアをクリックすると、上の画像に示されているように、連合を含むリストが表示されます。連合が選択されると、そのビアの連合をワークスペースで削除することができます。

-

Popup Selectionダイアログが有効になっていない場合、連合に属する個々のビアをクリックすると、次のように動作します:

-

最初のクリックで個々のビアが選択されます。

-

2回目以降のクリックで、重なっているオブジェクトの選択順序に従って次のオブジェクトが選択されます。例えば、カーソルの下にある場合はコンポーネント、ポリゴン、ビア連合などです。

-

また、最初のクリックで個々のビアが選択された後、Shift+Tabショートカットを押してSelect Overlappingコマンドを呼び出します。重なっているオブジェクトを順に選択するために、Shift+Tabを続けて押します。

-

特定の領域に制約されたステッチング連合は、連合内の任意のビアの周りに選択ウィンドウをドラッグする(左から右へドラッグ)ことで選択できます。これは、このページのModifying a User-Defined Via Stitching Areaセクションのアニメーションで示されています。

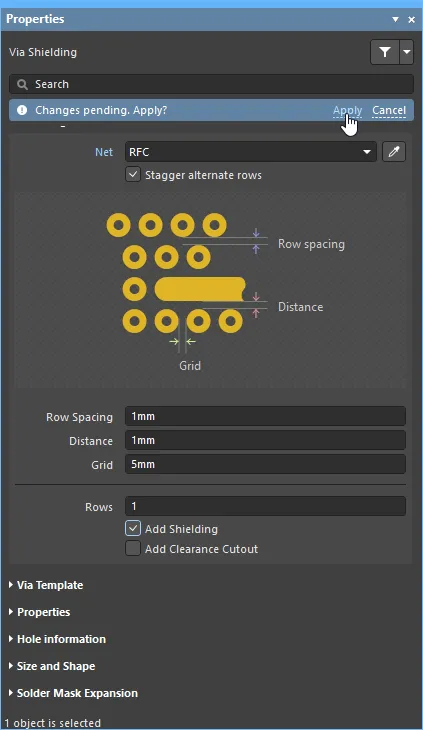

ステッチングまたはシールディングビアの編集

ステッチングまたはシールディングビアセットのプロパティは、選択された後、Via StitchingまたはVia ShieldingモードのPropertiesパネルで編集できます。セット内の任意のビアをダブルクリックしてパネルを開きます。

ビアシールディングの編集例。

ビアシールディングの編集例。

パネルでいずれかのプロパティが編集されると、Changes pendingメッセージとボタンがパネルの上部に表示されます - Applyリンクをクリックして編集アクションを完了します。

以下の折りたたみ可能なセクションには、利用可能なVia Shieldingオプションとコントロールに関する情報が含まれています:

シールドパラメータ

-

Net – シールディングビアによってシールドされるネット。

-

Row Spacing – Rows設定が1より大きい場合のシールドビアの行間の間隔(エッジからエッジへの分離)。

-

Distance - シールドされたネットトラックセグメントの端から、シールドビアの端までの距離。

-

Grid - 隣接するシールドビアの端間の距離。シールドビアは適用可能な設計ルールに違反しないように配置されます。潜在的なビアの位置が違反になる場合、その位置はスキップされます。

-

Rows - シールドビアの行数。

-

Add Shielding - Via Netフィールドで指定されたネットに接続された、シールドビアが占める領域にポリゴンを配置します。ポリゴンは適用可能なClearance constraintおよびPolygon Connect Style設計ルールに従って定義されます。

-

Add Clearance Cutout - シールドされたネットの周りにポリゴンカットアウトを含め、Distanceフィールドで指定された距離だけネットから後退させます。適用可能なClearance constraint設計ルールとは異なるクリアランスが必要な場合に使用します。

ビアテンプレート

プロパティ

ホール情報

サイズおよび形状

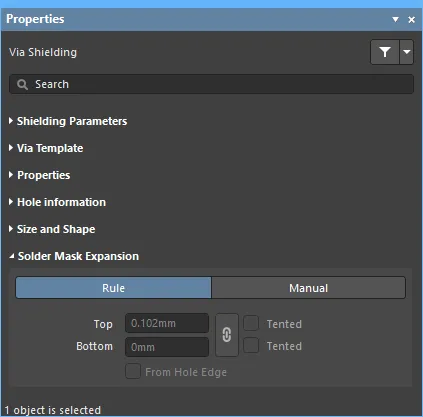

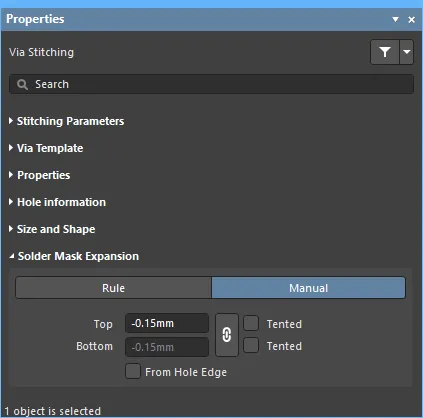

はんだマスク拡張

-

Rule - 既存のはんだマスク拡張ルールがシールドビアに適用されるようにこのオプションを有効にします。Mask設計カテゴリをPCB Rules and Constraints Editorダイアログからチェックします。

-

Manual - これらのシールドビアのマスク拡張値(以下)を編集するためにこのオプションを有効にします。

-

Top - トップレイヤーに必要なマスク拡張を入力します。

-

Bottom - ボトムレイヤーに必要なマスク拡張を入力します。

-

Top Tented - このチェックボックスが有効になっている場合、これらのシールドビアのためにトップレイヤーでマスクが閉じます。

-

Bottom Tented - このチェックボックスが有効になっている場合、ボトムレイヤーでマスクが閉じます。

-

Linked - リンク済みオプションが有効になっている場合、トップとボトムのレイヤーで同じ拡張値が使用されます。

-

From Hole Edge - ビアドーナツの端ではなく、ドリル穴の端からマスク拡張を計算するためにこのオプションを有効にします。

以下の折りたたみセクションには、利用可能なVia Stitchingオプションとコントロールに関する情報が含まれています:

ステッチングパラメータ

-

Constrain Area - 特定のエリアにビアステッチングを制約するために有効にします。オプションを選択した後、設計スペースに移動します。クロスヘアカーソルを使用して制約エリアを定義した後、ダイアログに戻るために右クリックします。

-

Edit Area - クリックして制約領域を編集します。

-

Offset (X/Y) - XおよびYのオフセット距離を入力します。ステッチングパターンは、指定されたXおよびYの量のオフセットで、制約エリア内に配置されます。

-

Grid - 隣接するステッチングビアの中心間の距離です。ステッチングビアは、適用可能な設計ルールに違反しないように配置されます。潜在的なビアの位置が違反になる場合、その位置はスキップされます。

-

Default Via/Pad - ステッチングビアは、この程度のクリアランスがある場合にのみ、潜在的なステッチングサイトに配置されます。ステッチングサイトはステッチンググリッドによって決定されるため、この設定よりも離れている可能性が高いです。

-

Min Boundary - ステッチングビアは、この程度のクリアランスがポリゴン/フィル/プレーン領域の端まで存在する場合にのみ、潜在的なステッチングサイトに配置されます。

ビアテンプレート

プロパティ

ホール情報

サイズと形状

はんだマスク拡張

-

Rule - このオプションを有効にして、既存のはんだマスク拡張ルールをステッチングビアに適用させます。Mask設計カテゴリーをPCB Rules and Constraints Editorダイアログからチェックします。

-

Manual - このオプションを有効にして、これらのステッチングビアのマスク拡張値(以下)を編集します。

-

Top - トップレイヤーに必要なマスク拡張を入力します。

-

Bottom - ボトムレイヤーに必要なマスク拡張を入力します。

-

Top Tented - このチェックボックスが有効な場合、これらのステッチングビアのためにトップレイヤー上のマスクが閉じます。

-

Bottom Tented - このチェックボックスが有効な場合、ボトムレイヤー上のマスクが閉じます。

-

Linked - リンクオプションが有効な場合、トップとボトムのレイヤーで同じ拡張値が使用されます。

-

From Hole Edge - このオプションを有効にして、ビアドーナツの端ではなく、ドリル穴の端から拡張を計算します。

ステッチング/シールディングユニオンを編集した後のポリゴンの更新

ステッチングが完了したら、適用可能なポリゴン接続スタイル設計ルールがリリーフ接続スタイルを指定している場合、ポリゴンを再配置する必要があります。これは、Tools » Polygon Poursサブメニューのコマンドを使用して行うことができます。

さらに読む

-

PCB設計のすべての側面については、Printed Circuit Design and Fab MagazineのWebサイトを参照してください。このサイトは、「ビアフェンス」の役割(検索結果の品質を向上させるために引用符を含める)などの技術的なトピックに関する優れたリソースです。

-

ウィキペディアの記事, ビアフェンス

-

多層プリント基板上のビア結合に関する検討

-

PCB構造内でのEM波の伝播の基本原理を紹介する論文 - 回路基板設計のベストプラクティス

-

質問チップアンテナのノイズ削減のためのビアフェンス?がされたディスカッションフォーラム

-

最低コストでEMCコンプライアンスと信号整合性を実現するためのPCB設計とレイアウト技術:M K Armstrong. EMC Standards, 1999年8月。