PCBエディタは、設計の整合性を確保するためにチェックできる多くの種類の設計制約を定義できるルール駆動型の設計環境です。オンラインDRC機能は、作業中に有効なルールを監視し、検出された設計違反を即座に強調表示します。また、バッチDRCを実行して設計がルールに準拠しているかをテストし、有効なルールと検出された違反の詳細を記載したレポートを生成することもできます。

チュートリアルの前半で、電気的クリアランス、配線幅、配線ビアスタイルを含むいくつかの設計制約を調査し、設定しました。これらに加えて、新しいボードが作成されると自動的に定義される他の多くの設計ルールがあります。

設計ルールチェック(DRC)の設定と実行

メインページ: DRCの設定と実行

設計ルールチェック(DRC)を実行することで、違反がチェックされます。オンラインおよびバッチDRCは、Design Rule CheckerダイアログからTools » Design Rule Checkコマンドを選択してアクセスし、設定されます。このダイアログでは、一般的なレポーティングオプション(Report Options – )と、特定のルールタイプのテストを設定する機能(Rules to Check – )が提供されます。

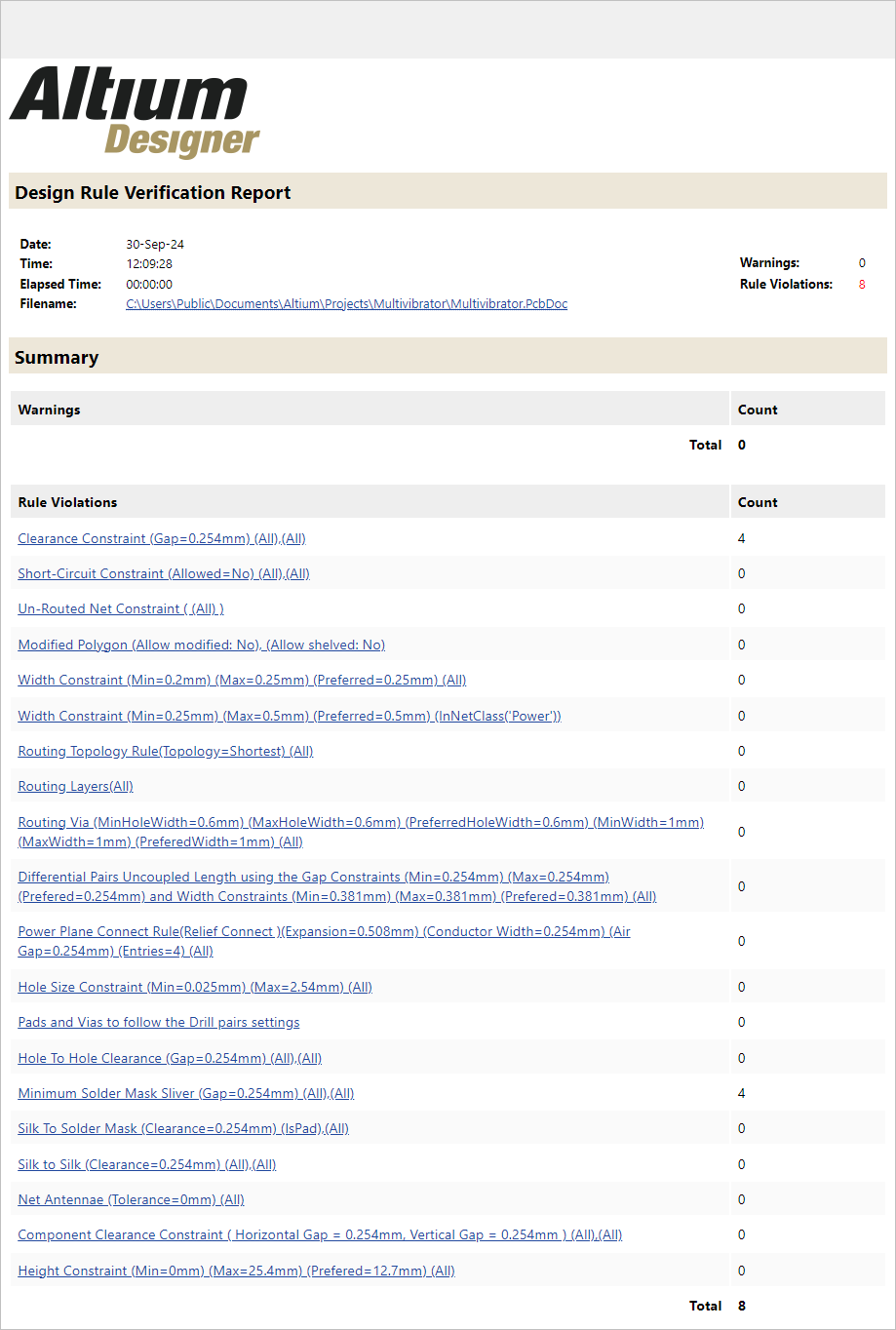

ダイアログの下部にある  ボタンをクリックすると、DRCが実行され、その後Messagesパネルが開き、検出されたすべての違反がリストされます。ダイアログでCreate Report Fileオプションが有効になっている場合、Design Rule Verification Reportが別のドキュメントタブで開きます。このレポートには、チェックのために有効にされたルール、検出された違反の数、および各違反の具体的な詳細が記載されています。

ボタンをクリックすると、DRCが実行され、その後Messagesパネルが開き、検出されたすべての違反がリストされます。ダイアログでCreate Report Fileオプションが有効になっている場合、Design Rule Verification Reportが別のドキュメントタブで開きます。このレポートには、チェックのために有効にされたルール、検出された違反の数、および各違反の具体的な詳細が記載されています。

-

メインメニューからTools » Design Rule Checkコマンドを選択して、Design Rule Checkerダイアログを開きます。

-

ダイアログのReport Options ページで、Create Report Fileオプションが有効になっていることを確認します。

-

ダイアログのRules To Check ページで、グリッドエリアを右クリックし、Batch DRC - Used Onエントリを選択します。

-

テストポイントルールのバッチDRCを無効にします。これを行うには、ツリーでTestpointセクションを選択し、このカテゴリの4つのルールタイプのBatchチェックボックスを無効にします。

-

ダイアログの下部にある ボタンをクリックしてDRCを実行します。 Design Rule Checkerダイアログが閉じ、レポートが開きます。少なくとも以下が含まれます:

ボタンをクリックしてDRCを実行します。 Design Rule Checkerダイアログが閉じ、レポートが開きます。少なくとも以下が含まれます:

レポートの上部には、チェックのために有効にされたルールと検出された違反の数が詳細に記載されています。違反を調査するには、ルールをクリックします。

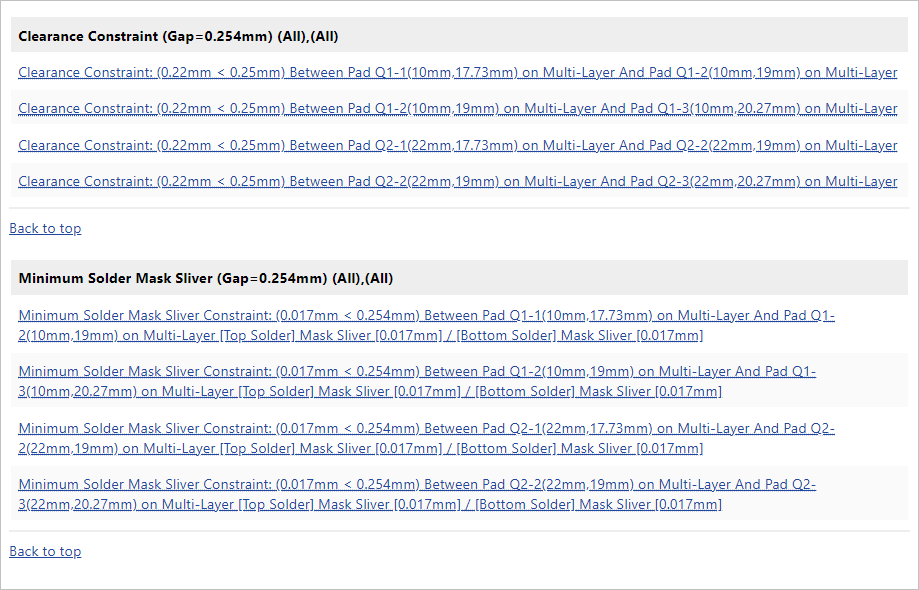

レポートの下部には、違反している各ルールが表示され、その後に違反オブジェクトのリストが続きます。違反エントリをクリックすると、そのオブジェクトがPCB上で表示されます。

検出された違反も、開かれるMessagesパネルにリストされます。

違反の特定と解決

メインページ: 設計違反の問い合わせと解決

設計者として、PCB内の違反を特定し、その状態と実際にどの程度失敗しているかを確立し、違反を解決する最も適切な方法を考え出す必要があります。

違反の特定と解決に関する注意事項

-

Altium Designerには、設計ルール違反を表示する2つの技術があります:

クリアランス違反の例を以下に示します。上記の技術は両方とも違反を示すために使用されます。違反しているパッドはパターンを使用して強調表示され、また、違反は白い矢印と<0.25mmテキストによって示され、このギャップが制約によって許可される最小の0.25 mmよりも小さいことを示しています。

-

違反を特定するには、報告書ファイルの下部にある具体的な違反を詳細に説明したリンクをクリックするか、Messagesパネルの項目をダブルクリックしてください。

-

報告書とMessagesパネルの違反エントリーには、違反がどの程度失敗したかについての詳細も含まれています。実際の値は、指定された制約値(例えば、0.017mm < 0.254mm)と共に詳細に記載されています。

クリアランス違反の解決

チュートリアルデザインでは、トランジスタフットプリントのパッド間のクリアランス制約に対する4つの違反があります。これらの違反を解決する方法は2つあります:

0.25 mmのクリアランスはかなり余裕があり、実際のクリアランスはこの値(0.22 mm)にかなり近いため、この状況では、ルールを設定して小さいクリアランスを許可することが良い選択です。この解決策は、スルーホールパッドを持つ唯一の他のコンポーネントが1 mm間隔のパッドを持つコネクタであるため、この状況で受け入れられます。この場合でなければ、最良の解決策は、トランジスタパッドだけを対象にした2番目のクリアランス制約を追加することです。これは、はんだマスク拡張ルールで行ったようにです。

制約マネージャーまたはPCB Rules and Constraints Editorーダイアログを持っていますか?

チュートリアルデザインに対して制約マネージャーまたは

PCB Rules and Constraints Editorダイアログが利用可能かどうかに応じて(プロジェクトのPCBドキュメントが開いているときにPCBエディターの

Designメインメニューを開き、

Constraint Managerまたは

Rulesコマンドの有無を素早く確認できます)、以下の折りたたみセクションのいずれかで説明されている対応するアプローチを使用してください。

クリアランス違反の解決(制約マネージャー)

-

設計スペースの上部にあるPCBドキュメントタブをクリックして、それをアクティブドキュメントにします。

-

メインメニューからDesign » Constraint Managerコマンドを選択して、制約マネージャーを開きます。

-

Clearancesビューの制約マネージャーで、クリアランスマトリックスのAll Nets / All Netsセル内をクリックします。

-

グリッドの下部にあるTH Pad – to – TH Padの値を0.22mmに変更します。これを行うには、セルをクリックし、0.22と入力してEnterを押します。

-

制約マネージャーで変更を保存します(File » Save to PCB)。

クリアランス違反の解決(PCB Rules and Constraints Editorダイアログ)

-

設計スペースの上部にあるPCBドキュメントタブをクリックして、それをアクティブドキュメントにします。

-

PCB Rules and Constraints Editorダイアログを開く(Design » Rules)。

-

ダイアログの左側にあるElectricalカテゴリの既存のクリアランスルールを見つけて選択します。

-

グリッド領域のルール制約で、TH Pad – to – TH Padの値を0.22 mmに変更します。これを行うには、セルをクリックし、0.22と入力してEnterを押します。

-

変更を受け入れてPCB Rules and Constraints Editor を開いたままにするには、Applyをクリックしてください。

最小はんだマスクスリバー違反の解決

はんだマスクは、銅にはんだ付けされる部品やワイヤーのための開口部が作られる、基板の外表面に適用される薄いラッカー様の層です。これらの開口部は、PCBエディタのはんだマスク層にオブジェクトとして表示されます(はんだマスク層はネガティブで定義されていることに注意してください - 見えるオブジェクトは実際のはんだマスクで穴になります)。

製造中、はんだマスクは異なる技術を使用して適用されます。最も低コストのアプローチは、マスクを通して基板表面にシルクスクリーンで印刷することです。レイヤーのアライメントの問題を許容するために、マスクの開口部は通常、パッドよりも大きく、デフォルトの設計ルールで使用される4ミル(約0.1 mm)の拡張値に反映されています。

はんだマスクを適用する他の技術もあり、これらはより高品質のレイヤー登録とより正確な形状定義を提供します。これらの技術を使用する場合、はんだマスクの拡張は小さくなるか、またはゼロになることがあります。マスク開口部を減らすことで、はんだマスクスリバーやシルクからはんだマスクまでのクリアランス違反の可能性が減少します。

はんだマスクスリバー違反。紫色は各パッド周りのはんだマスクの拡張を表しています。

最小はんだマスクスリバー違反の詳細を見るには、はんだマスクの表示を有効にする必要があります。View Configurationパネルを使用してレイヤーの可視性を設定してください。

これらのはんだマスクの問題のような違反は、完成した基板を作成するために使用される製造技術を考慮せずには解決できません。

例えば、これが高価値製品のための複雑な多層基板である場合、小さなまたはゼロのはんだマスク拡張を可能にする高品質のはんだマスク技術が使用される可能性があります。しかし、このチュートリアルの基板のような単純な両面基板は、低コストの製品として製造される可能性が高く、低コストのはんだマスク技術を使用する必要があります。これは、基板全体のはんだマスク拡張を減らすことではんだマスクスリバー違反を解決するのが適切な解決策ではないことを意味します。

PCB設計の多くの側面と同様に、解決策は、影響を最小限に抑えるために焦点を絞った方法で思慮深いトレードオフを行うことにあります。

この違反を解決するには、次のことができます:

これは、使用されるコンポーネントと製造および組み立て技術に関するあなたの知識を踏まえた設計上の決定です。マスクを開けてトランジスタパッド間のマスクのスリバーを完全に取り除くことは、それらのパッド間にはんだブリッジができる可能性が高くなることを意味しますが、マスク開口部を減らすと、スリバーが残る可能性があり、また、マスクとパッドの登録問題の可能性も導入します。

このチュートリアルでは、2番目と3番目のオプションの組み合わせを行い、この基板で使用されている設定に適した最小スリバー幅を減らし、また、トランジスタパッドのマスク拡張を減らしますが、トランジスタパッドにのみです。

制約マネージャーまたはPCBルールと制約エディタダイアログを持っていますか?

チュートリアルデザインにConstraint ManagerまたはPCB Rules and Constraints Editorダイアログが利用可能かどうかに応じて(プロジェクトのPCBドキュメントが開いているときにPCBエディタからDesignメインメニューを開いてConstraint ManagerまたはRulesコマンドを確認することで素早くチェ

今、すべての違反が解決されたことを確認するためにDRCを再実行してください。

出力を生成する前に、必ずクリーンな設計ルール検証レポートを確認してください。

-

Design Rule Checkerダイアログ(Tools » Design Rule Check)を開き、Create Report FileオプションがReport Optionsページで有効になっていることを確認します。

-

ボタンをクリックします。

ボタンをクリックします。

-

新しいレポートが生成され、別のドキュメントタブで開かれます。ルール違反が含まれていないことを確認してください。

違反がある場合は、それらを解決してからレポートを再生成してください。

-

生成されたDRCレポートをプロジェクトから削除します。これは、設計リリースプロセス中に生成されます。これを行うには、Generated\Documentsエントリをプロジェクトパネルで見つけ、それを右クリックしてRemove from Projectコマンドを選択します。Remove from projectダイアログが開いたら、Delete fileオプションを選択します。

-

現在開いているすべてのドキュメントを閉じます。これを行うには、設計スペースの上部にあるドキュメントタブを右クリックし、コンテキストメニューからClose All Documentsコマンドを選択します。

-

プロジェクトをワークスペースに保存します。これを行うには、プロジェクト パネルのプロジェクトエントリの隣にあるSave to Serverコントロールをクリックし、開いたSave to ServerダイアログのCommentフィールドに意味のあるコメントを入力します(例:PCB design complete)、そして OK ボタンをクリックします。

よくやりました!あなたはPCBが制約に準拠していることを確認し、PCB図面を作成する準備が整いました。