設計の信号整合性分析を成功させ、正確な結果を得るためには、分析を実行する前に以下の作業を行う必要があります。

-

各ネットはネットとインピーダンスデータを提供するためにスクリーニングできますが、すべてのネットが信号完全性特性(電圧とタイミング)について分析されるわけではありません。すべての特性に成功裏にスクリーニングするためには、ネットには少なくとも1つの出力ピンを持つICが含まれている必要があり、他のコンポーネントは含まれていません。例えば、抵抗器、コンデンサ、インダクタは、駆動源を提供する出力ピンがないため、自身ではシミュレーション結果を提供しません。双方向ネットがスクリーニングされる場合、両方向がシミュレートされ、最悪の結果が表示されることに注意してください。

-

各コンポーネントに関連付けられた信号完全性モデルタイプは正確でなければなりません。これは、Signal Integrity Model Assignmentsダイアログを使用するか、回路図ソースドキュメント上に配置されたコンポーネントに関連付けられた信号完全性モデルを編集する際に、信号完全性モデルダイアログのタイプフィールドに正しいエントリを手動で設定することで達成されます。このエントリが定義されていない場合、Signal Integrity Model Assignmentsダイアログは、その特性に基づいてコンポーネントのタイプを推測しようとします。このエントリが定義されていない場合、タイプは統合回路と仮定されます。詳細については、Signal Integrity Model Assignmentsダイアログを使用したSIモデルの追加を参照してください。

-

電源ネットの設計ルールが必要です。一般に、電源ネット用とグラウンドネット用の少なくとも2つのルールがあるべきです。これらの範囲は、ネットまたはネットクラスのいずれかになります。電源ネットは信号完全性で分析できません。詳細については、回路図の信号完全性設計ルールまたはPCBの信号完全性設計ルールを参照してください。

-

信号励起の設計ルールを設定できます。デフォルトの励起を上書きしたい場合にのみ、励起ルールが必要ですので、これは一般的に必要ありません。

-

PCBのレイヤースタックが正しく設定されている必要があります。信号完全性アナライザーは連続した電源プレーンを要求します。分割プレーンはサポートされていないため、プレーンに割り当てられたネットが使用されます。存在しない場合は、仮定されるので、それらを追加して適切に設定する方がはるかに良いです。ボードのすべての層、コア、プレプレグの厚さも正しく設定されている必要があります。Design » Layer Stack Managerコマンドを使用して、PCBエディターでレイヤースタックを設定します。回路図のみモードで信号完全性を実行する場合、デフォルトの2層ボードで2つの内部プレーンが使用されます。より多くの制御が必要な場合は、レイヤースタックが設定された空のPCBを作成できます。レイヤースタックの定義ページで詳細を学ぶことができます。

信号の特性、例えば電圧レベルは、テスト中のネットの出力ピンに割り当てられたモデルによって決定されます。ピンモデルは、コンポーネントモデル割り当てプロセスの一部として割り当てられ、これらのコンポーネントレベルのモデル割り当ては、回路図を更新することで保持されます。個々のピンモデルも、例えばシグナルインテグリティパネルでピンをダブルクリックすることによって、上書きすることができますが、これらのピンレベルの再割り当ては編集セッション間で保持されません。

Signal Integrity Model Assignmentsダイアログを使用してSIモデルを追加する

デザインにシグナルインテグリティモデルを追加する最も簡単な方法は、Signal Integrity Model Assignmentsダイアログを使用することです。

-

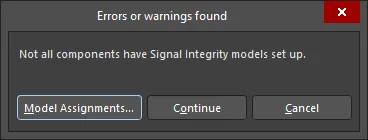

メニューからTools » Signal Integrityを選択します。プロジェクトでシグナルインテグリティを始めたばかりで、シグナルインテグリティモデルが添付されていないコンポーネントがある場合、エラーや警告が見つかりましたダイアログが表示され、Signal Integrity Model Assignmentsダイアログを使用してモデルの割り当てを設定するように促されます。

Errors or warnings foundダイアログ

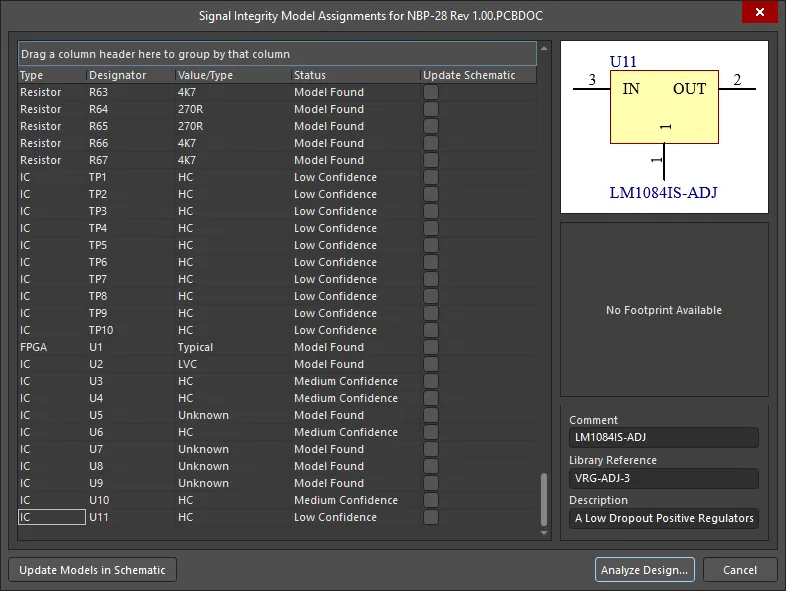

Signal Integrity Model Assignmentsダイアログ

また、ContinueをクリックしてSignal Integrityパネルが表示されている場合、パネル内のModel Assignmentsボタンをクリックすることで、いつでもSignal Integrity Model Assignmentsダイアログに入ることができます。これを行うと、モデル割り当ての変更により既存の結果が無効になるため、すべての結果がクリアされて再計算されることに注意してください。

すべてのコンポーネントに対してモデルが既に設定されている場合、SI設定オプションダイアログが表示されます。SI設定オプションの設定については、詳細をご覧ください。

-

Errors or warnings found ダイアログでModel Assignmentsをクリックすると、Signal Integrity Model Assignmentsダイアログが表示されます。

Signal Integrity Models Assignmentダイアログを実行すると、Signal Integrity Modelを含まない各コンポーネントに必要なSignal Integrity Modelを推測しようとします。モデルが既に定義されているコンポーネント(およびモデル情報)を含むすべてのコンポーネントがSignal Integrity Models Assignmentダイアログに表示されます。各コンポーネントには、次の表で説明されているステータスが割り当てられます。

| ステータス |

定義 |

| No match |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントを特定のタイプにリンクする特性を見つけることができませんでした。ユーザーによる修正が必要になる可能性が高いです。 |

| Low confidence |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントのタイプを選択しましたが、強い根拠はありませんでした。 |

| Medium confidence |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントのタイプを選択し、その推測にはそれなりの自信があります。 |

| High confidence |

Signal Integrity Model Assignmentsダイアログは、このコンポーネントのタイプを選択し、通常このタイプのコンポーネントに関連付けられる特性のほとんどに適合しています。 |

| Model found |

このコンポーネントの既存のモデルが見つかりました。 |

| User modified |

Signal Integrity Model Assignmentsダイアログの初期推測からユーザーが変更した場合、コンポーネントはこのステータスに変わります。 |

| Model added |

Signal Integrity Model Assignmentsダイアログを使用して回路図ドキュメントを変更し、新しいモデルを保存した場合に使用されるステータスです。 |

Signal Integrity Model Assignmentsダイアログを使用したコンポーネントモデルの変更

-

モデルを変更したいコンポーネントを選択します。

-

正しいタイプを選択します。シグナルインテグリティ用のコンポーネントには、抵抗器、コンデンサ、インダクタ、ダイオード、BJT、コネクタ、ICの7種類があります。各コンポーネントのタイプは、Type列のドロップダウンまたは右クリックメニューから選択できます。

-

抵抗器、コンデンサ、インダクタの値を設定します。可能であれば、Signal Integrity Model Assignmentsダイアログは、コンポーネントのコメントフィールドとパラメータに基づいてこの列にコンポーネントの正しい値を配置しようとします。これに変更が必要な場合(または存在しない場合)、この時点で行う必要があります。抵抗器アレイなどの部品アレイの特別なケースは、列内をクリックすることでアクセスできる別のダイアログを通じて行われます(詳細については、コンポーネントにシグナルインテグリティモデルを手動で追加するを参照してください)。

-

コンポーネントがICの場合、技術タイプの選択が重要です。これにより、分析に使用されるピンモデルの特性が決まります。これは、Value/Type列のドロップダウンリストを介して選択するか、右クリックメニュー(Change Technology)を通じてアクセスできます。

-

最後に、Signal Integrity Model Assignmentsダイアログで許可されている以上の詳細を指定する必要がある場合があります。これは、IBISモデルなどの場合です。これは、右クリックメニューからAdvancedを選択することで実現できます。このプロセスの詳細については、コンポーネントにシグナルインテグリティモデルを手動で追加するを参照してください。

モデルの保存

いずれかまたはすべてのコンポーネントに対してモデルが選択されたら、その情報を永続的に保存するために回路図ドキュメントを更新できます。

-

Signal Integrity Model割り当てダイアログで更新されるすべてのコンポーネントのUpdate Schematic列をチェックします。その後、Update Models in Schematicボタンをクリックします。

-

選択された各コンポーネントに対して、新しいSignal Integrity Model(または既存のものの変更)が回路図ドキュメントに追加されます。回路図ドキュメントは後で保存する必要があります。

信号整合性分析プロセスを進めるためにモデルを保存する必要はありません。モデルが保存されない場合、分析はSignal Integrity Model割り当てダイアログに現在表示されている通りのすべてのモデルで進行します。しかし、次に信号整合性ツールを使用する際には、いかなる変更も失われていることになります。

コンポーネントに手動で信号完全性モデルを追加する

回路図コンポーネントに信号完全性モデルを追加するには:

-

回路図エディターで配置されたコンポーネントの場合 - コンポーネントを選択し、Propertiesパネルを開きます。

-

回路図シンボルエディターで編集中のコンポーネントの場合 - SCHライブラリパネルでそのエントリを選択してアクティブにし、Propertiesパネルを開きます。

PropertiesパネルのParameters領域でAddボタンをクリックし、Signal Integrityを選択します。すると信号完全性モデルダイアログが開きます。

モデルを設定して、OKをクリックしてください。

受動部品の設定

抵抗器やコンデンサーなどの部品を設定する場合、通常、タイプと値を入力するだけで十分です。値はValueフィールドに入力でき、コンポーネント全体のパラメータとして設定できます。

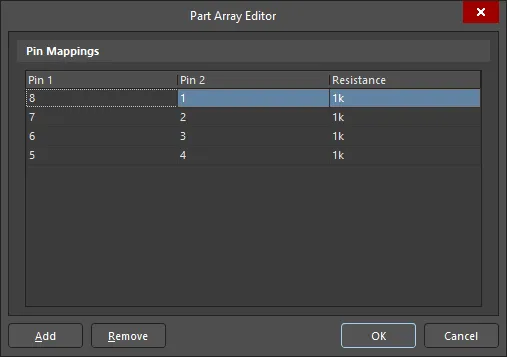

抵抗器アレイのようなコンポーネントのサポートもあります。これは、コンポーネントタイプを選択した後、Signal Integrity ModelダイアログでSetup Part Arrayボタンをクリックすることで実現できます。Part Array Editorダイアログでは、ピン間の接続やそれらの接続の値/モデルを設定できます。

Part Array Editorダイアログ

ICの設定

ICタイプモデルを設定する際には、いくつかの代替方法があります。

-

タイプ(IC)を選択した後、技術タイプを選択するだけで十分です。これにより、このコンポーネントをシミュレートする際に、その技術に適したピンモデルが使用されることが保証されます。利用可能な技術の完全なリストは、以下の折りたたみセクションにあります。

利用可能な技術タイプ

| 技術タイプ |

説明 |

| ABT |

高度なバイポーラCMOS技術 |

| AC |

高度なCMOS |

| ACT |

TTL入力付き高度なCMOS |

| AHC |

高速高度CMOS |

| AHC_50 |

5.0V高速高度CMOS |

| AHCT |

TTL入力付き高速高度CMOS |

| AHCT_50 |

5.0V TTL入力付き高速高度CMOS |

| ALS |

高度な低消費電力ショットキー |

| ALVC |

高度な低電圧CMOS |

| AS |

高度なショットキー |

| BCT |

バイポーラCMOS技術 |

| BTL |

バックプレーントランシーバロジック/フューチャーバス+ |

| CMOS |

CMOS |

| F |

FAST |

| FCT |

FAST CMOS技術 |

| GTL |

ガニングトランシーバロジック |

| GTL_LVT |

低電圧ガニングトランシーバロジック |

| HC |

高速CMOS |

| HCT |

TTL入力付き高速CMOS |

| HLL |

高速低消費電力低電圧CMOS |

| LS |

低消費電力ショットキー |

| LV |

低電圧高速CMOS |

| LVC |

低電圧CMOS |

| LVT |

低電圧BiCMOS技術 |

| S |

ショットキー |

| STD_TTL |

標準TTL |

| TTL |

TTL |

-

より細かい制御が必要な場合は、個々のピンに特定の技術やピンモデルを割り当てることができます。Signal Integrity Modelダイアログの下部にあるピンリストのドロップダウンリストから選択することでこれを行うことができます。ここでの変更は、コンポーネントの基本技術を上書きします。

IBISファイルのインポート

もう一つの重要なオプションは、IBISファイルをインポートする機能です。

-

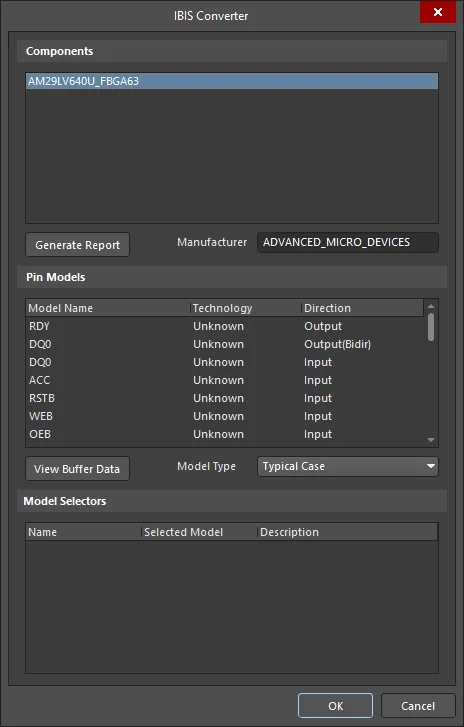

ICモデルの入出力特性を指定するためにIBIS(Input/Output Buffer Information)ファイルを使用するには、Signal Integrity ModelダイアログでImport IBISボタンをクリックします。IBISファイルを開くダイアログからIBISファイルを選択し、Openをクリックします。IBIS Converterダイアログが表示されます。

IBIS Converterダイアログ

-

IBISファイルに含まれる必要なコンポーネントを選択します。Altium DesignerはIBISファイルを読み込み、IBISファイルからピンモデルをインストール済みのピンモデルライブラリにインポートします。重複するモデルが見つかった場合、既存のモデルを上書きするかどうか尋ねられます。さらに、コンポーネント上のすべてのピンには、IBISファイルで指定された通りの適切なピンモデルが割り当てられます。

-

どのピンが成功裏に割り当てられたか、また割り当てられなかったかを示すレポートが自動的に生成されます。上記のように、適切なピンに対して手動でモデルを選択することによるさらなるカスタマイズが可能です。

-

OKをクリックしてIBIS情報のインポートを完了し、Signal Integrity Modelダイアログに戻ります。

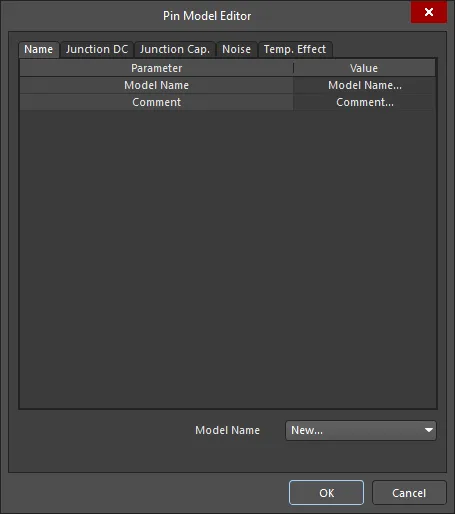

ピンモデルの編集

そのピンのさまざまな電気特性を指定することにより、既存のピンモデルを追加または編集することが可能です。この機能は、BJT、コネクタ、ダイオードなどの他のタイプにも利用可能であることに注意してください。

-

ピンモデルを変更するには、そのタイプで利用可能な場合、Signal Integrity ModelダイアログのAdd/Edit Modelボタンをクリックします。Pin Model Editorダイアログが表示されます。

Pin Model Editorダイアログ

-

Model NameのドロップダウンリストでNewをクリックします。

-

必要な変更を行い、OKをクリックします。

-

これが新しいピンモデルの場合、そのモデルはこの(および他の)コンポーネントのピンで選択できるようになります。

Ibisモデル実装エディタの使用

Altium Designer自身のシグナルインテグリティモデル形式(SIマクロモデルと呼ばれる)を使用できず、専用のIBISモデルを必要とするサードパーティツールのシグナルインテグリティシミュレーションをサポートするために、Altium Designerは専用のIBISモデル実装エディタを組み込んでいます。これにより、IBISモデルを回路図のコンポーネントに添付できます。したがって、以下のいずれかを行うことができます:

-

シグナルインテグリティ解析中にコンポーネントピンにIBISピンモデルをインポートする(上記のようにAltium Designer SIマクロモデルとして保存される)(IBISファイルのインポートを参照)、または

-

以下に説明するように、回路図のコンポーネントにIBISモデルを添付する。

この機能は、IBISモデル仕様の全バージョンをサポートしており、バージョン4.0まで含みます。

回路図コンポーネントにIBISモデルを追加するには:

-

回路図エディタ内で配置されたコンポーネントの場合 - コンポーネントを選択し、Propertiesパネルを開きます。

-

回路図シンボルエディタで編集中のコンポーネントの場合 - SCHライブラリパネルでそのエントリを選択してアクティブにし、Propertiesパネルを開きます。

PropertiesパネルのParameters領域でAddボタンをクリックし、Ibis Modelを選択します。IBIS Modelダイアログが開きます。

回路図コンポーネントには、IBISモデルのリンクを複数定義できますが、同時にアクティブにできるのは1つだけです。

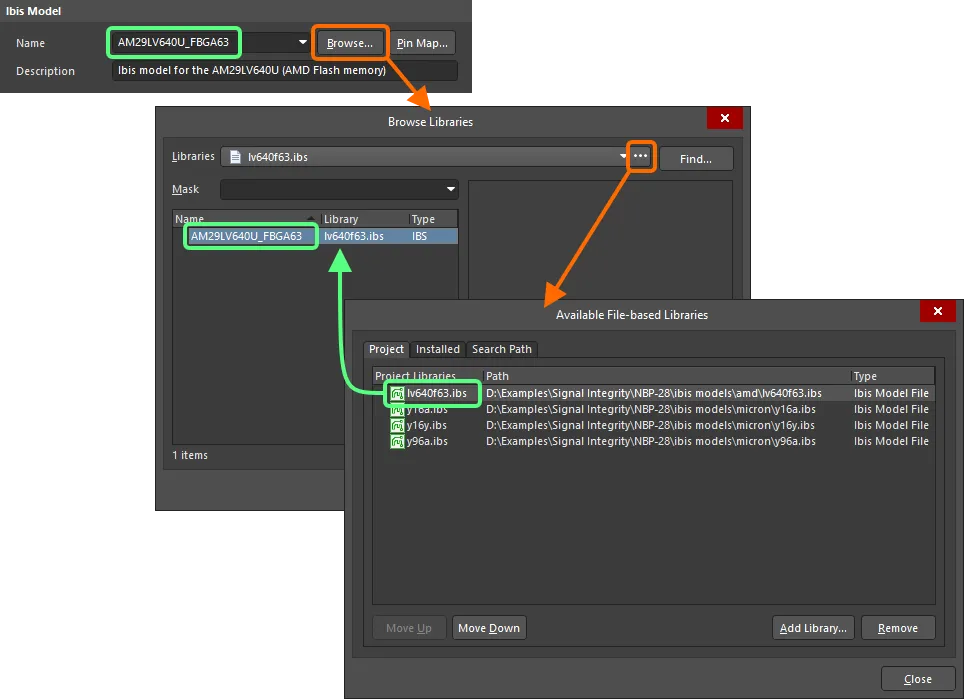

IBISモデル

モデルの名前を指定します - .ibsファイル内での正確な名前と一致させてください - そして、このドメインでの実装が何を表しているかを説明する意味のある名前をモデルリンクに付けてください。

特に名前がわからない場合は、Browseボタンを使用してBrowse Librariesダイアログにアクセスします。このダイアログを使用して、現在利用可能なライブラリ全体のIBISモデルファイルを参照します。必要なモデルファイルが現在利用可能なライブラリに含まれていない場合は、このダイアログのFind機能を使用します。

モデルの名前を直接指定するか、それを参照してください。

IBISファイルを検索する際、名前ドロップダウンではそのファイル内に定義されている全てのモデルが名前で表示されます。必要なものを選択するだけです。

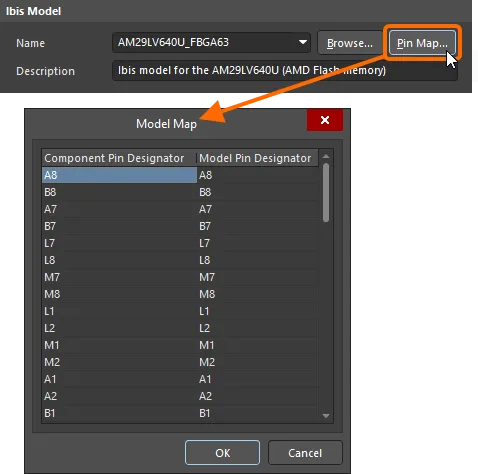

回路図のコンポーネントピンとIBISモデルピンのマッピングは、モデルマップダイアログで定義されており、Pin Mapボタンをクリックすることでアクセスできます。

モデルマップダイアログでコンポーネントからモデルへのピンマッピングを確認します。

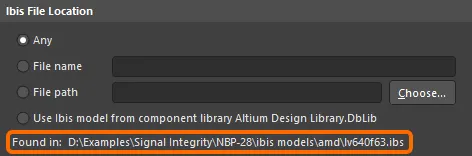

IBISファイルの場所

このIBISモデルダイアログの領域では、モデル名が定義されている場合に、ソフトウェアがモデルをどのように見つけるかを指定するためのオプションが利用可能です。

-

Any - 利用可能なすべてのライブラリ(プロジェクトライブラリ、インストールされたライブラリ、および定義された検索パスで見つかったライブラリ)がモデルを探すために使用されます。

-

File name - モデルが存在する完全なファイル名を入力してください(例:lv640f63.ibs)。利用可能なすべてのライブラリがモデルを探すために使用されます。ここで見つからない場合は、デフォルトのライブラリパス(PreferencesダイアログのSystem – Default LocationsページのLibrary Pathフィールド)が調べられ、指定されたファイルがそこにあるかどうかが確認されます。

-

File path - ファイルの完全なパス/名前を入力してください。Chooseボタンをクリックしてファイルを参照します。このオプションは、ファイルがそのディレクトリに残っている限り、明示的であるため、常にモデルを見つけます。

-

Integrated/Database Library - 配置後、コンポーネントが統合またはデータベースライブラリから配置された場合、そのライブラリが利用可能なライブラリセットの一部である限り、同じライブラリから直接モデルを取得できます。

モデルが見つかった場合、その場所が表示されます。

IBISモデルの検索方法を指定します。

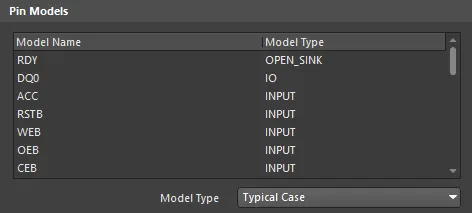

ピンモデル

このダイアログの領域では、選択したIBISモデルに定義されているピンモデルのリストが表示のみで提供されます。ただし、デフォルトのModel TypeであるTypical Caseから、Strong CaseまたはWeak Caseに変更することができます。

選択されたIBISモデルのピンモデル。

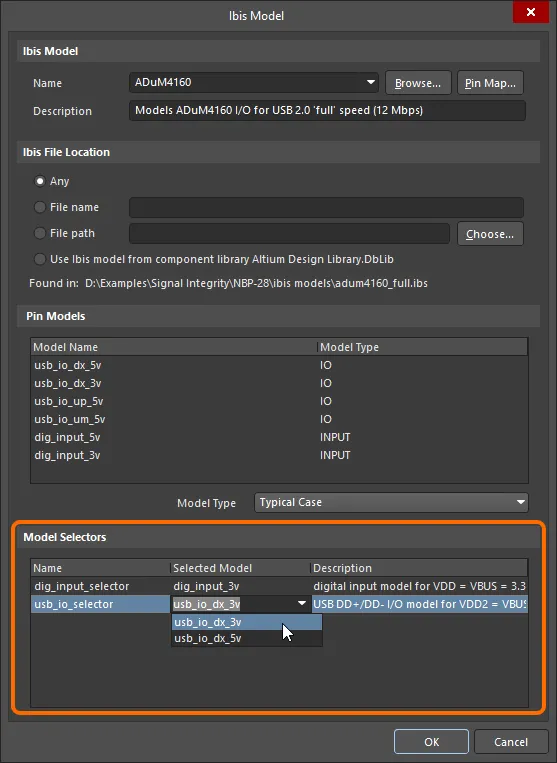

モデルセレクタ

Model Selectors領域は、選択されたIBISモデルにモデルセレクタが含まれている場合に表示されます。これにより、使用するモデルを選択できます(例えば、ピンには異なる電圧レベルのモデルがあるかもしれません;3.3V、5Vなど)。

定義されたモデルセレクタを持つ例のIBISモデル。

回路図内のシグナルインテグリティ設計ルール

シグナルインテグリティに関するPCB特有の設計ルールは、パラメータとして追加される場合、回路図内で定義することができます。

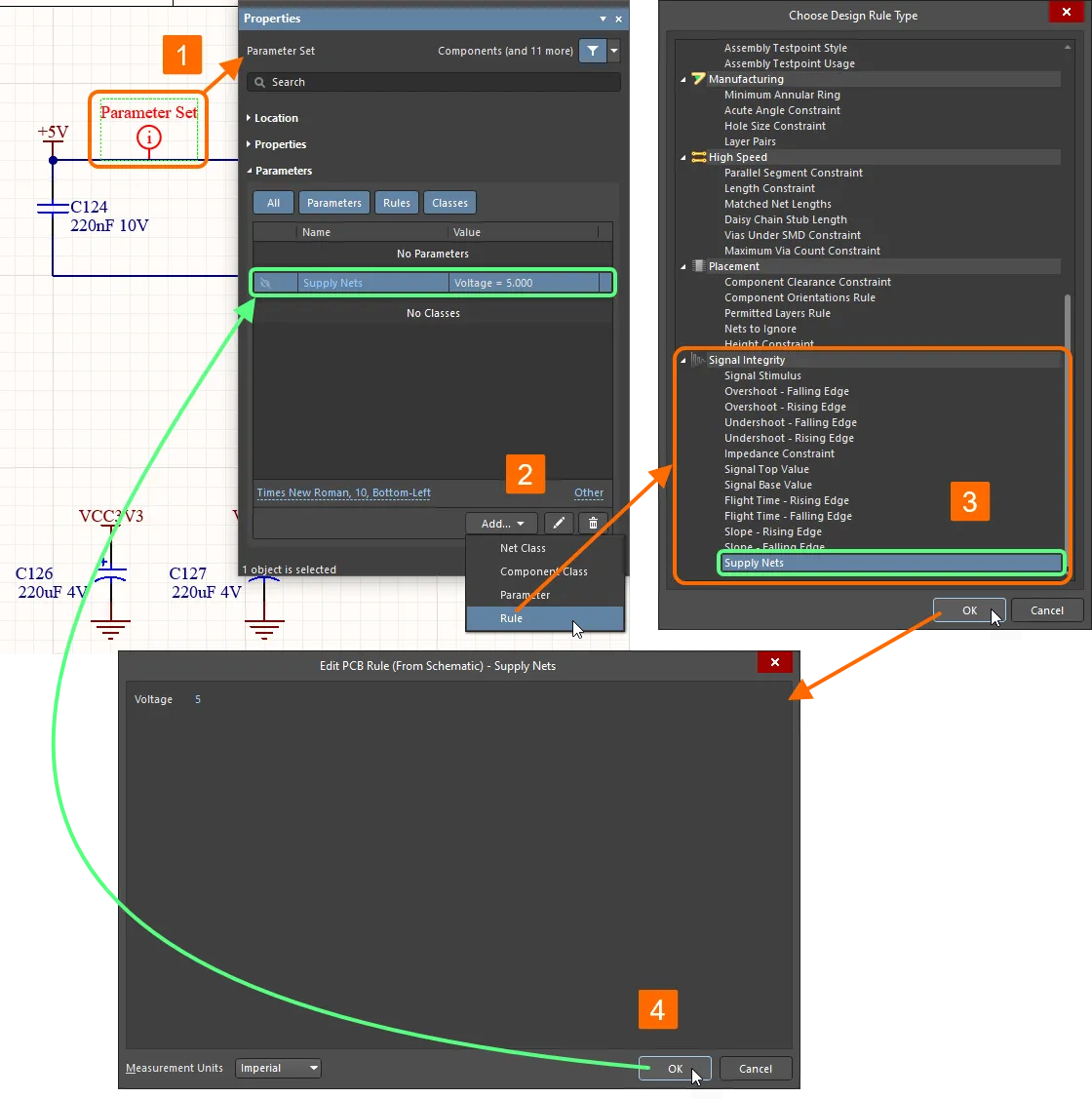

電源ネットの設計ルール

シグナルインテグリティ分析のために、パラメータセットディレクティブを使用して、供給ネットとその電圧を識別するためのPCBルールを追加する必要があります。回路図に供給ネットの設計ルールを追加するには:

-

パラメータセットディレクティブ(Place » Directive » Parameter Set)を適切なネットに配置します。

-

配置されたディレクティブが選択されたら、PropertiesパネルのParameters領域でAddボタンをクリックし、ドロップダウンメニューからRuleを選択します。

-

デザインルールタイプの選択ダイアログが開き、ルールタイプを選択できます。スクロールダウンしてSignal Integrityルールを選び、Supply Netsを選択してからOKをクリックします。

-

Edit PCB Rule (From Schematic) - Supply Netsダイアログが表示されます。このサプライネットの電圧を入力し、OKをクリックします。ルールエントリーがPropertiesパネルにリストされます。

シグナルインテグリティ設計ルールは、パラメータセットディレクティブを使用して回路図内に直接追加することができます。

設計をPCBレイアウトに転送した後、そのルールはPCB設計ルールに追加されます(PCB Rules and Constraints Editor ダイアログからアクセスでき、Design » Rulesコマンドを使用してPCBエディタで表示および編集が可能です)。

回路図エディタでは、ルールの対象範囲(ルールがターゲットにするオブジェクトのセット)は、パラメータが追加される場所(例えば、ワイヤーやピン上)によって定義されます。PCBエディタでは、ルールの対象範囲はルール自体内で定義されます。

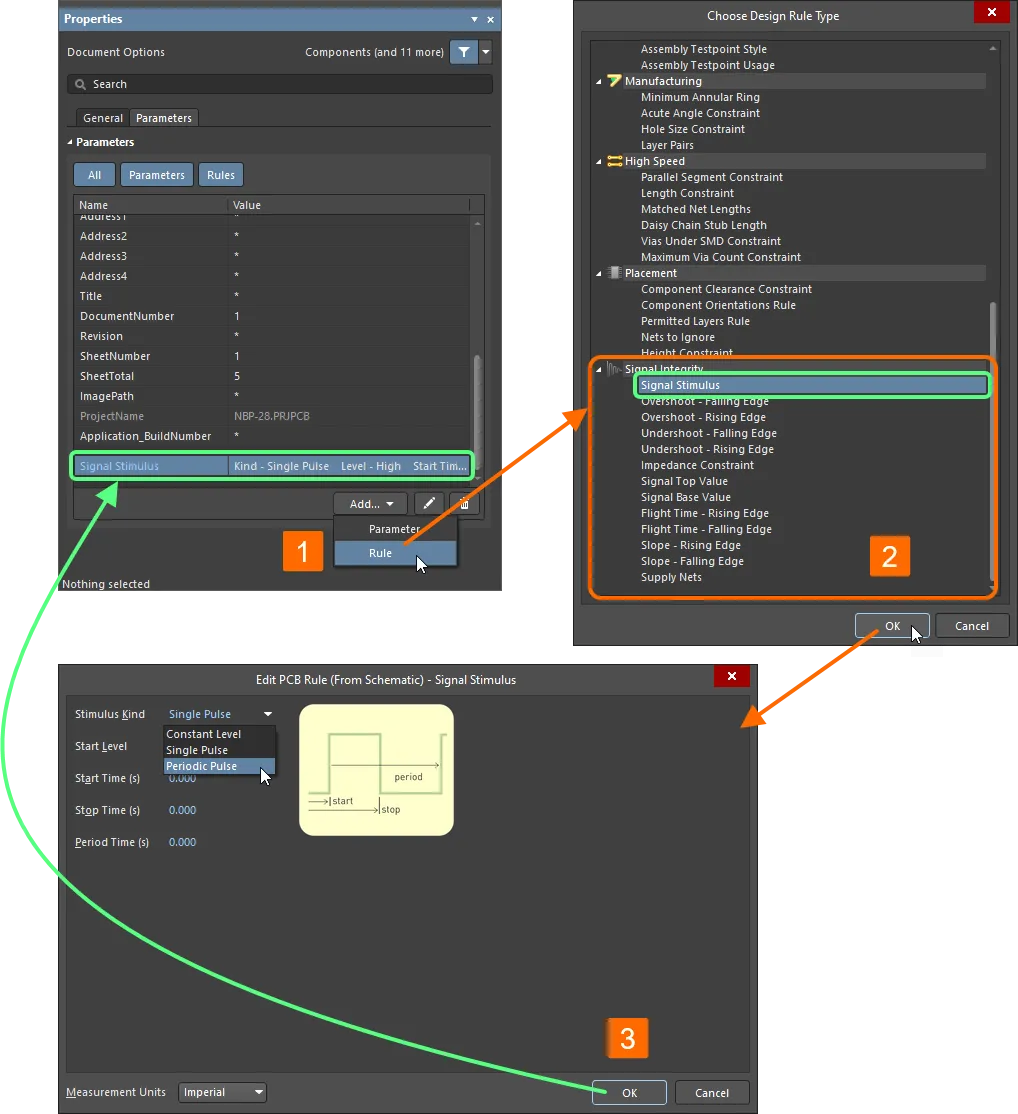

信号励起設計ルール

回路図エディタから設定できるもう一つの設計ルールは、信号励起ルールです。このルールを実行すると、分析されているネット上の各出力ピンに励起が注入されます。これには「all」という範囲を使用する設計ルールが必要なので、このルールのためにシートパラメータを作成する必要があります。このルールを設定しない場合、デフォルトのルールオプションが使用されます。

-

路図シートでオブジェクトが選択されていない場合、Propertiesパネルを開きます。パネルのParametersタブで、Addボタンをクリックし、ドロップダウンメニューからRuleを選択します。

-

設計ルールタイプを選択ダイアログが開き、ルールタイプを選択できます。 Signal Integrityルールまでスクロールダウンし、Supply Netsを選択してからOKをクリックします。

-

Edit PCB Rule (From Schematic) - Signal Stimulusダイアログが表示されます。励起の種類、開始レベル、時間を選択し、OKをクリックします。ルールエントリーがPropertiesパネルにリストされます。

シグナルインテグリティ設計ルールは、回路図シートパラメータとして追加できます。

PCBにおけるシグナルインテグリティ設計ルール

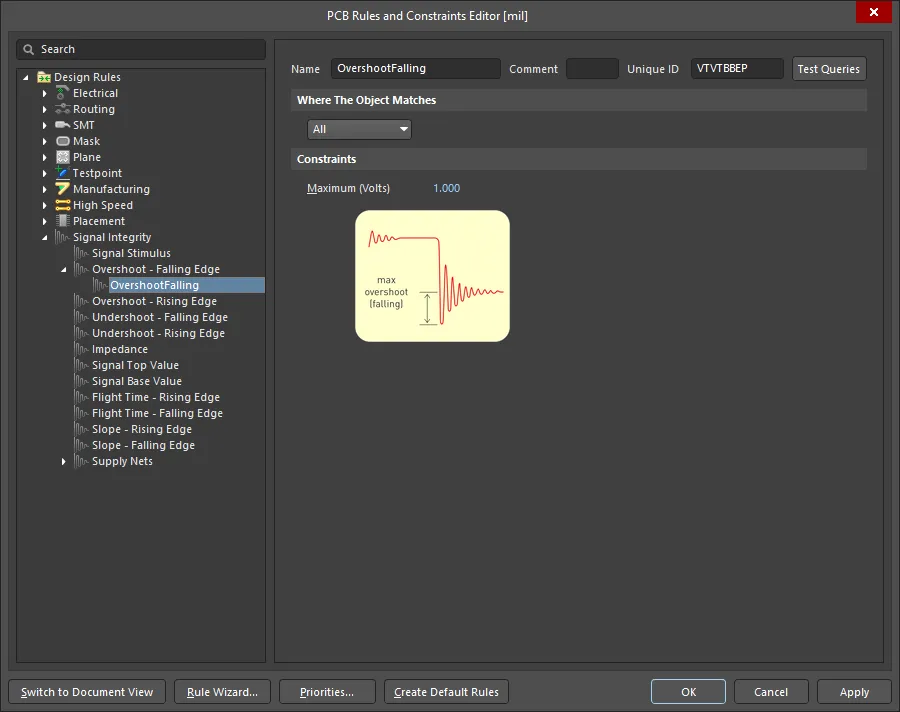

オーバーシュート、アンダーシュート、インピーダンス、信号勾配要件などのシグナルインテグリティパラメータは、標準のPCB設計ルールとして指定できます。Design » RulesをPCBエディタで選択し、PCBルールと制約エディタダイアログにアクセスしてこれらのルールを設定できます。これらのルールは、回路図エディタでパラメータを使用して設定することもでき、設計をPCBレイアウトに転送した後、PCBルールと制約エディタダイアログに表示されます。

オーバーシュート - 落下エッジ設計ルールを閲覧する際のPCB ルールと制約エディタダイアログ

これらのルールには2つの目的があります。1つ目は、PCB内で標準のDRCチェックを実行する際に、基板がこれらのルールに対して標準的なスクリーニング分析を使用してチェックされることです。2つ目の用途は、シグナルインテグリティパネルを使用する場合です。これらのルールはテストとして設定および有効化され、どのネットがどのテストに失敗したかをパネルがグラフィカルに表示します。

デザインが準備できたら、シグナルインテグリティ分析を設定して実行してください。