DRC の設定

デザインルールチェックの設定は、PCB ドキュメントからTools » Design Rule CheckコマンドでアクセスしたDesign Rule Checkerダイアログで行います。

Design Rule Checkerダイアログは、PCB エディタのパフォーマンスを向上させるために、特定のオンライン DRC チェックを無効にしたデフォルトを表示します。オンライン DRC やバッチ DRC の一部としてチェックするデザインルールタイプを含めるには、関連オプションを使用します。

Design Rule Checkerダイアログは、PCB エディタのパフォーマンスを向上させるために、特定のオンライン DRC チェックを無効にしたデフォルトを表示します。オンライン DRC やバッチ DRC の一部としてチェックするデザインルールタイプを含めるには、関連オプションを使用します。

Options and Controls of the Design Rule Checker Dialog

ダイアログの機能は基本的に2つの領域に分かれています:

-

バッチDRCに関するオプションの設定。

-

どのルールをチェックするか、オンラインDRCおよび/またはバッチDRCの一部としてこれらのルールをチェックするかどうかを設定します。

これらの領域は、左側のペインにあるフォルダのようなエントリに反映され、そこからアクセスできます。

レポートオプション

Report Optionsフォルダをクリックすると、ダイアログの右側にバッチDRC実行時に使用できる追加オプションが表示されます。

DRCレポートオプション

-

Create Report File- このオプションを有効にすると、ボードのバッチDRC実行後にレポートが生成されます。

レポートはHTML形式で、

Design Rule Check -.htmlという名前になります。バッチDRCプロセスが完了すると、自動的にアクティブなドキュメントとして開かれます。

-

Create Violations- このオプションを有効にすると、定義された違反の表示設定に従ってデザインスペースで違反がハイライトされます。このオプションは、PCB Rules And Violations パネルの Violations 領域で違反を表示するためにも必要です。

-

Sub-Net Details-Un-Routed Netルールが定義されている場合、DRC レポートにサブネットの詳細を含めるためにこのオプションを有効にします。

Un-Routed Netルールは、すべてのコネクションが配線された場合にのみ有効にしてください。

-

Verify Shorting Copper- このオプションを有効にすると、デザインに使用されている Net Tie コンポーネントの短絡銅線の完全性を確認できます。このチェックでは、コンポーネント内の未接続の銅(パッドが他のパッドと正しく短絡していないことを示す)を探します。

-

Report Drilled SMT Pads- このオプションを有効にすると、DRCレポートに誤って穴あけされたSMT(表面実装技術)パッドが含まれます。

SMTパッドは、例えば、ショートピン、フラットコンタクト、ボールマトリックス(BGA)の1つ、部品本体の終端(パッシブ)、ガルウィング形成のショートリード(QFP)などがあります。

このオプションは、穴が定義されたSMTパッドを検出するためのもので、旧バージョンのソフトウェアでは可能でした。SMDパッド下のビアをチェックするには、

Vias Under SMDルール(

High Speedカテゴリ)をデザインに追加し、バッチDRCで有効にする必要があります。

-

Report Multilayer Pads with 0 size Hole- このオプションを有効にすると、デザイン内で無効なマルチレイヤーパッドが検出されます。無効なマルチレイヤーパッドとは、穴のサイズが0であり、SMTパッドとなるものです。

-

Stop when n violations found- このフィールドを使用して、バッチ DRC プロセスを停止する前に検出できる違反の最大数を決定します(デフォルト =500)。報告される違反の数を制限することは、チェックプロセスを管理しやすく保つための重要な戦略です。

分割プレーンDRCレポートオプション

-

Report Broken Planes- このオプションを有効にすると、バッチ ルール チェック プロセスでプレーンの破損を検索してレポートします。プレーンの破損は、ネットへの接続性を持つプレーンの領域が、プレーンの残りの部分から電気的に切断された場合に発生します。これが発生する例としては、分割されたプレーンを横切って配置されたコネクターがありますが、これには接続されていません。ピンの周りのボイドがプレーンの銅を完全に切り裂くように結合し、事実上プレーンを2つの部分に分割する。

プレーンの破損をチェックするには、バッチ DRC で(

Electricalカテゴリの)

Un-Routed Netルールを有効にする必要があります。

-

Report Dead Copper larger than- このオプションを有効にすると、バッチ ルールのチェック プロセスで、指定した領域よりも大きなデッド カッパー領域を検索し、レポートします。デッド・カッパーとは、ネットへの接続性がなく、元の親プレーンから電気的に切り離された銅線のセクションを指します。これが発生する例としては、ピンの間隔が狭いコネクタ(プレーンに接続されていない)があり、ピンの周りの空隙がプレーンの銅の領域をプレーンの残りの部分から分離するために結合します。関連するフィールドを使用して、デッド銅の最大許容面積の値を指定し、それを超えるとルール違反とみなされます(デフォルト=100 sq. mils)。

デッドカッパーをチェックするには、(Electricalカテゴリの)Un-Routed NetルールをBatch DRCで有効にする必要があります。

Report Dead Copper larger thanオプションが有効な場合(そして、Un-Routed Netルールがバッチ DRC で有効な場合)、サイズに関係なく、ネットが割り当てられていない全てのオブジェクトもバッチルールチェック中に報告されます。この機能は、Advanced Settings ダイアログの PCB.Rules.DeadCopperNoNetオプションの値を設定することで利用できます。デフォルト値は2 です。

また、Report Dead Copper larger thanオプションが有効な場合、ネット割り当てがあるが、同じネットのどのパッドオブジェクトにも接続されておらず、接続線で同じネットの他のオブジェクトに接続されていない銅層オブジェクトはチェックされます(バッチ DRC でUn-Routed Netルールが有効かどうかに関係なく)。この機能はオープンベータ版で、PCB.Rules.DeadCopperInNetオプションがAdvanced Settings ダイアログで有効な場合に利用できます。

-

Report Starved Thermals with less than n% available copper- バッチルールチェックプロセスで、指定されたパーセンテージより大きい 'starved' サーマル接続を検索し、レポートするためにこのオプションを有効にします。サーマルとは、プレーン銅への熱伝導を低減するために、周囲にサーマルリリーフ「カットアウト」を設けたプレーンへの接続のことです。プレーンに接続する銅スポークの表面積がボイド領域によって減少すると、サーマルは「飢餓状態」になる可能性があります。このオプションは、サーマルに侵入するボイドエリアに対して、サーマルの表面積(スポークだけでなく)もチェックします。関連するフィールドを使用して、接続する銅の最小許容割合を指定し、それを下回るとルール違反とみなされます(デフォルト=50%)。

-

Run Design Rule Check- このボタンをクリックすると、バッチ・チェックで有効化されたルールと、このタイプのチェック用に定義された追加オプションに従ってバッチDRCが実行されます。

チェックが完了すると、すべての違反がMessagesパネルに表示されます。

チェックすべきルール

Rules To Checkフォルダをクリックすると、ダイアログの右側にチェック可能なすべてのルール・タイプのリストが表示されます。また、特定のカテゴリ(フォルダの下)をクリックすると、そのカテゴリに関連するデザイン・ルール・タイプのみがリストアップされます。

各ルール・タイプについて、以下の情報が表示されます;

-

Rule- ルールの種類。

-

Category- ルールの種類が関連付けられる親カテゴリ。

-

Online- オンラインDRCに関するこのルールタイプの現在の状態(利用可能な場合)。クリックして切り替えます。

-

Batch- バッチ DRC に関するこのルール タイプの現在の状態。クリックして切り替えます。

必要に応じて、各ルールタイプをオンラインおよび/またはバッチチェック用に有効にする。

右クリックメニューを使用して、オンラインDRCまたはバッチDRCのすべてのルールタイプの有効化/無効化、または使用する(定義済みで使用可能な)ルールタイプのみをすばやく有効化/無効化するコマンドにアクセスできます。

注意事項

-

生成されたDesign Rule Verification Reportには、このダイアログで指定されたバッチ・チェック・プロセスでテストされた各ルールが一覧表示されます。検出された各違反は、オブジェクトの位置だけでなく、レイヤ、ネット名、コンポーネント・指定子、パッド番号などの参照情報の詳細とともにリストアップされます。違反オブジェクトのエントリーをクリックすると、デザインスペース内のそのオブジェクトに直接クロスプローブします。

-

デザイン・スペースにルール違反を表示する際の柔軟性を高めるため、2つの違反表示タイプ(違反の詳細(カスタム違反グラフィックス)と違反のオーバーレイ)には、それぞれ別のシステム・カラーが関連付けられています。これにより、異なる色を使用して両者を区別することができます。色の割り当ては、View ConfigurationパネルのLayers & Colorsタブで行います:

-

違反の詳細- System Colors領域のViolation Markersカラーに割り当てられたカラーを使用します。

-

Violation Overlay-System Colors領域のDRC Error Markers色に割り当てられた色を使用する。

-

バッチDRCを実行した後、Messagesパネルの違反メッセージをダブルクリックすると、デザインスペース内の違反の原因となっているオブジェクトをクロスプローブできます。

-

Online または Batch DRC を実行すると、PCB Rules and Violations パネルのViolations領域にルール違反が表示されます。

-

特定のデザインオブジェクトに関連する違反は、PCB デザインスペース内で直接問い合わせることができます。違反オブジェクトの上にカーソルを置き、右クリックし、Violationsサブメニューからコマンドを選択します。オブジェクトが関与している個々の違反を調査するか、Show All Violationsコマンドを使用して、オブジェクトが関与している全ての違反を表示するかを選択します。いずれの場合も、Violation Detailsダイアログが表示され、違反の詳細情報と、違反オブジェクトをハイライトしたりジャンプしたりするためのコントロールが提供されます。

ダイアログの左側にあるフォルダツリーペインでは、ルールタイプをチェックできるデザインルールの各カテゴリが、Rules To Checkフォルダの下に表示されます。この最上位のフォルダをクリックすると、チェック可能なすべてのルール・タイプがダイアログの右側に一覧表示されます。また、特定のカテゴリーをクリックすると、そのカテゴリーに関連するデザイン・ルール・タイプのみがリストアップされます。ダイアログを使用して、チェックするルール・タイプごとにオンライン・チェック(利用可能な場合)および/またはバッチ・モード・チェックを有効/無効にします。

右クリック・メニューを使用して、Online または Batch DRC のすべてのルール・タイプの有効化/無効化、または使用されている(デザインで使用するために定義され、有効化されている)ルール・タイプのみを素早く有効化/無効化するコマンドにアクセスできます。

特に、バッチ・モードのデザイン・ルール・チェックは、最終的なアートワークを生成する前に必ず実行することをお勧めします。オンラインDRCは新しい違反(機能が有効化された後に作成された違反)のみを検出しますが、バッチDRCではボード設計プロセス中にいつでも手動でチェックを実行することができます。そのため、優れた設計者はオンラインDRCの価値を知っている一方で、基板設計はバッチDRCで始まり、バッチDRCで終わるべきであることも知っています。バッチDRCの設定オプションの詳細については、バッチDRCの使用を参照してください。

オンラインDRCの使用

オンライン・デザイン・ルール・チェックはバックグラウンドでリアルタイムに実行され、デザイン・ルール違反のフラグを立てたり自動的に防止します。これは、クリアランス、幅、平行セグメント違反を即座にハイライトするため、基板をインタラクティブに配線する場合に特に役立ちます。ルールをオンラインDRCの対象とするには、以下の3つの要件を満たす必要があります:

-

ルールが有効になっていること。これは、PCB Rules and Constraints Editor ダイアログで、ルールのEnabled オプションがチェックされていることを確認するか、PCB Rules and Violations パネルで、ルールのOn オプションがチェックされていることを確認します。

オンライン DRC で監視したいデザインルールが、デザインで使用するために実際に有効になっていることを確認します。

オンライン DRC で監視したいデザインルールが、デザインで使用するために実際に有効になっていることを確認します。

-

ルールタイプは、Design Rule Checkerダイアログでオンラインチェックのために有効になっている必要があります。

ルールタイプがオンラインDRCで有効になっていることを確認します。

ルールタイプがオンラインDRCで有効になっていることを確認します。

-

Online DRC 機能を有効にする必要があります。これを行うには、PreferencesダイアログのPCB Editor - General ページでOnline DRCオプションを有効にします。

オンライン DRC 機能が有効になっていることを確認します。

オンライン DRC 機能が有効になっていることを確認します。

もし、オブジェクトがオンラインチェックを有効にしている適用可能なデザインルールに違反している場合、定義された違反表示オプションに従い、デザインスペースでハイライト表示されます。

オンライン DRC 処理は、マルチスレッドとデザインの可視領域に関連するプリミティブの優先順位付けを含むように最適化できます。

この機能はオープンベータ版で、Advanced Settings ダイアログでPCB.DRC.OnlineOptimizationオプションが有効な場合に利用できます。

バッチ DRC の使用

Online DRC が新しい違反(機能が有効になった後に作成された違反)だけを検出するのに対して、Batch DRC はボード設計プロセス中にいつでも手動でチェックを実行できます。そのため、優れた設計者はオンラインDRCの価値を知っていますが、ボード設計はバッチDRCで始まり、バッチDRCで終わるべきであることも知っています。

既存のエラーマーカーをクリアするには、PCB エディタメニューからTools » Reset Error Markersを選択します。

必要に応じて、Design Rule Checkerダイアログでバッチチェックのルールタイプを有効にします(Configuring the DRCセクションを参照してください)。Batch DRC を実行する時、レポートファイルを生成する機能を含む様々な追加オプションが利用できます。これらのオプションには、ダイアログのフォルダツリーペインのReport Optionsフォルダをクリックすることでアクセスできます。主なオプションは以下の2つです:

-

Create Report File- DRC レポートを生成するためにこのオプションを有効にします。生成されたレポートにPCBヘルスチェックモニタで検出された問題を含めるために、Report PCB Health Issuesサブオプションを有効にします。

-

Create Violations- このオプションを有効にして、定義された違反表示オプションに従い、違反がデザインスペースでハイライトされるようにします。このオプションは、PCB Rules And ViolationsパネルのViolations 領域にリストされた違反を表示するためにも必要です。

Batch DRC の実行、DRC レポートの生成に適用するオプションにアクセスします。

Batch DRC の実行、DRC レポートの生成に適用するオプションにアクセスします。

バッチモード DRC は、ダイアログの左下にあるRun Design Rule Checkボタンをクリックすることで開始します。チェックが完了すると、すべての違反がメッセージとしてMessagesパネルに表示されます。このオプションを選択した場合、DRC レポートが作成され、メイン デザイン ウィンドウのアクティブ ドキュメントとして自動的に開かれます(そのように設定されている場合)。レポートには、Design Rule Checker ダイアログで指定されたテストされた各ルールがリストされます。デザインに存在しないルールはテストされません。

DRC レポート

Design Rule Checker ダイアログでCreate Report Fileオプションを有効にすると、バッチ DRC 実行時に DRC レポートを生成します。PreferencesダイアログのPCB Editor - Reports ページで利用可能なオプションは、レポートフォーマットの指定、生成後にレポートを自動的に表示するかどうかを設定できます。

Batch DRC プロセスの一部として DRC レポートを生成します。

サポートされているフォーマットは以下の通りです:

-

TXT- ファイルDesign Rule Check -.drc を生成します。

-

HTML- ファイルDesign Rule Check -.html を生成します。

-

XML- ファイル.xmlを生成します。

レポートには、Design Rule Checkerダイアログで指定されたバッチチェックプロセスでテストされた各ルールがリストされます。検出された各違反は、オブジェクトの位置だけでなく、レイヤ、ネット名、コンポーネント指定子、パッド番号などの参照情報の詳細とともにリストされます。

HTML形式のレポートでは、違反オブジェクトのエントリーをクリックすると、デザインスペース内のそのオブジェクトに直接クロスプローブします。このクリック操作のズーム・レベルは、PreferencesダイアログのSystem - Navigationページで設定します。

違反表示オプション

指定されたデザインルールに照らしてデザインをチェックすることは1つのことですが、1つ以上のルールに違反した場合はどうなるのでしょうか?設計中に Online DRC を実行するか、手動で Batch DRC を実行するかに関わらず、そのようなルール違反が発生している場所を視覚的に表示する必要があります。PCB エディタには、明確で視覚的な方法で違反が存在する場所を示す強力な違反表示オプションが含まれています。

カスタム違反グラフィック

オンライン/バッチデザインルールチェックのどちらかに含めることができるほとんどのデザインルールには、特定のルールが違反した時にデザインスペース内に表示されるカスタム違反グラフィックがあります。これらのグラフィックは、視覚的にすっきりとしたDRC景観を提供します。特定のデザイン・ルールに違反した場合、関連するカスタム違反グラフィックス(該当する場合)は、その違反に関連するレイヤーにのみ描画されます。

場合によっては、違反が発生している場所だけでなく、その理由(ルールに定義された制約値を表示し、違反しているプリミティブがこの値より下または上にあることを示す)もグラフィックで表示されます。

幅と最小環状リングのルール違反に使用されるカスタムグラフィックの例。

幅と最小環状リングのルール違反に使用されるカスタムグラフィックの例。

ネットアンテナ、ショートサーキット、非配線ネット、ルーム定義、レイヤーペア、SMD下のバイアスのルール違反を表すために使用されるものを含む他のグラフィックは、表示される定義可能な制約値がないため、グラフィックとなります。

カスタム違反グラフィックの追加例。左からNet Antennae違反; Short-Circuit違反; Un-Routed Net違反。

カスタム違反グラフィックの追加例。左からNet Antennae違反; Short-Circuit違反; Un-Routed Net違反。

違反オーバーレイ

カスタムバイオレーショングラフィックスに加え、バイオレーション「オーバーレイ」をセットアップして使用することができます。オーバーレイはデザインプリミティブの上に描画されます。プリミティブ上にどのようなパターンを表示するかは、スタイルの中から選択できます。

DRC違反を表示する場合、カスタム違反グラフィックスの代替として違反オーバーレイを使用します。

DRC違反を表示する場合、カスタム違反グラフィックスの代替として違反オーバーレイを使用します。

2つの違反表示を組み合わせて使用すると、違反の「粗い」表示と「細かい」表示を提供する点で便利です。違反オーバーレイをズームアウトすると、違反が存在する場所にフラグを立てることができ、その後ズームインすると、関連するカスタム違反グラフィックによって詳細が表示されます。

違反表示の設定

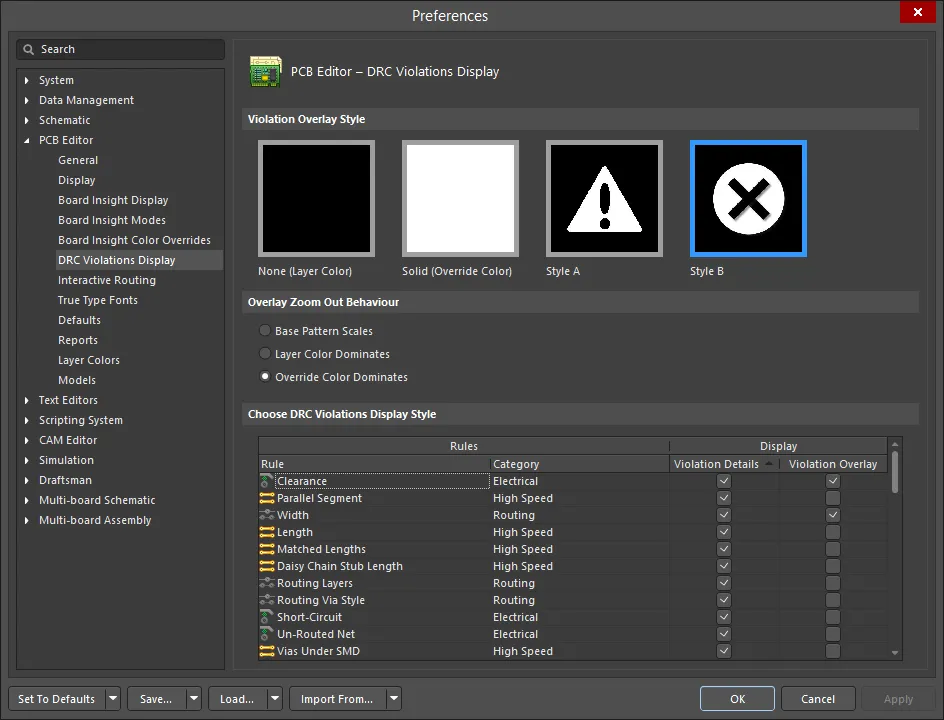

カスタムバイオレーショングラフィックや定義されたバイオレーションオーバーレイを使用した DRC バイオレーションの表示方法のコントロールは、PreferencesダイアログのPCB Editor - DRC Violations Display ページで指定します。

カスタムグラフィックや定義された違反オーバーレイを使用して、DRC 違反がデザインスペースでどのように表示されるかを設定します。

利用可能なオプション

-

Violation Overlay Styleを使用して、違反オーバーレイのスタイルを選択します。クリックしてお好みのスタイルを選択してください:

-

None (Layer Color)- エラーマーカーはレイヤーの色で表示されるため、表示されません。

-

Solid (Override Color)- エラー・マーカーはエラー・マーカー・レイヤの色で表示されます。

-

Style A- エラーマーカーは警告の三角形で表示されます。

-

Style B- エラーマーカーはドットの中に十字が表示されます。

-

Overlay Zoom Out Behaviorを使用して、ズームアウト時の違反オーバーレイの表示動作を決定します:

-

Base Pattern Scales- エラー・マーカーはズーム・レベルに関係なくスケールされます(マーカーのタイプは上記で選択した違反オーバーレイ・スタイルによって決まります)。

-

Layer Color Dominates- ズームアウトすると、エラーマーカーはレイヤーの色のベタ領域になります。

-

Override Color Dominates- ズームアウトすると、エラーマーカーがレイヤーカラーの色のベタになる。

-

ルールごとに、Choose DRC Violations Display Style領域で使用する表示スタイルを選択します。ルールタイプのViolation Detailsオプションを有効にすると、関連するカスタム違反のグラフィックが使用され、そのルールのDRC違反が表示されます。Violation Overlayオプションを有効にすると、指定されたオーバーレイ・スタイルで違反が表示されます。デフォルトでは、Violation Details表示スタイルはすべてのルールタイプで有効になり、Violation Overlay Style表示はクリアランス、幅、およびコンポーネントクリアランスルールでのみ有効になります。

グリッド内で右クリックすると、コマンドのメニューにアクセスし、すべてのルールタイプで違反表示タイプの使用をすばやく有効または無効にできます。また、現在デザインで使用されているルールに対してのみ、違反の表示(詳細グラフィックまたはオーバーレイスタイル)を素早く有効にするコマンドも用意されています。

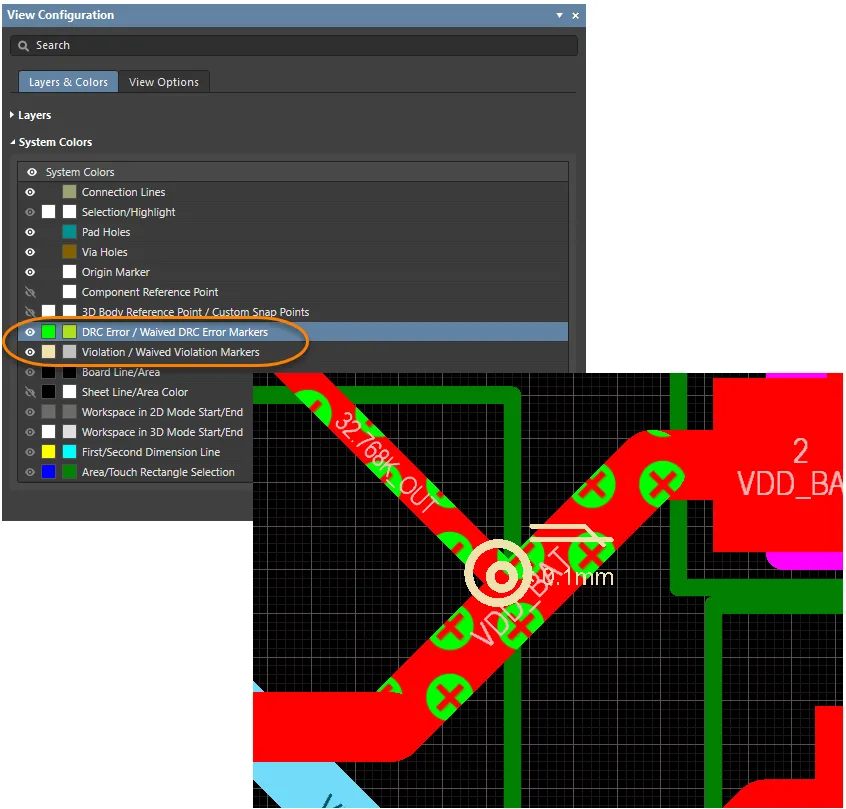

違反のカラーリングの定義

デザイン・スペースでルール違反を表示する際の柔軟性をさらに高めるため、違反の詳細(カスタム違反グラフィック)と違反のオーバーレイという2つの違反表示タイプには、それぞれ関連するシステムカラーがあります。これによって、異なる色を使用して 2 つを区別できます。色の割り当ては、View ConfigurationパネルのLayers & ColorsタブにあるSystem Colorsセクションで行います:

-

違反の詳細-Violation Markersのシステムカラーを使用します(この表示スタイルで放棄された違反については、Waived Violation Markersのシステムカラーを使用します)。

-

違反のオーバーレイ-DRC Error Markersのシステムカラーを使用します(この表示スタイルを使用して放棄された違反については、Waived DRC Error Markersのシステムカラーを使用します)。

2つの違反表示タイプに異なるカラーリングを指定し、必要に応じて表示を有効/無効にします。

2つの違反表示タイプに異なるカラーリングを指定し、必要に応じて表示を有効/無効にします。

使用する違反表示タイプについて、可視アイコン(色見本の左側)が有効(

)になっていることを確認します。そうでない場合、関連する違反の詳細または違反のオーバーレイは表示されません。