ピンパッケージ遅延の対応

This document is no longer available beyond version 16.0. Information can now be found here: Pin Package Delay for version 25

ピンパッケージ遅延の管理

500 MHz 以上の高速設計で、デバイスの接続媒体、またはダイ ワイヤ・ボンディングによる信号の遅延が発生します。このデバイス内の遅延は、ピンパッケージ遅延と呼ばれます。デザインや PCB 側から見て、2 つのデバイスのピンが一致していても、パッケージへ信号が流れる時間は、デバイスによって異なります。そのため、それを考慮する必要があります。パッケージへ信号が流れる時間は、デバイスに関する IBIS 6 document に記載されています。パッケージのピン情報は、I/O を決める段階で、またはFPGA での論理合成後に考慮する必要があります。

全てのデバイスメーカーは、パッケージの遅延情報(picosecond 遅延、または配線長として示す)を提供する必要があります。Altium は、配線長の方法を使用します。この方法により、同じ配線長を容易に定義できます。

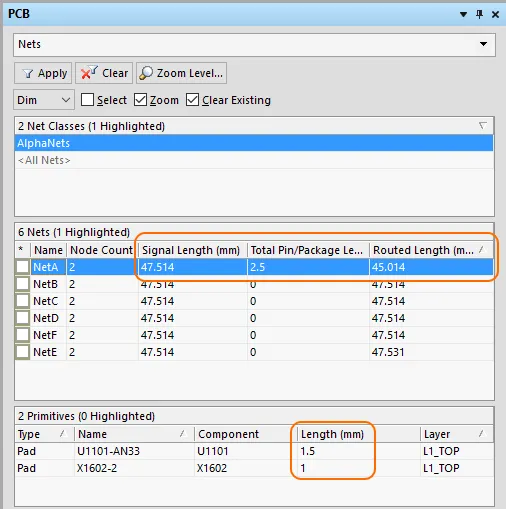

ピンパッケージの配線長は、全体の 信号配線長 に含まれています。これは、PCB パネルの様々なモード(Nets モードや xSignal モードを含む)で確認できます。

回路図で遅延を含める

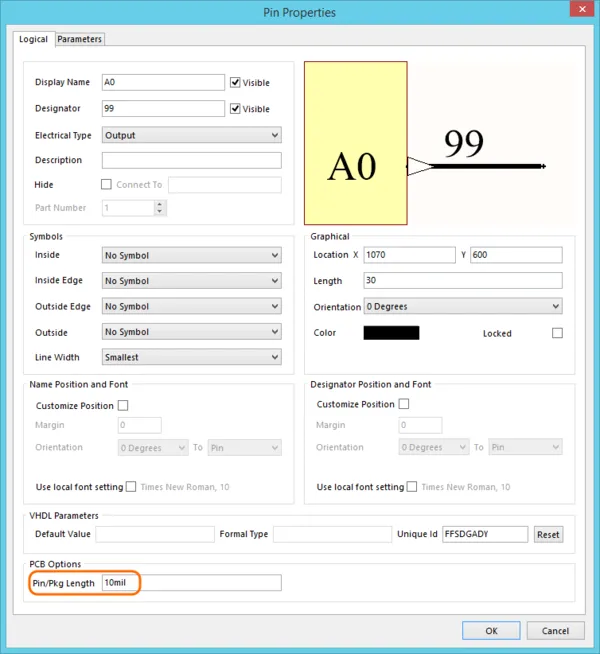

ピンパッケージの配線長は、回路図コンポーネントピンの属性として Pin Properties ダイアログの Pin/Pkg Length 欄で定義できます。配線長の単位は、そのファイルで設定されている単位が使用されます。

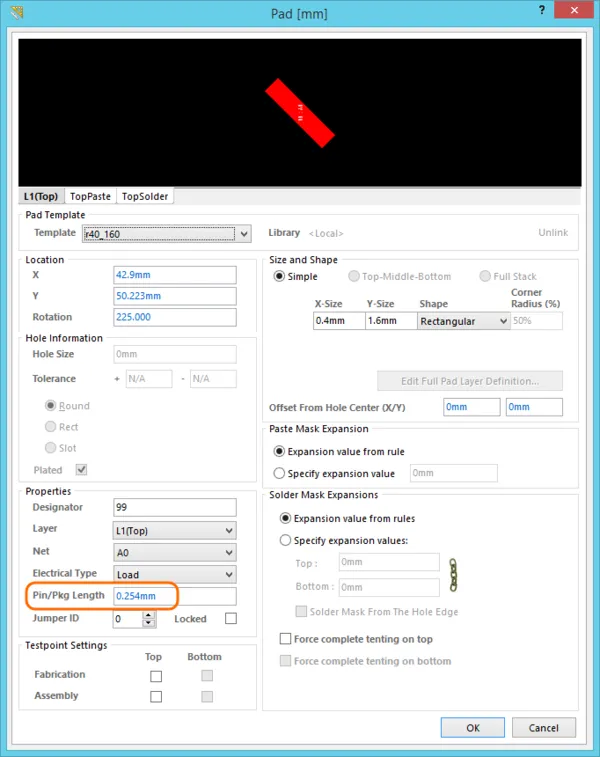

配線長の値は、PCB レイアウトへ移行されます。これは、フットプリントパッドの Pin/Pkg Length になります。

配線長は、回路図から PCB へ移行されます。また、PCB でも定義できます。

PCB パネルでピンパッケージの配線長を確認

ピンパッケージの配線長 は、自動で Signal Length に含まれます。これは、PCB パネルの様々なモードで表示されます。ネットのピンに関する ピンパッケージの配線長 の値を確認(または、編集)するには、パネルを Nets モードに設定します。Routed Length 欄に配線長が、Signal Length 欄に配線長と、ピンパッケージの配線長を足した値が表示されることに注意してください。

ピンパッケージの配線長と、信号配線長は、PCB パネルのNets モードで表示されます。

xSignal に含まれる配線長

以下の場合、ピンパッケージの配線長は、自動で全体の xSignal 配線長に含まれます:

- その信号を、xSignal で定義している。

- そのパッドは、空中配線で接続されていない(1 つの配線のみパッドに接続されている)。