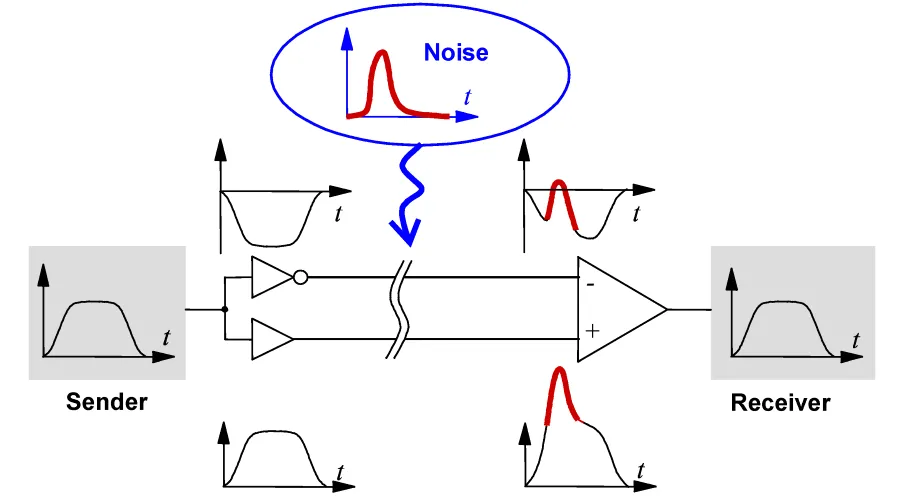

差動ペア配線は、差動(等しく反対の)信号をプリント基板上で伝送できるバランスの取れた伝送システムを作成するために使用される設計技術です。通常、この差動配線は外部の差動伝送システム、例えばコネクタやケーブルに接続されます。

差動信号システムとは、信号が密接に結合された一対のキャリアを介して送信されるシステムで、そのうちの一方が信号を、もう一方が信号の等しいが反対のイメージを運ぶものです。差動信号は、信号源の論理参照グランドが負荷の論理参照グランドにうまく接続できない状況に対応するために開発されました。差動信号は、電子製品に存在する最も一般的な干渉アーティファクトである共通モード電気ノイズに対して本質的に免疫があります。差動信号のもう一つの大きな利点は、信号ペアから発生する電磁干渉(EMI)を最小限に抑えることができることです。

差動ペアPCB配線は、差動(等しく反対の)信号をプリント基板上で運ぶことができるバランスの取れた伝送システムを作成するために使用される設計技術です。通常、この差動配線は、コネクタやケーブルなどの外部差動伝送システムに接続されます。

重要な点として、ツイストペア差動ケーブルで達成される結合比が99%以上である場合でも、差動ペア配線で達成される結合は通常50%未満であることに注意する必要があります。現在の専門家の意見では、PCB配線のタスクは特定の差動インピーダンスを達成しようとするのではなく、外部ケーブリングからターゲットコンポーネントまで差動信号が良好な状態で到着することを確実にすることに焦点を当てるべきだとされています。

業界で著名な高速PCB設計の専門家であるLee Ritcheyによると、成功した差動信号伝送には以下が必要です:

- 受信側の差動ケーブルインピーダンスの半分に各配線信号のインピーダンスを設定する。

- 2つの信号線がそれぞれの特性インピーダンスで受信側で適切に終端されていること。

- 2本の線は、設計に使用されるロジックファミリーと回路の周波数の許容範囲内で等しい長さであるべきです。タイミングを保持することに焦点を当て、設計のスキューバジェットを満たすのに十分なほど長さを合わせます。例えば、高速USBの場合、長さの不一致は150ミルを超えてはならず、DDR2クロックは25ミル以内に合わせる必要があります。

- 2つの信号を並行して配線する利点を利用して、一致した長さの良質な配線を実現します。必要に応じて、障害物を避けるために分離して配線することが許容されます。

- 信号インピーダンスが維持される限り、レイヤーの変更は許容されます。

回路図からPCBエディタへの差動ペアの転送

回路図で差動ペアの指示をネットに配置した場合、デフォルトのプロジェクトオプション設定により、PCB上に差動ペアメンバーが作成されます。PCBプロジェクトのオプションダイアログで、この設定を構成するために使用されるオプションは次のとおりです:

- コンパレータタブ - 追加の差動ペア(その後、異なる差動ペアが後続の更新をチェックし、デザインルールを作成/変更している場合はルールオプション)

- ECO生成タブ - 差動ペアの追加(その後、差動ペアの変更が後続の更新をチェックし、デザインルールを作成/変更している場合はルールオプション)

- クラス生成タブ - ネットクラスの生成(PCB差動ペア配線ルールの範囲を定義するために使用するネットクラスを作成している場合)

PCB上の差動ペアの表示と管理

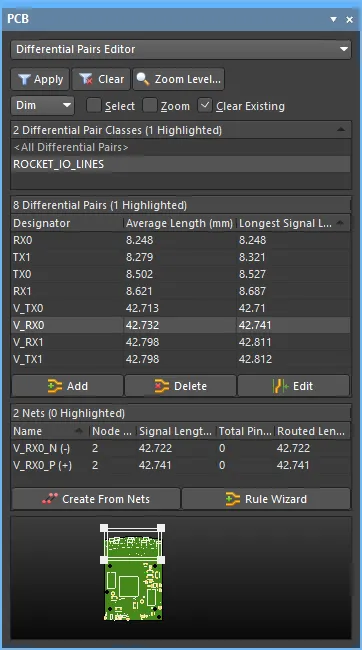

差動ペアの定義は、PCBパネルを差動ペアエディタモードに設定して表示および管理されます。下の画像は、差動ペアクラスROCKET_IO_LINESに属するペアを示しています。ペアV_RX0が強調表示されており、このペアのネットはV_RX0_NとV_RX0_Pです。各メンバーのネット名の隣に表示される-および+は、ペアの正または負のメンバーであるかを示すシステムフラグです。

差動ペアは差動ペアエディターで表示および管理できます。差動ペアクラス領域で右クリックして新しいクラスを作成します。

PCBパネルの差動ペアエディターモードでは、現在のPCB設計の差動ペア階層を反映するために、その3つの主要な領域が変更されます(上から順に):

- 差動ペアクラス。

- クラス内の個々のメンバー差動ペア。

- 差動ペアを形成する構成要素のネット(ネガティブおよびポジティブ)。

差動ペアクラスの定義

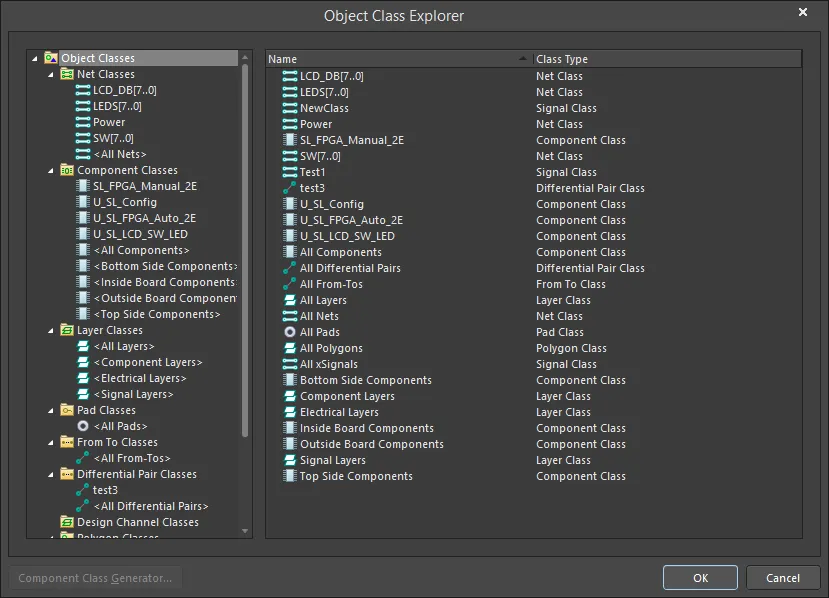

設計ルールによって対象とされる必要がある差動ペアが複数ある場合がよくあります。このような状況では、差動ペアのクラスを定義し、それらを論理的なグループにクラスタリングすることができます。差動ペアクラスエントリを右クリックしてプロパティを選択するか(またはエントリを直接ダブルクリックすると)、オブジェクトクラス編集ダイアログが開き、クラスの差動ペアメンバーシップの名前を変更したり、表示/修正したりすることができます。すべてのクラス、差動ペアクラスを含む、完全な制御と編集のためには、メインメニューから設計 » クラス コマンドを使用してオブジェクトクラスエクスプローラーダイアログを開きます。

オブジェクトクラスエクスプローラーは、差動ペアを含むすべてのクラスの作成、表示、および変更を可能にします。

差動ペアの管理

差動ペアは、回路図上で定義することも、PCBエディター内で定義することもできます。後者での管理は、差動ペアエリアのPCBパネルが差動ペアエディターモードに設定されている場合に行われます。特定の差動ペアクラスが選択されると、そのクラスに属する現在定義されているすべての差動ペアオブジェクトが差動ペアエリアにリストされます。

以下のボタンを使用して、必要に応じて差動ペアを管理してください:

- 新しい差動ペアオブジェクトを作成するには、追加ボタンをクリックします。差動ペアダイアログで、正と負のネットの既存のネットを選択し、ペアに名前を付けてからOKをクリックします。

選択可能なネットのみがリストに表示されることに注意してください。既存の差動ペアの一部として定義されているネットはリストに表示されません。

名前付きネットから迅速にペアを作成します。

名前付きネットから迅速にペアを作成します。

- 既存の差動ペアを変更するには、そのエントリを選択して編集ボタンをクリックします。差動ペアダイアログが開き、ペアに選択された現在のネットがポジティブネットおよびネガティブネットのドロップダウンフィールドに入力されます。ペアのネットを1つまたは両方変更するか、必要に応じてペアの名前を変更します。

差動ペアエントリー上で右クリックし、プロパティを選択するか、エントリーを直接ダブルクリックすることもできます。

- 既存の差動ペアを削除するには、そのエントリーを選択し、削除ボタンをクリックします。

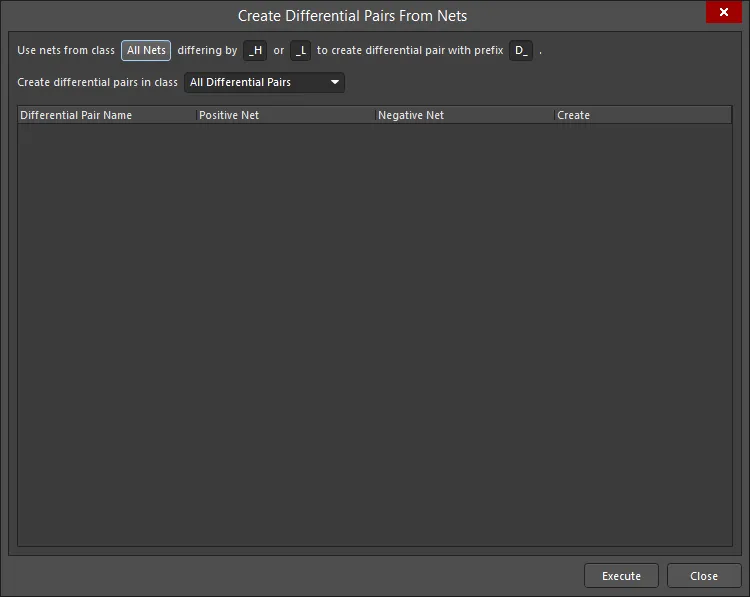

設計ネットからの差動ペアの作成

一貫した命名規則を持つネットをペアリングする場合(例えば、共通のプレフィックスと一貫した正/負のサフィックスを持つ、TX0_P と TX0_N のように)、ネットから差動ペアを作成ダイアログを使用できます。差動ペアエディタモードのPCBパネルでネットから作成ボタンをクリックしてダイアログを開きます。

ダイアログの上部にあるフィルターエントリーに応答して、作成する予定の差動ペアオブジェクトがリストされています。

この自動化された方法の効果は、差動ペアを構成する特定のネットに使用されている命名規則に直接依存します。理想的には、共通のルートに一貫した正/負の指標(`P` と `N`)が続く命名規則が使用されます。例えば、設計内の差動信号である受信信号 `D_ETH_O.RX` を考えてみましょう。この信号を構成する2つのネットは `ETH_O.RX_P` と `ETH_O.RX_N` です - これらはそれぞれ信号の正と負の側を表します。

ダイアログの上部にあるフィルターを使用すると、ネットクラスと、正と負のネットを区別するために使用された特定の差別化要因の観点から、これらのネットを迅速に対象とすることができます。たとえば、_P と _N です。差動ペアオブジェクトに追加されるプレフィックスを定義したり、どの差動ペアクラスに追加されるかを決定することもできます。

各差動ペアオブジェクトについて、ダイアログはその構成要素である正と負のネットをリストします。デフォルトでは、すべての見込み差動ペアオブジェクトが作成用に選択されており、関連する作成チェックボックスをクリアすることで個々のものを除外できます。

すべてのオプションが必要に応じて設定されたら、実行ボタンをクリックします。差動ペアオブジェクトが作成され、PCBパネルがそれに応じて更新されます。

- PCBパネルでネットのエントリを右クリックしてプロパティを選択するか(またはエントリを直接ダブルクリックすると)、必要に応じてネットのプロパティを表示/変更できるネット編集ダイアログが開きます。

- ルールウィザードボタンを使用して、差動ペアルールウィザードにアクセスし、自動化されたプロセスで差動ペアルールのプロパティを実装します。差動ペアルールウィザードを使用してルールを定義するセクションを参照して、詳細を学びましょう。

差動ペアとxSignalsの使用

メインページ: xSignalsを使用した高速信号経路の定義

差動ペアにシリーズコンポーネントが信号経路上にある場合、xSignalsを作成することが有益かもしれません。xSignalは、二つのノード間の設計者が定義した信号経路です。これらは同じネット内の二つのノードであることも、異なるネットの二つのノードであることもあります。xSignalを使用すると、シリーズコンポーネントの両側にあるネットを含むように信号経路を定義できます。xSignalsのルート長計算には、xSignalsモードのPCBパネルでxSignalが選択されたときに表示される細い線によって示されるように、シリーズコンポーネントを通る経路の長さが含まれます。

これらの差動ペアはxSignalsとして定義されており、ルート長には直列コンポーネントが含まれます。

これらの差動ペアはxSignalsとして定義されており、ルート長には直列コンポーネントが含まれます。

xSignalsは、マッチング長および長さのルールを含む設計ルールの範囲を定義するために使用できます。

► xSignalsを使用して高速信号パスを定義する方法についてもっと学ぶ こちら

適用可能な設計ルール

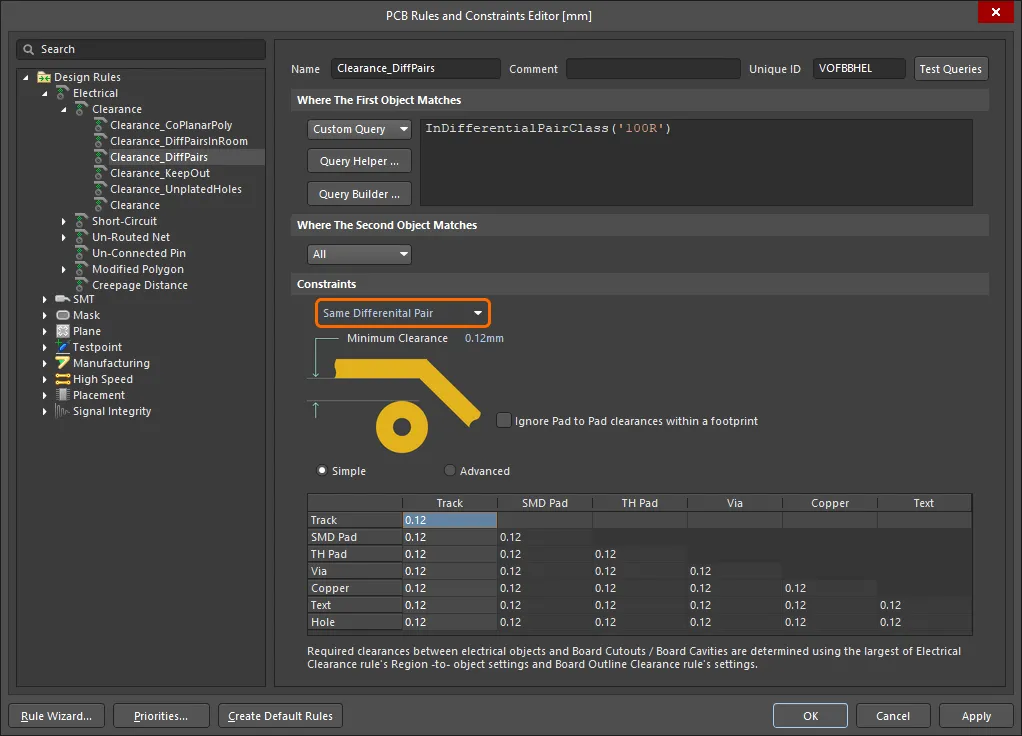

対話的に差動ペアを配線するには、以下の2つの設計ルールを作成し、設定します。PCBルールと制約エディタダイアログ(設計 » ルール)で行います。

- 差動ペアの配線 - ペア内のネットの配線幅、ペア内のネット間の隔たり(ギャップ)、および全体の非結合長(ギャップが最大ギャップ設定よりも広い場合、ペアは非結合になります)を定義します。このルールの範囲を差動ペアである対象オブジェクトに設定します。例えば、

IsDifferentialPair や InDifferentialPairClass('全ての差動ペア')です。最小/推奨/最大ギャップ設定は配線中に使用できますが、設計ルールチェック中には使用できないことに注意してください。設計ルールチェック中には、ペア内のネット間の距離は、下記のハイライトボックスで説明されているように、適用される電気的クリアランス設計ルールによってテストされます。

- 電気的クリアランス - 任意のネット、同じネット、または異なるネット上の任意の2つのプリミティブオブジェクト(例:パッド間、トラック-パッド)間の最小クリアランスを定義します。このルールの範囲を、例えば、

InDifferentialPairのメンバーであるオブジェクトを対象として設定し、以下に示すように、ダイアログの制約領域で適切なオブジェクトタイプを選択します。

重要な注意: 差動ペアを配線する際、ペア内の配線されたネットは、適用される差動ペア配線設計ルールで定義された現在の最小/推奨/最大 ギャップ設定によって分離されます(配線中にギャップモードを切り替えるにはShift+6を押し、どのモードが適用されているかをステータスバーで確認してください)。しかし、設計ルールチェック中には、すべての電気オブジェクトが適用される電気クリアランス設計ルールを使用してテストされるため、差動ペアの配線に使用されたギャップ値が、電気クリアランス設計ルールによって設定された差動ペアネット間の最小許容クリアランスよりも小さい場合、電気クリアランス設計ルールの違反が発生します。ペア内のネットが適用される電気クリアランス設計ルールによって許可される最小設定よりも近くに配置されている場合は、差動ペアに等しいクリアランスを許可する追加の電気クリアランス設計ルールを追加する必要があります。このルールには、テストされるべきネットタイプが同じ差動ペアに設定されていることも定義されている必要があります。この設定は、 ![]() この画像に示されています。

この画像に示されています。

設計ルールの範囲設定

設計ルールの範囲は、ルールを適用したいオブジェクトのセットを定義します。差動ペアはオブジェクトの一つであるため、以下の例のようなクエリを使用できます:

- InAnyDifferentialPair - 任意の差動ペア内のオブジェクトです。

- InDifferentialPair('D_V_TX1') - 名前が

D_V_TX1である差動ペアの両方のネットを対象とします。

- InDifferentialPairClass('ROCKET_IO_LINES') -

ROCKET_IO_LINESと呼ばれる差動ペアクラスに属するすべてのペアのすべてのネットを対象とします。

- (IsDifferentialPair And (Name = 'D_V_TX1')) - 名前が

D_V_TX1である差動ペアオブジェクトを対象とします。

- (IsDifferentialPair And (Name Like 'D*')) - 名前が

Dで始まるすべての差動ペアオブジェクトを対象とします。

差動ペアルールウィザードを使用してルールを定義する

ルールはPCBルールと制約エディタ(設計 » ルール)を使用して手動で作成できますが、差動ペアエディタモードのPCBパネルは差動ペアルールウィザードの便利さを提供します。ルールウィザードボタン(PCBパネルのネット領域の下)を使用してウィザードにアクセスし、必要に応じてルールのプロパティを実装します。

ルール定義プロセスをガイドする差動ペアルールウィザード。

ルールの範囲は、ウィザードを起動する前にPCBパネルでの選択に依存することに注意してください。以下の通りです:

差動ペアクラス

全ての差動ペアクラスが選択されている場合、各ルールの範囲は全てになります。

特定の差動ペアクラスが選択された場合、各ルールに対する範囲はInDifferentialPairClass('ClassName')になります。

差動ペア

パネルで単一の差動ペアオブジェクトが選択された場合、範囲は以下の通りです:

- 幅 -

InDifferentialPair('PairName')

- マッチングされたネット長さと差動ペアの配線 -

IsDifferentialPair And (Name = 'PairName'))

パネルで複数の差動ペアオブジェクトが選択されている場合、各ペアオブジェクトごとに個別の範囲項目があり、それぞれが「Or」演算子で区切られます。例えば、個別に選択された差動ペアオブジェクトD_ETH_O.TXとD_ETH_O.RXを対象とする配線幅ルールの範囲は以下のようになります:

InDifferentialPair('D_ETH_O.TX') Or InDifferentialPair('D_ETH_O.RX')

差動ペア内のネットと、ペアの一部ではない他の電気オブジェクトとのクリアランスは、適用されるクリアランスルールによって監視されることに注意してください。

差動ペアの配線

関連ページ: インタラクティブ配線

差動ペアはペアとして配線されます - つまり、2つのネットを同時に配線します。差動ペアを配線するには、ルートメニューまたはアクティブバーからインタラクティブ差動ペア配線を選択します。ペア内のネットの1つを選択するように求められます。どちらかをクリックして配線を開始します。ペア内の正または負のトレースが選択されても、システムが自動的にもう一方のトレースも選択するため、どちらを選択しても問題ありません。以下のビデオは、差動ペアが配線されている様子を示しています。

差動ペア配線中に、以下の機能を実行できます:

- Shift+R を押して、競合解決配線モード(回避、押し込み、抱きつきと押し込み、最初の障害物で停止、障害物を無視)を切り替えます。

- Shift+Spacebar を押して、利用可能なコーナースタイル(45度コーナー、コーナー内の45度円弧、任意の角度、90度コーナー、コーナー内の90度円弧)を切り替えます。

- 任意の角度のコーナースタイルを使用して差動ペアを配線する場合、Shiftを押し続けると、接線円弧を使用して差動ペアを配線します。

- Spacebar を押して、2つのコーナー方向のサブモード間を切り替えます。

- 最後の頂点を削除するには、Backspace キーを押します。

- 3 を押して、可能な差動ペアの配線幅(ユーザー選択、ルール最小、ルール推奨、ルール最大)を切り替えます。

- Shift+6 を押して、可能な差動ペアのギャップ(ルール最小、ルール推奨、ルール最大)を切り替えます。

- 数値キーパッドの + および - キーを使用して、配線レイヤーを切り替えます。

- レイヤーを切り替えてビアを挿入するには、数値キーパッドの * キーを押すか、Ctrl+Shift+Wheel Scroll のショートカット組み合わせを使用します。その後

- 4 を押して、可能なビアサイズ(ユーザー選択、ルール最小、ルール推奨、ルール最大)を切り替えます

- 5 を押して、レイヤー変更時の可能なビアパターンを切り替えます

- 6 を押して、可能なビアスタックを切り替えるか、8 を押して選択するためのリストを表示します(インタラクティブ配線中に配置されるビアを制御する方法について詳しくは、こちらを参照してください)

- Shift+F1 を押して、利用可能なコマンド内ショートカットをすべて表示します。

- コーナー内の円弧モードでは、"," キーを押して最大円弧半径を減らし、"." キーを押して最大円弧半径を増やします。円弧サイズはカーソルを動かすことでインタラクティブに変更できます。この設定は、配線時にステータスバーに表示される許容される最大円弧半径を定義します。

- インタラクティブ差動ペア配線ツールを使用する際には、差動ペアの結合が優先されることに注意してください。そのため、SMD To CornerおよびSMD Entryの設計ルールは期待通りに機能しない場合があります。差動ペアの配線時にこれらのルールを厳格に遵守する必要がある場合は、クイック差動ペア配線ツールを使用してください。

- 任意角度の差動ペア配線の現在の主な制限事項は以下の通りです:

- 異なる設計ルールを持つ部屋の境界を通る配線の遷移は現在サポートされていません。

- SMD Entryの設計ルールは現在サポートされていません。

- 自動ループ除去は現在サポートされていません。

多くの設定、例えば現在の配線モード、幅、ギャップ、ビアサイズなどは、ステータスバー(下記参照)またはヘッズアップディスプレイに表示されます(

Shift+Hでオン/オフ切り替え)。

差動ペア配線の多くの振る舞いは、シングルネットインタラクティブ配線と同じです。 ►

インタラクティブ配線についてもっと学ぶ

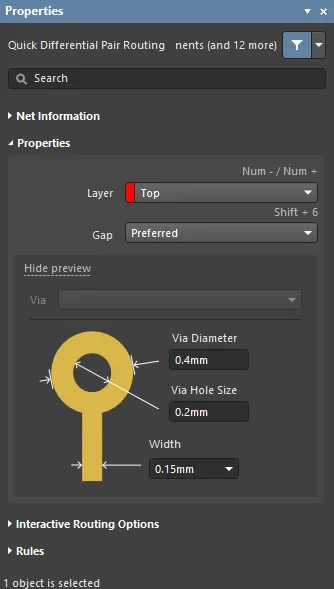

インタラクティブ差動ペアルーターの設定

インタラクティブ差動ペア配線の設定の多くは、プロパティパネルのインタラクティブ差動ペア配線モードで、インタラクティブ差動ペア配線中に変更することができます。配線中にTabを押すと、パネルが表示されます。

差動ペアのメンバーを認識するために、カップリングの概念が使用されます。ソフトウェアが差動ペアに属するオブジェクトを認識すると、プロパティパネルのインタラクティブスライディングまたはインタラクティブビアドラッグモード(以下で説明)でカップル維持オプションが有効になっている場合、ペアのパートナートラックやビアをドラッグしようとします。

次の折りたたみセクションには、利用可能なオプションとコントロールに関する情報が含まれています:

ネット情報

- DP名 – 差動ペアの名前を表示します。

- DPクラス – 配線が属する差動ペアクラスを表示します(差動ペアクラスのメンバーである場合)。

- 選択

- 長さ – 選択されたセグメントの総長さの合計。

- 遅延 – 未配線を含む選択されたセグメントの総遅延。

- 合計

- 長さ – 総信号長。 信号長は、ノード間の総距離の正確な計算です。配置されたオブジェクトは、重なっているまたは積み重なっているオブジェクトとパッド内の迷走パスを解析し、ビアの長さも含まれます。ネットが完全に配線されていない場合は、接続線のマンハッタン(X + Y)長も含まれます。

- 遅延 – 総長の配線されたセグメントの遅延。

DP名、

DPクラス、

長さ、および

遅延のクリック可能なリンクを

差動ペア配線モードの

プロパティパネルから選択して、

PCB – ネットパネルにリダイレクトされます。ここで、関連するネットの詳細を表示および変更できます。

ルール

適用可能な設計ルールによって定義された制約は、プロパティパネルのルールセクションにリストされます。

- ビア制約 – PCBルール編集ダイアログを開き、ビアのためのPCBルールを定義できます。

- 差動ペア制約 – PCBルール編集ダイアログを開き、差動ペアのためのPCBルールを定義できます。

配線品質の向上

メイン記事: 既存ルートのグロッシングと再トレース

PCBエディタには、既存の配線の品質を向上させるための強力なツールが含まれています。これらのツールはグロッシングと再トレースとして知られており、どちらもルートメニューで利用可能です。

前のセクションのアニメーション、差動ペアの配線には、グロスエフォート(配線済み)をStrongに設定した簡単なグロッシングのデモンストレーションが含まれています。

差動ペア配線のインタラクティブな変更

メイン記事: 既存のルートの変更

配線中に、既存の配線の一部を変更する必要がある場合が多くあります。たとえば、パッド出口に満足できず、パッドの形状を変更したい場合などです(下のビデオを参照)。トラック セグメントをクリックしてドラッグする製図タイプの方法を使用して既存の経路を変更できますが、多くの場合、単に経路を変更する方が簡単です。

これを行うには、Route » Interactive Differential Pair Routing コマンドを選択し、既存の配線上の任意の場所をクリックします。新しいパスを配線し、必要に応じて既存の配線に戻ってきます。これにより、古いパスと新しいパスの間にループが作成されます。右クリックまたは Esc を押して配線を終了すると、冗長なセグメントや冗長なビアが自動的に削除されます。

ループ除去機能は、

ループを自動的に削除オプションを有効にすることで使用されます。これは、インタラクティブ差動ペア配線モード中に

プロパティパネルから、または

PCBエディタ - インタラクティブ配線ページの

設定ダイアログから有効にできます。配線中にこの機能をオンまたはオフに切り替えるには、

Shift+Dキーボードショートカットを使用します。

差動ペア配線は、単一ネット配線とは少し異なります。単一ネット配線は、最後のセグメントを中空(先読みセグメント)に設定でき、クリック時には配置されません。差動ペア配線には先読みセグメントが含まれていないため、クリックすると見えるすべてのセグメントが配置されます。余分なセグメントがないようにカーソルを位置づけてください。

差動ペアを手動でトラックセグメントをドラッグして調整する場合、一方のペアメンバーをもう一方で押すか、それぞれを独立してドラッグすることができます。

ループ除去機能を使用して、差動ペアを新しいパスに沿ってインタラクティブに再配線し、古い配線ループは自動的に削除されます。ペアは、一方のルートをドラッグして他方を押すことによっても変更できます。

詳細については、既存のルートの変更を参照してください。

インタラクティブなビアのドラッグ

PCB設計者は、遅れた設計変更のためや、設計を完成させるために、配線の調整に多くの時間を費やすことがあります。これには、既存の配線を押したり引いたり、ビアをドラッグしたり、コンポーネントを微調整したりすることが含まれます。

プロパティパネルでビアのドラッグ動作を調整します。

プロパティパネルでビアのドラッグ動作を調整します。

隣接ルートのグロッシングをサポートすることに加えて、ドラッグによるビアの操作もサポートされています。ドラッグによるビア操作は、PCBエディタのプロパティパネルのインタラクティブビアドラッグモードを通じて設定された隣接グロッシングをサポートします。ビアをドラッグ中にTabキーを押すと、パネルにアクセスして設定を調整できます。

差動ペアのドラッグ

差動ペアのメンバーを認識するために、カップリングの概念が使用されます。ソフトウェアが差動ペアに属するオブジェクトを認識すると、プロパティパネルのインタラクティブスライディングまたはインタラクティブビアドラッグモードでカップル維持オプションが有効になっている場合、ペアのパートナートラックまたはビアをドラッグしようとします。

ビアペアをドラッグする際にXキーを押すと、ペアが90度回転します。

パートナーオブジェクトが結合していることを確認するために、ソフトウェアは以下のオブジェクトをチェックします:

利用可能なクリアランスの表示

配線中に、なぜその隙間を通過できないのかと悩んだことはありませんか?このフラストレーションは、差動ペア配線中にさらに発生しやすいです。Altium Designerには、この問題を解決するための機能が含まれています。それはクリアランス境界の動的表示と呼ばれます。有効にすると、既存のオブジェクト + 適用可能なクリアランスルールによって定義された禁止クリアランスエリアが、下のビデオに示されているように、ローカルビューイングサークル内でシェーディングされたポリゴンとして表示されます。Ctrl+Wを押して、機能のオン/オフを切り替えます。

差動ペア配線中にクリアランスの境界を動的に表示します。

差動ペア配線中にクリアランスの境界を動的に表示します。

表示領域は、現在のカーソル位置の周囲の領域に制限することも、画面全体にすることもできます。これは、PreferencesダイアログのPCBエディタ - インタラクティブ配線ページのクリアランス表示エリアの縮小サブオプションで制御されます。

クイック差動ペア配線ツール

メインメニューとアクティブバーからアクセスできるクイック差動ペア配線コマンドは、設定や機能が少なく、よりシンプルな設計に適した軽量な配線を提供します。その一般的な動作とショートカットは、標準のインタラクティブ差動ペア配線コマンドと同じです。

機能には以下が含まれます:

- 最初の障害物で停止する、迂回する、押し出すなど、さまざまな配線モードがあります。

- トラックの角度と直交性を維持する強力なドラッグ機能。

- 再配線を迅速かつ簡単にするループ除去機能。

クイック差動ペア配線ツールは、カーソルのパスに沿ってルートセクションを配置、シングルクリックでの配線完了、障害物の押し込みや迂回、既存の接続に自動的に従うなど、直感的な方法で配線の効率と柔軟性を最大化します。これらはすべて、適用可能な設計ルールに従って行われます。

このルーターは、機能セットが削減されているためQuickと呼ばれています。Quick Differential Pair Routerに含まれていない機能には以下のものがあります:

- ターンスムージングなし

- 任意の角度の配線をほとんどサポートしない

- T字路の押さえ込みなし

- 簡単な押し出しのサポート

- マイター比、最小アーク、またはパッド進入安定性なし

- 簡単なグロスエフォート(グロスネイバーのサポートなし)

- スタート・ピンを横方向に出るときの差動ペアの収束なし

- 配線された差動ペアによるハグなし

- ネイバー差動ペアがプッシュされたときの差動ペアのメンテナンスなし

これらの機能が必要な場合は、インタラクティブ差動ペア配線ツールを使用してください。

以下の折りたたみ可能なセクションには、クイック差動ペア配線のオプションとコントロールに関する情報が含まれています:

差動ペアのメンバーを認識するために、カップリングの概念が使用されます。ソフトウェアが差動ペアに属するオブジェクトを認識すると、プロパティパネルのインタラクティブスライディングまたはインタラクティブビアドラッグモードでカップル維持オプションが有効になっている場合、ペアのパートナートラックまたはビアをドラッグしようとします。

ネット情報

- DP名 – 差動ペアの名前を表示します。

- DPクラス – 配線が属する差動ペアクラスを表示します(差動ペアクラスのメンバーである場合)。

- 選択

- 長さ – 選択されたセグメントの総長さ。

- 遅延 – 未配線を含む選択されたセグメントの総遅延。

- 合計

- 長さ – 総信号長です。信号長は、ノード間の総距離を正確に計算したものです。配置されたオブジェクトは、重なっているか重複しているオブジェクトとパッド内の迷走パスを解析し、ビアの長さも含まれます。ネットが完全に配線されていない場合は、接続線のマンハッタン(X + Y)長も含まれます。

- 遅延 – 総長の配線されたセグメントの遅延。

DP名、

DPクラス、

長さ、および

遅延のクリック可能なリンクを

差動ペア配線モードの

プロパティパネルから選択して、

PCB – ネットパネルにリダイレクトされ、関連するネットの詳細を表示および変更できます。

プロパティ

- レイヤー – ドロップダウンを使用して、配線が配置されているレイヤーを指定します。

- ギャップ – ドロップダウンまたはShift+6のショートカットを使用して、許容されるクリアランスを切り替えます。

- 最小 – 同じ差動ペア内の異なるネット上のプリミティブ間の最小許容クリアランスを指定するために選択します。

- 推奨 – 同じ差動ペア内の異なるネット上のプリミティブ間の推奨クリアランスを指定するために選択します。

- 最大 – 同じ差動ペア内の異なるネット上のプリミティブ間の最大許容クリアランスを指定するために選択します。

- ビア – ビアがテンプレートに関連付けられている場合、ここにテンプレート名が表示されます。

- ビア直径 – ビアの直径を指定します。

- ビア穴サイズ – ビア穴のサイズを指定します。

- 幅 – ドロップダウンを使用して幅を指定します。

- 最小 – 現在のネットに定義された設計ルールの最小幅が使用されることを意味します

- 推奨 – 現在のネットに定義された設計ルールの推奨幅が使用されることを意味します。

- 最大 – 現在のネットに定義された設計ルールの最大幅が使用されることを意味します。

インタラクティブ配線オプション

- 配線モード – ドロップダウンを使用するか、Shift+Rショートカットを使用して、目的の配線モードを切り替えます。次の選択肢があります。R

障害物を無視 – 既存のオブジェクトを無視する場合に選択します (配線は自由に配置できます)。違反が強調表示されます。障害物を迂回– インタラクティブルーターが既存のトラック、パッド、ビアを迂回するように選択します。このモードで障害物を迂回できない場合、違反を引き起こさずに障害物を迂回できない場合は、ルートがブロックされていることを示すインジケーターが表示されます。障害物を押す – インタラクティブ ルーターが既存のトラックを邪魔にならないように移動する場合に選択します。このモードでは、ビアをプッシュして新しい配線に道を譲ることもできます。このモードで障害物を押すことができず、違反を発生させることができない場合は、ルートがブロックされていることを示すインジケーターが表示されます。障害物をハグして押す – インタラクティブルーターが既存のトラック、パッド、ビアをできるだけ近づけてハグし、必要に応じて障害物を押してルートを続行する場合に選択します。このモードで障害物を抱きしめたり押したりできない場合、違反を引き起こさずに障害物を押すことができない場合は、ルートがブロックされていることを示すインジケーターが表示されます。最初の障害物で停止 – このモードでは、配線 エンジンは邪魔になる最初の障害物で停止します。現在のレイヤーを自動配線 – 現在のレイヤーでのみ自動配線を有効にする場合に選択します。- 複数のレイヤーを自動配線 – 複数のレイヤーで自動配線を有効にする場合に選択します。

- コーナースタイル – 目的の配線コーナースタイルを選択するか、Shift+Spacebarのショートカットを使用してコーナースタイルを切り替えます。

- 90/45 に制限 – 配線を 90 度と 45 度のみに制限できるようにします。

- ループを自動的に削除– 手動配線中に作成された冗長なループを自動的に削除します。これにより、冗長なトラックを手動で削除することなく、接続を再配線できます。ただし、電源ネットなどのネットを配線する必要がある場合や、ループが必要な場合があります。選択したネットに対してこのオプションを切り替えるには、Shift+D ショートカットを使用して、同じネットのこのグローバル設定をオーバーライドします。

- ビア付きループの削除 – ビア付きのループを自動的に削除できるようにします。このオプションを無効にすると、ループの削除中にビアが残ります。

- ネットアンテナを削除 – このオプションを有効にすると、他のプリミティブに接続されておらず、アンテナを形成しているトラックまたはアークの端が削除されます。

- クリアランス境界を表示 - このオプションを有効にすると、既存のオブジェクトによって定義された立ち入り禁止のクリアランス領域と、適用可能なクリアランスルールが、ローカルビューサークル内のシェーディングされたポリゴンとして表示されます。このオプションは、障害物を無視配線モードでは使用できません

- クリアランス表示領域を縮小 – このオプションを有効にすると、より小さなクリアランス境界が使用されます。このオプションは、クリアランス境界を表示オプションが有効な場合にのみ使用できます。

差動ペアの長さのマッチング

差動ペアは、本質的なノイズ耐性と、信号の高品質なリターンパスを提供する課題を簡素化することから、高速設計でよく使用されます。しかし、片側信号と同様に、信号タイミング要件を満たすためには、その長さを管理する必要があります。

差動ペアの配線中に、ペア内の2つのネットのそれぞれの長さがステータスバーに表示され、ヘッズアップディスプレイ(Shift+Hでオン/オフ切り替え)にも表示されます。ペアの配線を終了したときに、PCBパネルに表示される長さの値が更新されます。

ペア内の各ネットの現在のルート長は、ヘッズアップディスプレイに表示されます(オン/オフを切り替えるにはShift+H)。

ペア内の各ネットの現在のルート長は、ヘッズアップディスプレイに表示されます(オン/オフを切り替えるにはShift+H)。

PCBパネルは、設計空間内のオブジェクトを調査するために使用され、ネット、差動ペア、xSignalsなど、他にも様々なモードを含んでいます。このパネルには、各ネット/差動ペア/xSignalの詳細が含まれており、信号長や遅延などの情報があります - パネルの各セクションで右クリックすると、そのセクションのコマンドのコンテキストメニューが表示されます。例えば、パネルがネットモードの場合、パネルのネットセクションで右クリックし、列サブメニューを使用して信号長や遅延などの詳細を有効または無効にします。長さやマッチングされた長さのルールが適用されている場合、設計ルールに違反するネットの信号長列は、目標長さより短い場合はオレンジ色で、目標長さを超える場合は赤色でハイライトされます。

PCBパネルを使用して長さマッチングの進行状況を監視する。

PCBパネルを使用して長さマッチングの進行状況を監視する。

► PCBパネルについてもっと学ぶ

一致した長さと長さの設計ルール

長さと一致した長さの設計ルールは、フライトタイムとスキューのタイミング要件が満たされるように定義することができます。これらのルールは、設計ルールチェック(DRC)中だけでなく、インタラクティブな長さ調整中にも使用されます。

一致した長さの設計ルールは、ルールの範囲によって対象とされる最長のペアを検出し、そのペアの平均長さ値を参照として使用して、他の対象ペアがルールで定義された許容範囲内であることを要求します。この平均長さ値は、PCBパネルの差動ペアエディタモードで表示されます。

長さの単位または遅延の単位で範囲できる長さおよびマッチングされた長さの設計ルールがあります。遅延によってルールが範囲される場合、長さ調整ゲージも遅延を使用して表示されます。

ペア内およびペア間の設計ルール

ペア間、および各ペア内でマッチングされた長さの要件がある可能性が高いです。

これを管理するには、適切なマッチングされた長さの設計ルールを作成します:

差動ペア間、またはこの例ではxSignals間の長さ要件を定義するためのマッチした長さのルールを作成します。

差動ペア間、またはこの例ではxSignals間の長さ要件を定義するためのマッチした長さのルールを作成します。

ペア内の長さ要件を定義するために、2番目のマッチした長さのルールを作成します。

ペア内の長さ要件を定義するために、2番目のマッチした長さのルールを作成します。

差動ペアの長さ調整

メイン記事: 長さ調整

ペアの長さ、および各ペア内のネットは、2つの長さ調整コマンドを使用して調整されます。長さを調整するには:

- 差動ペアの長さは、ルートメニューのインタラクティブ差分ペアの長さ調整コマンドを使用して正確に調整できます。長さのチューニング中に、ショートカットを使用してアコーディオンのスタイルとサイズをインタラクティブに調整したり、Tabキーを押して差動ペアの長さチューニングモードでプロパティパネルを開いたりできます。パネルでは、ターゲットの長さが定義されます。

- ペア内のネットを調整するには、配線メニューのインタラクティブ長さ調整コマンドを使用します。ペアの長い方のネットを調整しようとすると、「Target Length Shorter than Old Length」というメッセージが表示されます。

まず差動ペアの長さを調整し、次にペア内の短いネットの長さを調整します。

まず差動ペアの長さを調整し、次にペア内の短いネットの長さを調整します。

長さの調整中にアコーディオンが表示されない場合、現在の設定がアコーディオンを配置するための利用可能なスペースに適していない可能性が高いです。このような状況が発生した場合は、

Tabキーを押して

差動ペア長さ調整モードで

プロパティパネルを開き、パネルの

パターンセクションの設定が適切であることを確認してください。例えば:

- 最大振幅の値が大きすぎる可能性があります

- スタイルがマイター付き円弧の場合、マイタ(Miter)のパーセンテージが大きすぎて、現在の振幅と空間の円弧を形成できない場合があります

良い選択肢は、スタイルをミタードラインに設定し、一時停止ボタンをクリックして長さの調整を再開し、

1および

2のショートカットを使用して

マイターを、

3および

4のショートカットを使用して

スペース(ピッチ)を、

,および

.のショートカットを使用して

振幅を対話的に調整します。調整が希望通りの見た目になったら、好みのスタイルに切り替えるために

Spacebar 押します。

長さ調整のページを参照してください。ここでは、アコーディオンスタイル、振幅、ピッチを変更するために使用できるショートカットの詳細なリストが見つかります。また、長さと一致した長さの設計ルールにおいて重複する設定がある場合に、ソフトウェアがどのルール設定に従うかについても説明しています。

長さ調整とアコーディオンの変更のデモンストレーション

このビデオでは、xSignalの長さに基づいて他のペアと比較してペアの長さを調整するために、長さ調整アコーディオンを追加する様子が示されています。各ペアの短いメンバーは、そのペアの長いメンバーに対して長さ調整されます。次に、ペアを対話的に移動および再形成する方法、調整アコーディオンを削除する方法、配置中にショートカットを使用して新しいアコーディオンを形成する方法が示されます。

差動ペアの長さは、長さ調整アコーディオンを追加することで調整できます。アコーディオンは、移動、形状変更、削除が可能なオブジェクトです。

関連項目