部品番号は、設計内の各コンポーネントを一意の指定子を用いて個別に識別できるようにするためのプロセスです。Altium Designerはグローバルに一意なID(GUID)を使用してコンポーネントの識別を維持できますが、多くの設計者は歴史的にコンポーネントの指定子を回路図およびPCB、部品表などの出力においてコンポーネントを参照する主要な手段として使用しています。

部品番号付与には3つのアプローチがあります。部品番号付与ツールの選択は、設計のタイプ、個人の好み、会社の方針や手順など、多くの要因に依存します。

回路図レベルの部品番号付与

回路図レベルの部品番号付与は、設計の純粋に論理的なビューを使用してコンポーネントの指定子を決定します。デバイスシートを使用しない単純な設計に最も有用ですが、処理の順序を指定できるだけでなく、マルチパートコンポーネントの既存のパッケージを完成させるオプションもあるため、ボードレベルの部品番号付与に先立つ必要があります。

要約すると、回路図レベルの部品番号を使用して:

- マルチパートコンポーネントをパッケージ化する。

- 回路図設計内の位置に基づいてコンポーネントに部品番号を付ける。

- プロジェクトオプションで指定されたデフォルトの命名規則を使用して、マルチチャネル設計に部品番号を付ける。

- 追加の部品番号のために設計を準備する。

PCB部品番号

PCB部品番号は、PCB上のコンポーネントの物理的位置を使用して、その指定を決定します。これにより、位置情報をコンポーネントの指定子に効果的にエンコードでき、組み立てられたPCBのデバッグ時に非常に役立ちます。要するに、PCB設計のボード上の位置に基づいてコンポーネントに部品番号を付けるためにPCB部品番号を使用すべきです。

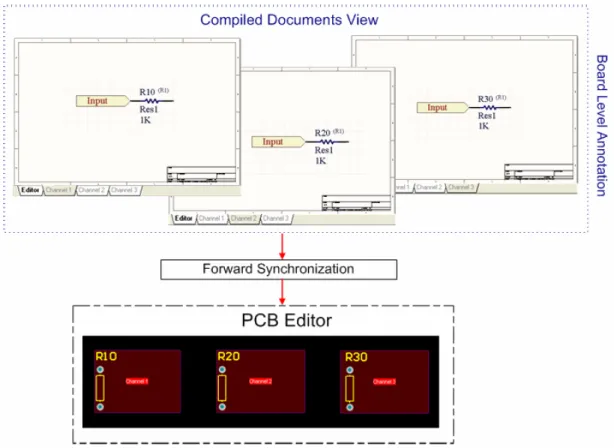

ボードレベルの部品番号

ボードレベルの部品番号は、回路図設計で使用される指定子と、PCB設計上の実際の対応物との間のマッピングを提供します。ボードレベルの部品番号はどのような設計にも使用できますが、特にマルチチャネル設計や、デバイスシート上で指定子を編集できないデバイスシートを取り入れた設計にとって非常に有用です。この方法では、元のデバイスシートを実際に変更することなく、全体の設計を再部品番号することができます。ボードレベルの部品番号は、プロジェクト全体で重複する指定子によって発生する可能性のある任意の部品番号の競合問題を解決し、その変更を*.Annotationテキストファイルに保存します。これには、命名スキームをカスタマイズするための追加のキーワードが含まれており、それらを全ての部品または選択した範囲の部品にのみ適用することができます。

要約すると、ボードレベルの部品番号を使用して:

- デバイスシートにコンパイルされたコンポーネントに部品番号を付与する。

- 部品番号、グローバルインデックス、その他の設定可能なオプションを含む命名規則を使用して、複数のチャネルにわたってすべてのコンポーネントに固有の名前を付ける。

- コンポーネントに手動で名前を付ける。

回路図の部品番号

回路図部品番号は、Annotateダイアログを使用して設定されます。このダイアログには、プロジェクトの選択されたシート内のすべてまたは選択された部品に対して、指定子を体系的に割り当てるためのコントロールが提供されており、指定子が一意であり、その位置に基づいて順序付けられることを保証します。部品番号オプションは、マルチパートコンポーネントをパッケージ化し、インデックスおよびサフィックスオプションを設定し、重複する指定子を含む回路図指定子をリセットし、PCBからバックアノテートするように構成できます。

Annotateダイアログは、Annotate Schematicsコマンド(Tools » Annotation » Annotate Schematics)を実行することでアクセスされます。

Annotate ダイアログは、Annotate Schematics コマンドから起動されます。

このダイアログは、主に2つの領域に分かれています:

- 回路図部品番号設定 - この領域では、部品番号スキームの設定および部品番号の範囲を設定します。

- 提案された変更リスト - この領域には、エンジニアリング変更命令 (ECO) を使用して受け入れられ、実行されると発生する提案された変更がリストされます。

コンポーネントのロック

非均質な複数部品コンポーネントの場合、部品番号付与中にサブパートの変更を防ぐために、プロパティパネル内のロックされたアイコンが閉じていることを確認してください。

厳格オプション

厳格チェックボックスがコンポーネントパラメータに対して有効になっている場合、すべてのコンポーネントはそのパラメータに一致してパッケージに組み込まれなければなりません。このパラメータを持たないコンポーネントは個別のコンポーネントとして部品番号され、パッケージ化されません。

以下の例は、これらのオプションがどのように組み合わさって特定の結果をもたらすかを示しています:

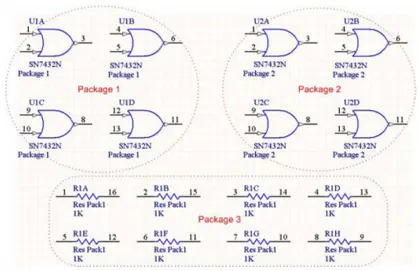

8つのORゲートと8つの抵抗器を含む設計を考えてみましょう(下の画像に示されています)。ORゲートにはQuadOrGateというパラメータが含まれており、4つのORゲートのグループがパラメータ値Package1を持ち、他の4つのORゲートのグループがパラメータ値Package2を持っています。抵抗器にはそのようなパラメータはありません。コンポーネントパラメータコントロールでQuadOrGateのチェックボックスを有効にすると、このパラメータがコンポーネントのパッケージ方法を制御するために使用されることを保証します。この場合、Strictlyのチェックボックスは有効にされていません。

Tools » Annotation » Annotate Schematicsコマンドを起動した後、パラメーターがQuadOrGate = Package1である部品は同じ物理的コンポーネントにパッケージされ、パラメーターがQuadOrGate = Package2である部品は別々に一緒にパッケージされます。 QuadOrGateパラメーターを持たない残りのコンポーネントは一緒にパッケージされます。この場合、抵抗器は共通の属性がQuadOrGateパラメーターを含まないため、一緒にパッケージされます。

Strictlyオプションがチェックされていない場合のパッケージ化されたコンポーネントの例。

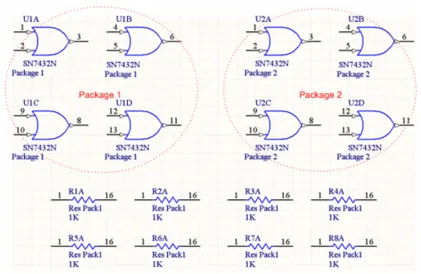

同じ設計が部品番号されているが、Strictlyオプションがチェックされている場合、QuadOrGateパラメータを持つコンポーネントのみがパッケージ化されます。この場合、ORゲートはパッケージ化されますが、抵抗器はパッケージ化されません。したがって、Strictlyオプションはパッケージ化プロセスを非常に細かく制御することができますが、ほとんどの状況ではチェックを外すことが推奨されます。

Strictlyオプションがチェックされた時のパッケージされたコンポーネントの例。

マルチパートコンポーネントは、アルファまたは数値のパート識別子サフィックスを使用できます - 例えば U1:1, U1:2, または U1:A, U1:B。サフィックスのスタイルの制御は、

Preferencesダイアログの

回路図 - 一般ページで指定されます。Preferencesはグローバルであり、現在開いているすべての回路図シートに適用されることに注意してください。

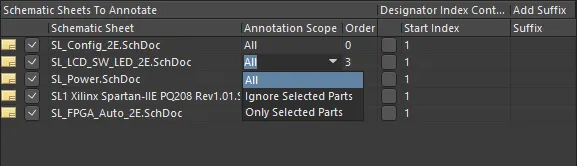

部品番号を付ける回路図シート

部品番号を適用する回路図シートとコンポーネントをどのように選択し、その変更がどのように計算されるかについて、高度な制御が提供されます。

部品番号の範囲を指定する。

- リストされた回路図シートの左側にあるチェックボックスは、部品番号付与コマンドの一部として処理されることを示します。

- 部品番号付与の範囲は、Annotation Scopeドロップダウンリストによって決定され、回路図シート全体を含むように拡張することも、選択されていないコンポーネントに限定することもできます。Ignore Selected Partsまたは Only Selected Partsオプションを使用するには、Annotationコマンドを実行する前に設計で構成部品が選択されている必要があります。

- 回路図シートに部品番号を付与する順序は、Orderフィールドを使用して構成します。フィールドに値を直接入力するか、フィールドをクリックすると表示される矢印を使用して目的の値を設定します。

- Designator Index Controlオプションが選択されている場合、指定子の値はStart Indexの値から開始されます。Start Indexは、Designator Index Controlオプションが選択されていない場合には効果がありません。

- 追加の接尾辞は、関連する接尾辞列に文字列/値を指定することによって、各指定子の末尾に追加できます。「A」や「1」などの 1 文字の接尾辞は、サブパートや他の指定子の値と混同されやすいため、使用しないでください。

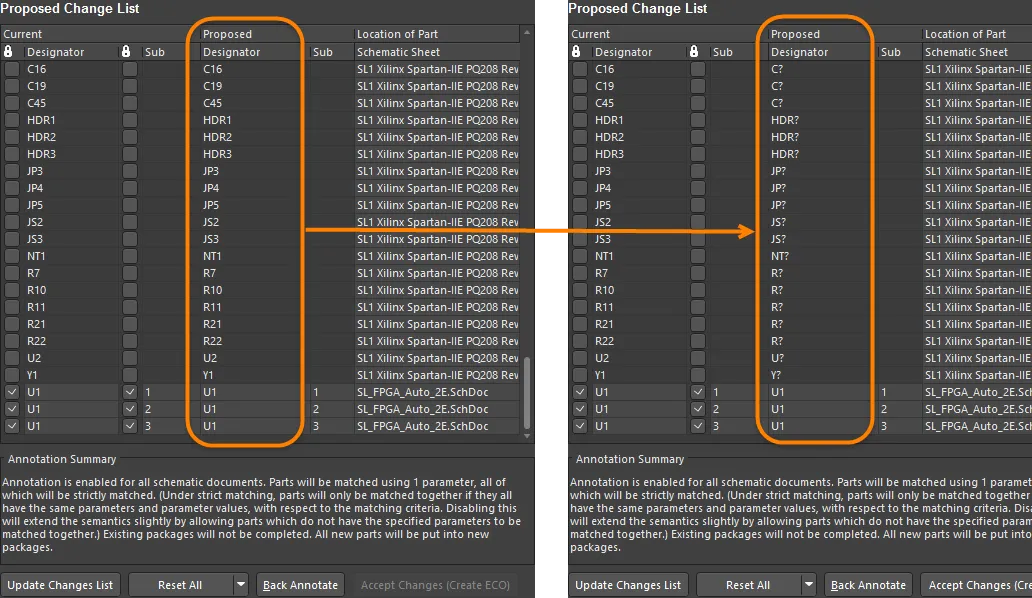

提案された変更リスト

Update Changes Listボタンをクリックして、提案された変更リストを更新し、適用される前にすべての指定子の変更を確認できます。変更されるのは以前に設定されていない指定子(例:R?、C?など)のみです。したがって、設計内のすべての指定子を更新するつもりであれば、Reset Allボタンを押して最初にリセットする必要があります。

部品番号設定を適用する前に指定子をリセットしています。

すべてリセットドロップダウンボタンは、重複リセットにも使用できます。

提案された変更リストには、部品番号が選択されたシート内に含まれる部品の指定子がすべてリストされています。各エントリーには、現在および提案された指定子の値の詳細が含まれ、コンポーネントのサブ(部品)と部品の位置が記載されています。

指定子に関連付けられたボックスをチェックすると、その特定の指定子は変更されないようにロックされます。同様に、サブボックスをチェックすると、その特定のマルチパートコンポーネントが更新されないようになります。このオプションは、プロパティパネルでロックアイコンを設定する代わりに使用できます。

提案された変更のリストを確認した後、変更を承認(ECOを作成)ボタンをクリックして、エンジニアリング変更命令ダイアログを起動します。ECOが実行されると、部品番号の変更が設計に適用されます。

追加の回路図の部品番号付与コマンド

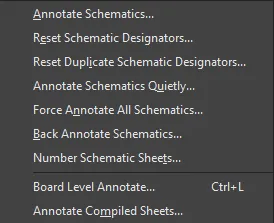

Tools » Annotation メニューには、特定の回路図部品番号コマンドがいくつか含まれています。グループの最初の項目、部品番号が付与された回路図は既に説明されています。

さまざまな部品番号付与コマンドが利用可能

回路図の指定子をリセットする

異なるソースから新しいデザインに大量のコンテンツがコピー&ペーストされた場合、すべての指定子をリセットする必要があるかもしれません。このコマンドは部品番号付与ダイアログから取得した設定を使用するため、そのダイアログ内で以前に設定された項目に適用されます。例えば、すべての部品番号付与する回路図シートが以前にチェックされていた場合、回路図指定子のリセットコマンドは、エディタで現在開かれているかどうかに関わらず、プロジェクト全体に適用されます。もし部品番号付与する回路図シートのうちいくつかだけが以前にチェックされていた場合、回路図指定子のリセットコマンドはそれらのシートにのみ影響します。

コマンドを実行すると、更新が必要な指定子の数をまとめた確認ダイアログが表示され、変更を進めるかどうかを尋ねられます。 はいをクリックすると、アクティブプロジェクトのすべての部品番号が有効な回路図シートのすべてのコンポーネント指定子がリセットされ、次の形式で表示されます:R?、C?、D?、U?など。

ロックされたステータスの指定子は、リセットされたり変更されたりしません。

重複する回路図指定子のリセット

設計の一部を複製すると、新しくコピーされたコンポーネントは、それらがコピーされたものと同じ指定値を保持します。Reset Duplicate Schematic Designatorsコマンドは、重複した指定子を「?」にリセットする迅速な方法を提供します。このコマンドはAnnotateダイアログから取得した設定を使用するため、そのダイアログ内で以前に設定された項目に適用されます。例えば、すべての部品番号を付ける回路図シートが以前にチェックされていた場合、Reset Duplicate Schematic Designatorsコマンドは、エディタで現在開かれているかどうかに関わらず、プロジェクト全体に適用されます。もし、いくつかの部品番号を付ける回路図シートのみが以前にチェックされていた場合、Reset Schematic Designatorsコマンドは、それらのシートにのみ影響します。

コマンドを実行すると、更新が必要な指定子の数をまとめた確認ダイアログが表示され、変更を進めるかどうかを尋ねられます。 はいをクリックすると、アクティブプロジェクトの部品番号が有効なすべての回路図シートにある重複するコンポーネント指定子がリセットされ、R?、C?、D?、U?などの形式で表示されます。

ロックされた状態の指定子はリセットされず、何も変更されません。

静的に回路図を部品番号付けする

Annotate Schematics Quietlyコマンドは、アクティブなプロジェクトの部品番号付与が有効になっているすべてのソース回路図ドキュメントを調査し、現在デザインが割り当てられていない任意のコンポーネントに一意のデザインを割り当てるために使用されます。部品番号付与は静的に実行されるため、アノテートダイアログの以前の設定を再度開くことなく適用することができます。これは、設計が急速な開発フェーズを経ている場合に、設計者が設計をコンパイルする前に迅速に部品番号付与を適用したい場合に特に便利です。

すべての回路図に強制部品番号付与を適用

このコマンドは、アクティブなプロジェクトの部品番号付与が有効になっているすべてのソース回路図ドキュメントを調査し、現在Annotateダイアログで定義されている部品番号付与スキームに従って、そこに含まれるすべてのコンポーネントを再部品番号付与するために使用されます。

Force Annotate All Schematicsコマンドを実行することは、Reset Schematic Designatorsコマンドを実行した直後にAnnotate Schematics Quietlyコマンドを実行することと同等です。その結果、Force Annotate All Schematicsコマンドは、どのコンポーネントとシートを更新できるかを決定する際に、以前にAnnotateダイアログ内で設定された設定を使用します。

このコマンドを起動すると、承認された場合に更新される指定子の数を詳述する確認のリクエストが表示されます。 Yesをクリックすると、アクティブプロジェクトのすべての部品番号付与が有効な回路図シートのすべてのコンポーネント指定子が、必要に応じて、AnnotateダイアログのSchematic Annotation Configuration領域で定義された現在の位置部品番号付与スキームに準拠するように再アノテートされます。

回路図のバックアノテート

Altium DesignerのDesign CompilerとSynchronizerの導入以前は、部品番号の変更はネットリスト(*.net)ファイルを介して回路図からPCBに伝達されていました。PCBから回路図へ逆方向に伝播する必要がある部品番号の変更は、バック部品番号付与プロセスを介して処理されました。このプロセスは、Was-Is (*.WAS)ファイルまたはエンジニアリング変更命令(*.ECO)ファイルを使用して、回路図の指定子に適用される変更を指示します。

このコマンドは、

Design Compilerと

Synchronizerが設計の同期を管理するためのはるかに効果的なツールであるため、大部分が余分なものとなっています。しかし、レガシー目的や、Specctra®のような代替のPCBレイアウトツールを使用する設計者にとっては依然として有用です。

Was-Isファイルの生成についてさらに学びましょう。

コマンドを起動した後、PCBからバック部品番号付与用のWAS-ISファイルを選択ダイアログが表示されます。必要な.was(または.eco)ファイルを探して選択します。開くをクリックすると、以前の状態から変更されたデザインネータの数と、元の状態から変更された数をリストアップする情報ダイアログが表示されます。この時点では、変更は実際には実装されていません。OKをクリックすると、アノテートダイアログが表示され、ECOを作成して実装する前に、現在のデザインネータに提案された変更を確認できます。

- PCB 内の指定子に再度部品番号を付与する場合、部品番号を付与するたびに、ファイル名に日付と時刻を含む固有の

.wasファイルが生成されます。これにより、複数の.wasファイルを古いものから新しいものへと連続して読み込むことができ、PCBとソース回路図シート間の指定の同期を失うことはありません。

- バックアノテートは、Annotationダイアログ内からBack Annotateボタンをクリックして直接実行することもできます。

回路図シートの番号付け

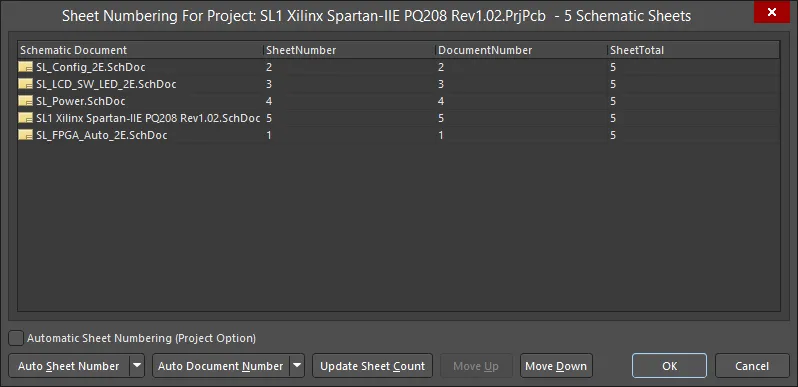

Number Schematic Sheetsコマンドは、コンポーネントの指定子ではなく、回路図シートの指定子(番号)を変更します。概念的には、これは設計アノテーションの一般的な概念に関連しています。

シートと文書の番号付けにより、シートの指定を制御し、それらを各回路図ドキュメント内のパラメータとして保存できます。Altium Designerの特別な文字列機能(=SheetNumber、=DocumentNumber、=SheetTotal)を使用すると、これらの値をシート上(例えばシートのフッターに)テキストオブジェクトとして表示できます。

回路図シートの番号付け。

シートの番号付けプロセスは以下の通りです:

自動シート番号付け(プロジェクトオプション)

自動シート番号付けを実行できます。プロジェクトパネルに値が表示されます。プロジェクトオプションダイアログのオプションタブでAutomatic Sheet Numberingオプションをチェックすることによっても、自動シート番号付けを有効にできます。

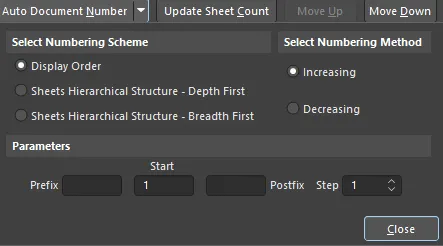

自動シート番号

Auto Sheet Numberドロップダウンボタンをクリックして、シート番号付けオプションにアクセスします。

番号付けスキームの選択オプションは以下の通りです:

- Display Order -シートには、表示されている順序で番号が付けられます。

- Sheets Hierarchical Structure - Depth First -シートには、最上位レベルから各枝に番号が付けられます。トップレベルに最初に番号が付けられ、次にトップレベルの下の最初の枝に番号が付けられ、2番目のブランチに番号が付けられます。

- Sheets Hierarchical Structure - Breadth First -シートには、階層内のレベルに応じて番号が付けられます。最上位レベルには最初に番号が付けられ、2 番目のレベルには次の番号が付けられます。

番号付け方法の選択オプションでは、増加または減少する連続値を選択できます。

自動文書番号付け

Auto Document Numberドロップダウンをクリックして、ドキュメント番号付けオプションにアクセスします。これらは基本的にAuto Sheet Numberオプションと同じですが、PrefixとPostfixの値が追加されています。

Parametersオプションは以下の通りです:

- Prefix - ドキュメント番号の前に配置するプレフィックスを選択します。英字(

A、B、Cなど)、数字(1、2、3など)、および数字以外のプレフィックス(_、*、.、%など)は、それらすべての組み合わせを含めてサポートされています。

- Start -番号付けを開始する数値を選択します。

- Postfix - 文書番号に追加する接尾辞を選択します。英字(

A、B、Cなど)、数字(1、2、3など)、数字以外の接尾辞(_、*、.、%など)の接尾辞がサポートされており、それらすべての組み合わせが含まれています。

- Step - 各ドキュメント番号をインクリメントする値を選択します。たとえば、開始インデックスが 1 に設定され、ステップ 値が 100 に設定されている場合、最初のドキュメント番号は 1 になり、次のドキュメント番号は 101 (開始 + ステップ)、次のドキュメント番号は 201 になります。

シート数の更新

Update Sheet Count ボタンをクリックして、現在のプロジェクト内のシート数を集計し、その結果を SheetTotal列に配置します。シート数は、以前のコントロールのいずれかで選択された番号付けスキームに関係なく、プロジェクト内のシートの総数になります。

上へ/下へ移動

Move UpまたはMove Downボタンを使用して、リスト内の選択された回路図ドキュメントを上または下に移動します。これは、シートまたはドキュメント番号を指定するために表示順番号付けスキームを使用する場合に関連します。

カスタム番号付け/命名

組織がAuto Sheet Numberやuto Document Numberコマンドを通じて自動化できない特定の番号や命名システムを持っている場合、カスタムシート名や番号をSheetNumberやDocumentNumberフィールドに直接記入することができます。

回路図シートの番号付けとデバイスシート

シートまたは文書番号は、デバイスシートが読み取り専用(デフォルト状態)である場合には設定できず、プロジェクトのシート番号付けダイアログでクロスハッチが表示され、更新できないことを示します。デバイスシートが編集可能として設定されると、クロスハッチが削除され、シートおよび文書の番号付けが通常どおりに設定できます。

PCB上の指定子の表示制御

マルチチャネル設計における拡張指定子文字列の配置は、PCBエディタで面倒な作業になることがあります。短い名前を結果とする命名オプションを選択するか、元の論理的なコンポーネント指定を表示することができます。例えば、C30_CIN1はC30として表示されます。これには、コンポーネントオーバーレイ上で各チャネルを囲むボックスなど、別々のチャネルを示すための別の表記をボードに追加する必要があります。

PCB上で論理的または物理的な指定子の表示を選択するには、BoardモードのPropertiesパネルのOther領域にあるDesignator Displayドロップダウンを使用します。マルチチャネル設計のコンポーネントに対して論理的な指定子を表示することを選択した場合、これらはPCBおよびプリントやガーバーなどの生成される任意の出力に表示されます。ただし、ユニークな物理的な指定子は、部品表を生成する際に常に使用されます。

設計同期 - 部品番号付与プロセスの最終化

直接設計同期は、回路図とPCBの指定子を一致させるための好ましい方法ですが、回路図とPCBエディタの両方にアクセスできない場合は除きます。設計同期は、回路図のコンポーネントと接続性を直接PCBと比較し、差異のリストを生成します。これらの差異を解決するために必要な変更のリストは、ECO(エンジニアリング変更命令)として生成されます。ECOファイルは、現在の設計と望ましい設計の違いを記述し、実行されることで、ターゲットを更新し、設計を同期状態にします。

前方同期と後方同期

Forward Synchronization(前方同期)とBack Synchronization(後方同期)という用語は、データの同期中に部品番号や設計変更が転送される方向を特定するための方法を具体的に説明しています。回路図から始まり、それによって駆動される設計フローを視覚化すると、Forward Synchronizationは回路図エディタで行われた変更をPCBに向けて更新するプロセスです。Back SynchronizationはPCBで行われた変更を回路図エディタに向けて更新するプロセスです。

前方同期

回路図からPCBへデータを同期する理由のいくつかは以下の通りです:

- 新しいコンポーネントが回路図エディタに追加され、PCBレイアウトで必要になります。

- 回路図デザインに初めて部品番号を付けたか、前回の設計同期以降に部品番号を付けた。

- マルチチャンネル デザインでProject Optionsを変更して、物理 (PCB) 命名スタイルを変更しました。

- ボード レベルの部品番号付与を初めて実行したか、前回の設計同期以降に実行しました。

回路図デザインをPCBデザインに同期させるには

回路図デザインをPCBデザインに同期させるために、以下の方法から選択してください:

- 回路図エディタのDesignメニューで Update PCB Documentを選択します。これらとターゲットPCBドキュメントの間に相違点がある場合は、Engineering Change Orderダイアログが開き、PCBを回路図デザインと同期させるために必要な修正のリストが表示されます。Execute Change をクリックして、設計を同期します。

- PCB エディタのDesignメニューのImport Changesを選択すると、回路図ドキュメントから PCB ドキュメントに変更がインポートされます。

バック同期

バック同期は、PCBデザインを部品番号付けしたり変更したりした後に、回路図デザインを更新したい場合に行います。

PCBデザインを回路図設計に同期させる方法

PCBデザインを回路図設計に同期させるための以下の方法から選択してください:

-

PCB エディタで、Designメニューの Update Schematicsを選択します。デフォルトでは、[プロジェクト オプション]ダイアログのECO Generation tabにあるPush Component Designator Changes to Annotation File (if any) オプションがオンになっているため、PCB エディタで行われた変更はアノテーション ファイルにのみプッシュされ、最終的にはコンパイル時にコンパイル済みドキュメントにプッシュされます。このオプションをオフにすると、ソース回路図ドキュメント(エディタビュー)にのみ変更がプッシュされます。

- 回路図エディタから、Tools » Annotation » Annotate Schematicsを選択し、Annotate dialogのBack Annotate ボタンをクリックします。PCB 環境で指定子に再注釈を付けるときに生成される WAS-IS ファイルを選択します。

これはレガシーツールです。設計の同期には、Design » Update Schematicsコマンドが推奨されます。

- 回路図エディタから、Tools » Annotation » Board Level Annotateを選択し、Board Level Annotate ダイアログの Back Annotateボタンをクリックします。PCB 環境で指定子に再注釈を付けるときに生成される WAS-IS ファイルを選択します。

これはレガシーツールです。設計の同期には、Design » Update Schematicsコマンドが推奨されます。

- 回路図エディタから、Tools » Annotation » Back Annotate Schematicsを選択します。PCB 環境で指定子に再注釈を付けるときに生成される WAS-IS ファイルを選択します。

これはレガシーツールです。設計の同期には、Design » Update Schematicsコマンドです。

回路図のバックアノテートは、PCBエディタで行われた部品番号付与変更を回路図設計と同期させる機能です。この機能は、PCBと回路図エディタを同時に開くことができない場合に便利です。例えば、PCBと回路図が異なる場所の人々によって設計されている場合などです。

設計同期の従来の方法

Altium Designerは、デザイン同期のために従来の中間ファイル(ネットリストおよびWAS/ISファイル)アプローチをサポートしています。部品番号データの前方同期はネットリストファイルを使用して行うことができ、後方同期はWAS/ISファイル(各指定子が何であったかと現在何であるかをリストアップする)を使用して行うことができます。デザインを同期するための推奨方法は、直接デザイン同期です。

ユニークIDを使用したコンポーネントのリンク

デザインを再度部品番号付与をした場合、回路図のコンポーネント指定子またはコンパイルされたコンポーネント指定子は、PCBのコンポーネント指定子と一致しなくなるため、デザインを正常に完了するために同期が必要になります。Altium Designerは、回路図シンボルを対応するPCBフットプリントに関連付けるキーフィールドとして指定子自体に依存するのではなく、ユニークIDentifier(UID)システムを通じてデザイン同期を維持することができます。UIDは、ソースコンポーネントを一意に識別するシステム生成値であり、各回路図コンポーネントを対応するPCBコンポーネントにマッチさせます。

コンポーネントが回路図シートに配置されると、自動的にUIDが割り当てられます。コンポーネント情報が初めてソース回路図ドキュメントから空のPCBに転送されると、各回路図コンポーネントのUID情報が対応するPCBコンポーネントに割り当てられます。

リファクタリングを使用すると、デバイスシートを回路図シートに変換したり、その逆を行ったりしながら、シートとそのコンポーネントのユニークIDを維持できます。さらに、現在のプロジェクト内の他の回路図シートにサブサーキットをリファクタリング(または移動)することができ、サブサーキットのユニークIDを維持できます。Refactorコマンドは、編集メニューにあります。

Altium Designerの同期機能は、Design » Updateコマンドを起動することで開始され、これらのUIDを使用して各回路図コンポーネントをそのPCB相当物と照合します。設計の更新/変更は、エンジニアリング変更命令(ECO)を使用して実施できます。ECOは、同期アクションの要求を満たすために、1つ以上の設計文書に対して実施する変更のすべてをリストアップします。ECOは、以下のようなさまざまな状況で設計更新を行うために使用されます:

- SCHからPCBへの設計の更新。

- 回路図コンポーネント指定子とコンパイル済みコンポーネント指定子に対する部品番号更新の実行。

- Parameter Managerを使用してパラメータの更新を実装する。(Tools » Parameter Manager).

- ソースライブラリまたは会社のデータベースに保存されている情報でパラメータ情報を更新する。回路図とPCBを比較すると(Design » Updateを選択する場合など)、Altium Designerはまず同じUIDを共有するコンポーネントを照合します。UID を共有しないコンポーネントが検出されると、警告が表示され、アプリケーションは指定子による照合を試みます。回路図と PCB の両方に一致する UID を割り当てるまで、このメッセージは引き続き表示されます。一意の ID とその相関関係は、Edit Component Linksダイアログ (Project » Component Links) で管理します。

ダイアログは、PCBドキュメントがアクティブなときにのみ開くことができます。UIDの変更は常に回路図ではなくPCBに適用されるためです。設計の任意の段階でこのダイアログを使用して、ドキュメント間のコンポーネントのリンクを表示し、コンポーネントが正しく一致しているかを確認するとともに、現在一致していないコンポーネントに一致するUIDを割り当てることができます。

ダイアログは、PCBドキュメントがアクティブなときにのみ開くことができます。UIDの変更は常に回路図ではなくPCBに適用されるためです。設計の任意の段階でこのダイアログを使用して、ドキュメント間のコンポーネントのリンクを表示し、コンポーネントが正しく一致しているかを確認するとともに、現在一致していないコンポーネントに一致するUIDを割り当てることができます。

もし回路図またはPCBの部品番号を再度付与を実施する場合、UIDが最初に一致していることを確認することが重要です。なぜなら、回路図またはPCBのすべての指定子を変更すると、回路図コンポーネントをそのPCB相当物にリンクするために使用できる情報はUIDだけになるからです