Routing Rule Types

The design rules of the Routing category are described below.

The Routing category of design rules

Width

Default Rule: required

This rule defines the width of tracks placed on the copper (signal) layers.

Constraints

Constraints for the Width rule, which apply to all layers. Enter layer-specific values in the grid (hover the cursor over to show).

-

Preferred Width - specifies the preferred width to be used for tracks when routing the board.

-

Min Width - specifies the minimum permissible width to be used for tracks when routing the board.

-

Max Width - specifies the maximum permissible width to be used for tracks when routing the board.

-

Check Tracks/Arcs Min/Max Width Individually – for each route in the net targeted by the rule, check that the width of each individual track and arc falls within the minimum and maximum range

-

Check Min/Max Width for Physically Connected – for each route in the net targeted by the rule, check that the actual width of the routed copper formed by the combination of tracks, arcs, fills, pads, and vias falls within the minimum and maximum range

-

Use Impedance Profile - this option becomes available when at least one impedance profile is defined in the Layer Stack Manager. When enabled, use the drop-down to select the impedance profile desired. When the rule is configured in this mode, the Preferred Width required on each routing layer is calculated as part of the specified impedance profile (Min Width and Max Width values will also be set to this value when the option is enabled). Once the rule is defined, as you route a net that falls under the scope of the rule, the track width will automatically be set to the width required to meet the specified impedance for that layer. When this option is enabled, the Preferred Width cannot be edited in the rule, but the Min Width and Max Width values can.

► Learn more about Configuring the Layer Stack for Controlled Impedance Routing

-

Show values for layer stack – This option appears in the dialog when multiple layer stacks are defined in the Layer Stack Manager. If the board includes multiple layer stacks, then the Width Constraints must be configured for each stack, using either the all-layer fields above the image or the layer-specific fields in the Layer Attributes Table.

► Learn more about Defining and Configuring Substacks

Configure the Constraints for each layer stack in the design.

-

Layer Attributes Table - the grid region at the bottom of the dialog displays all signal layers defined in the layer stack unless the Use Impedance Profile option is enabled. If this option is enabled, then only the layers available as part of the selected impedance profile will be displayed. The minimum, maximum and preferred routing widths and other layer-specific information are displayed. The routing width fields can be set globally by defining the values in the constraint fields above the image or individually by typing values directly into the table. When the Use Impedance Profile option is enabled, the required width entries will be automatically calculated and entered for each layer in the table. In this mode, the Preferred Width values cannot be edited, but the Min Width and Max Width values can.

Rule Application

The Preferred Width setting is obeyed by the Autorouter.

The Min Width and Max Width settings are obeyed by the Online DRC and Batch DRC. They also determine the range of permissible values that can be used during interactive routing (press the Tab key while routing to change the trace width within the defined range through the Properties panel). If a value is entered outside of this range, it will automatically be clipped.

Note

The width of each net in a differential pair is monitored by the applicable Differential Pairs Routing rule.

Routing Neck-Down

Default Rule: not required

It is not uncommon for a net to be routed at different widths as the routing travels across the board. For example, routing into or out of a BGA will often require escape routes narrower than the preferred width routes allowed by the applied impedance profile. This rule lets you define the maximum allowed total length of such narrower traces so that the route still delivers the required impedance.

The rule can be defined in both the Physical view of the Constraint Manager and the PCB Rules and Constraints Editor dialog.

Constraints

Constraints for the Routing Neck-Down rule

Neck-Down Length specifies the maximum allowed length of continuous routes (in each net scoped by the rule) whose width is between the Min Width and Preferred Width defined by the applicable Routing Width rule. Alternatively, use the grid to define the allowed length per layer basis.

Rule Application

Enable the Routing Neck-Down rule type check for online and/or batch checking in the Design Rule Checker dialog to detect violations of the Routing Neck-Down rules in corresponding DRC modes. Detected rule violations will be marked with a hatched pattern on corresponding traces in the design space.

Routing Topology

Default Rule: required

This rule specifies the topology to be employed when routing nets on the board. The topology of a net is the arrangement or pattern of the pin-to-pin connections. By default, pin-to-pin connections of each net are arranged to give the shortest overall connection length. A topology is applied to a net for various reasons; for high-speed designs where signal reflections must be minimized the net is arranged with a daisy chain topology; for ground nets, a star topology could be applied to ensure that all tracks come back to a common point.

Constraints

Default constraint for the Routing Topology rule

Topology - defines the topology to be used for the net(s) targeted by the scope (full query) of the rule. The following topologies can be applied:

-

Shortest- this topology connects all nodes in the net to give the shortest overall connection length. -

Horizontal- this topology connects all the nodes together, preferring horizontal shortness to vertical shortness by a factor of 5:1. Use this method to force routing in the horizontal direction. -

Vertical- this topology connects all the nodes together, preferring vertical shortness to horizontal shortness by a factor of 5:1. Use this method to force routing in the vertical direction. -

Daisy-Simple- this topology chains all the nodes together, one after the other. The order they are chained is calculated to give the shortest overall length. If a source and terminator pad are specified, then all other pads are chained between them to give the shortest possible length. Edit a pad to set it to be a source or terminator. If multiple sources (or terminators) are specified, they are chained together at each end. -

Daisy-MidDriven- this topology places the source node(s) in the center of the daisy chain, divides the loads equally and chains them off either side of the source(s). Two terminators are required, one for each end. Multiple source nodes are chained together in the center. If there are not exactly two terminators theDaisy-Simpletopology is used. -

Daisy-Balanced- this topology divides all the loads into equal chains, the total number of chains equal to the number of terminators. These chains then connect to the source in a star pattern. Multiple source nodes are chained together. -

Starburst- this topology connects each node directly to the source node. If terminators are present, they are connected after each load node. Multiple source nodes are chained together, as in theDaisy-Balancedtopology.

Rule Application

Batch DRC, during autorouting.

Notes

-

When using the Autorouter, routing completion time may be longer when using topologies other than

Shortest. -

Implementation of custom topologies defined using From-Tos can be checked during the Batch DRC of the Routing Topology design rules applied to corresponding nets. A violation is detected if there is an electrical connection between the pads of a From-To and the shortest path contains at least one other pad of this net. Violations will not be detected for nets with a large number of pads (more than 20) or primitives (more than 1024).

Routing Priority

Default Rule: required

This rule assigns a routing priority to the net(s) targeted by the rule. The Autorouter uses the assigned priority value to gauge the routing importance of each net in the design and hence determine which nets should be routed first.

Constraints

Default constraint for the Routing Priority rule

Routing Priority - the priority value assigned to the net(s) targeted by the scope (full query) of the rule. Enter a value between 0 and 100. The higher the number assigned, the greater the priority when routing.

Rule Application

During autorouting.

Routing Layers

Default Rule: required

This rule specifies which layers are allowed to be used for routing.

Constraints

Default constraints for the Routing Layers rule

Enabled Layers - each signal layer currently defined for the design, as defined by the layer stackup, are listed. Use the associated Allow Routing option to enable/disable routing on a layer, as required.

Rule Application

Online DRC, Batch DRC, during interactive routing, and while autorouting.

Note

When using the Autorouter, the routing direction for each enabled signal layer in the design is defined as part of the Situs Autorouter setup. Directions are specified in the Layer Directions dialog, accessed by clicking the Edit Layer Directions button in the Situs Routing Strategies dialog.

Routing Corners

Default Rule: required

This rule specifies the corner style to be used during autorouting.

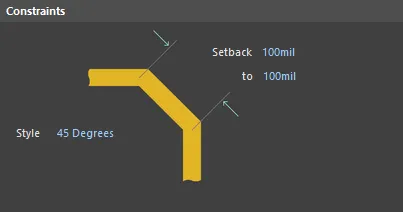

Constraints

Default constraints for the Routing Corners rule

-

Style - specifies which routing corner style to use. The following three styles are available:

-

90 Degrees. -

45 Degrees. -

Rounded.

-

-

Setback - these two fields allow you to define a minimum and maximum value for the setback when using the

45 DegreesandRoundedcorner styles. The setback is the distance from the 'true' corner location (that which would exist if using the90 Degreesstyle) to the point at which the Autorouter should begin its chamfering or rounding, effectively controlling miter size or corner radius.

Rule Application

This rule is intended for use by third-party Autorouters that implement 45° routing as a post process. It is not followed by the Situs Autorouter, which implements 45° routing as a native process.

Routing Via Style

Default Rule: required

This rule specifies the style of vias that can be used when routing. You can define specific Min/Max/Preferred values for the via's diameter and hole size - defined as part of the rule's constraints - or use templates available to the board design.

Constraints

Default constraints for the Routing Via Style rule. Roll the mouse over the image to compare the two modes available.

Mode - use the drop-down to choose from the following two modes:

- Min/Max preferred - choose this mode to set the permissible values (Minimum/Maximum/Preferred) for the via's diameter and hole size as part of the rule itself.

- Template preferred - choose this mode to be able to use via styles defined through via templates available to the board.

Mode = Min/Max preferred

When this mode is chosen, the constraints region changes to present the following options:

-

Via Diameter - specifies constraint range values to be adhered to with respect to the diameters of vias placed when routing the board. The following individual values are definable:

- Minimum - the minimum permissible value for the via diameter.

- Maximum - the maximum permissible value for the via diameter.

- Preferred - the preferred value for the via diameter.

-

Via Hole Size - specifies constraint range values to be adhered to with respect to the hole sizes of vias placed when routing the board. The following individual values are definable:

- Minimum - the minimum permissible value for the via hole size.

- Maximum - the maximum permissible value for the via hole size.

- Preferred - the preferred value for the via hole size.

Mode = Template preferred

When this mode is chosen, the constraints region changes to present the following options:

-

Templates List - lists the available via templates that can be used with the rule. These are via templates (local or defined in Pad Via Template Libraries) that are made available to the board design as part of the Local Pad & Via Library (accessed through the PCB Pad Via Templates panel). For each available template, the following information is presented:

- Template Name - the read-only name of the template. For a local template, auto-generated naming is used in compliance with IPC standards. For a template sourced from a PvLib, this naming can be customized as part of template configuration within that library.

- Description - the read-only description written for the template.

- Library - the library from which the template is sourced. This can be <Local> (where the via is defined and saved with the PCB document) or the name of the external Pad Via Template Library (<LibraryName>.PvLib) which has been made available to the PCB document.

- Enabled - enable this option to have the template made available for via placement during Interactive Routing.

Rule Application

Online DRC, Batch DRC, during autorouting, and during interactive routing.

When the mode of the rule is set to Min/Max preferred, the following considerations apply:

- The Preferred via attributes are used by the Autorouter.

- The Minimum and Maximum via attributes are obeyed by the Online DRC and Batch DRC.

- The Maximum and Minimum via attributes also determine the range of permissible values that can be used during interactive routing - when you press the + (or *) key on the numeric keypad to toggle routing signal layers and drop a via, press the / key on the numeric keypad to place a fanout via, or press the 2 shortcut key to place a via without changing layer.

- When a routing via is about to be placed during interactive routing, you can cycle through the Minimum / Preferred / Maximum / User Choice via definition by pressing the 4 key. The currently selected state is displayed in the Heads-Up Display and on the Status bar. You can also press the Tab key while routing to access the Properties panel, from where you can edit the via properties within the Min/Max rule range. If a value is entered outside of its range, it will automatically be clipped.

-

If there are multiple Via Types defined in the Layer Stack Manager, for example, thruhole and blind/buried vias, it can be possible for different Via Types to be used for the current layer transition. In this situation, press the 6 key to cycle through allowed Via Types. The selected Via Type is displayed in the Heads-Up Display and on the Status bar. Alternatively, press the 8 key to display a pop-up menu of allowed Via Types, and click on the required one.

When the mode of the rule is set to Template preferred, the following considerations apply:

- When a routing via is about to be placed during interactive routing, you can cycle through the enabled via templates by pressing the 4 key. The selected template is displayed in the Heads-Up Display and on the Status bar. You can also press the Tab key while routing to access the Properties panel, from where you can change the via template currently applied.

- If there are multiple Via Types defined in the Layer Stack Manager, for example, thruhole and blind/buried vias, it can be possible for different Via Types to be used for the current layer transition. In this situation, press the 6 key to cycle through allowed Via Types. The selected Via Type is displayed in the Heads-Up Display and on the Status bar. Alternatively, press the 8 key to display a pop-up menu of allowed Via Types, and click on the required one.

Note

In order to control the size of blind and buried vias, individual rules can be set up targeting the different layer pairs. For example, to control the via size for blind vias between the top layer and mid-layer 1, the following scope (Full Query) can be used:

(StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')

To control the via size for buried vias between mid-layer 2 and mid-layer 3, the following scope would be used:

(StartLayer = 'Mid-Layer2') and (StopLayer = 'Mid-Layer3')

Alternatively, instead of creating individual rules, you can expand the one rule query using ORs as follows:

((StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')) or((StartLayer = ' Mid-Layer2') and (StopLayer = 'Mid-Layer3'))

Fanout Control

Default Rule: required

This rule specifies fanout options to be used when fanning out the pads of surface mount components in the design that connect to signal and/or power plane nets. Fanout essentially turns an SMT pad into a thru-hole pad, from a routing point of view, by adding a via and connecting track. This greatly increases the probability of successfully routing the board, as a signal is made available to all routing layers instead of just the top or bottom layer. This is particularly needed in high-density designs where routing space is very tight.

Constraints

Default constraints for the Fanout Control rule (Fanout_Default)

-

Fanout Style - specifies how the fanout vias are placed in relation to the SMT component. The following options are available:

-

Auto- chooses the style most appropriate for the component technology in order to give optimal routing space results. -

Inline Rows- fanout vias are placed within two aligned rows. -

Staggered Rows- fanout vias are placed within two staggered rows. -

BGA- fanout occurs in accordance with the specified BGA Options. -

Under Pads- fanout vias are placed directly under SMT component pads.

-

-

Fanout Direction - specifies the direction to use for the fanout. The following options are available:

-

Disable- do not allow fanout with respect to the SMT components targeted by the rule. -

In Only- fanout in an inward direction only. All fanout vias and connecting track will be placed within the component's bounding rectangle. -

Out Only- fanout in an outward direction only. All fanout vias and connecting track will be placed outside of the component's bounding rectangle. -

In Then Out- fanout all component pads in an inward direction to begin with. All pads that cannot be fanned out in this direction should be fanned out in an outward direction (if possible). -

Out Then In- fanout all component pads in an outward direction to begin with. All pads that cannot be fanned out in this direction should be fanned out in an inward direction (if possible). -

Alternating In and Out- fanout all component pads (where possible) in an alternating fashion, first inward then outward.

-

-

Direction From Pad - specifies the direction to use for the fanout. When a BGA component is fanned out, its pads are sectioned into quadrants, with fanout applied to the pads in each quadrant simultaneously. The following options are available:

-

Away From Center- fanout for pads in each quadrant is applied following a 45° angle away from the component's center. -

North-East- all pads in each quadrant are fanned out in a North-Easterly direction (45° anti-clockwise from the horizontal). -

South-East- all pads in each quadrant are fanned out in a South-Easterly direction (45° clockwise from the horizontal). -

South-West- all pads in each quadrant are fanned out in a South-Westerly direction (135° clockwise from the horizontal). -

North-West- all pads in each quadrant are fanned out in a North-Westerly direction (135° anti-clockwise from the horizontal). -

Towards Center- fanout for pads in each quadrant is applied following a 45° angle toward the component's center. In most cases, uniformity of direction will not be possible due to the required fanout space already taken by another pad's fanout via. In these cases, fanout will occur in the next available direction (North-East, South-East, South-West, North-West).

-

-

Via Placement Mode - specifies how the fanout vias are placed in relation to the pads of the BGA component. The following options are available:

-

Close To Pad (Follow Rules)- fanout vias will be placed as close to their corresponding SMT component pads as possible without violating defined clearance rules. -

Centered Between Pads- fanout vias will be centered between the SMT component pads.

-

Rule Application

During interactive routing and autorouting.

Notes

-

The following default Fanout Control design rules are automatically created, covering the typical component package types available (listed in descending order of priority). These rules can be edited or others can be defined in accordance with your individual design requirements.

-

Fanout_BGA – with a query of

IsBGA. -

Fanout_LCC - with a query of

IsLCC. -

Fanout_SOIC - with a query of

IsSOIC. -

Fanout_Small - with a query of

(CompPinCount < 5). -

Fanout_Default - with a query of

All.

-

Fanout_BGA – with a query of

-

The style used for the fanout vias will follow the applicable Routing Via Style design rule(s). Additional tracks laid down as part of the fanout process from pad to via will follow the applicable Routing Width design rule(s).

-

To fanout the pads of a component, ensure there are no polygon pours under this component on any layer. Polygons can be shelved before creating fanouts and restored afterward.

Wire Bonding

Default Rule: not required

This rule defines constraints related to designs that feature Wire Bonding.

Constraints

- Wire To Wire – specifies the minimum permissible distance between 3D bodies of adjacent bond wires.

- Min Wire Length – specifies the minimum permissible length of a bond wire.

- Max Wire Length – specifies the minimum permissible length of a bond wire.

- Bond Finger Margin – specifies the minimum permissible margin from the edge of a bond finger pad.

Rule Application

Batch DRC

Differential Pairs Routing

Default Rule: required

This rule defines the routing width of each net in a differential pair and the clearance (or gap) between the nets in that pair. Differential pairs are typically routed with specific width-gap settings to deliver the required differential impedance needed for that net pair.

Learn more about Differential Pair Routing

Learn more about Controlled Impedance Routing

Constraints

Default constraints for the Differential Pairs Routing rule

- Min Width - specifies the minimum permissible width to be used for tracks when routing the differential pair.

- Min Gap - specifies the minimum permissible clearance between primitives on different nets within the same differential pair during routing. The Min, Preferred & Max Gap settings in this design rule are used as the differential pair is being routed, rerouted, or interactively modified (during Interactive Sliding). Note that these Gap settings are NOT used during rule checking (DRC). During DRC, the Gap is tested by the applicable Clearance Constraint rule - refer to the Notes below for more information on managing this.

- Preferred Width - specifies the preferred width to be used for tracks when routing the differential pair.

- Preferred Gap - specifies the preferred clearance between primitives on different nets within the same differential pair.

- Max Width - specifies the maximum permissible width to be used for tracks when routing the differential pair.

- Max Gap - specifies the maximum permissible clearance between primitives on different nets within the same differential pair.

- Max Uncoupled Length - specifies the value for the maximum permissible uncoupled length between positive and negative nets within the differential pair.

-

Use Impedance Profile - this option becomes available when at least one impedance profile is defined in the Layer Stack Manager. When enabled, use the drop-down to select the required impedance profile. When the rule is configured in this mode, the Preferred Width and Preferred Gap required on each routing layer are calculated as part of the specified impedance profile. Once the rule is defined, as you route a differential pair that falls under the scope of the rule, the track widths and pair gap will automatically be set to the values required for that layer to meet the specified impedance.

-

Show values for layer stack - this option appears in the dialog when there are multiple layer stacks defined in the Layer Stack Manager. If the board includes multiple layer stacks, then the Differential Pairs Routing Constraints must be configured for each of the layer stacks, using either the all-layer fields above the image or the layer-specific fields in the Layer Attributes Table.

- Layer Attributes Table - the grid region at the bottom of the dialog displays all signal layers defined in the layer stack, unless the Use Impedance Profile option is enabled. If this option is enabled, then only the layers available as part of the selected impedance profile will be displayed. The minimum, maximum and preferred width and gap constraints and other layer-specific information are displayed. The routing Width and Gap fields can be set globally by defining the values in the constraint fields above the image or individually by typing values directly into the table. When the Use Impedance Profile option is enabled, the required width entries will be automatically calculated and entered for each layer in the table. In this mode, the Preferred Width and Preferred Gap values cannot be edited, but the Min and Max values can.

Rule Application

Online DRC, Batch DRC, interactive routing (and re-routing), autorouting, interactive length tuning (Min Gap is applied), and when interactively modifying the pair, such as sliding a track segment of one of the nets in the pair.

Notes

- While the width of each net in a differential pair is monitored by the applicable Differential Pairs Routing rule (and not by a Width rule), clearance checking between the nets in that pair is still governed by the applicable Clearance design rule. If the gap value used for routing the differential pair is less than the minimum allowed clearance between the differential pair nets set by the Electrical Clearance design rule, a violation of the Electrical Clearance design rule will occur. In other words, a Clearance rule must be defined that targets the differential pair (on the specific layer where needed) with its connective checking mode set to Same Differential Pair and whose clearance is set to be equal to, or lower than, the value for the Min Gap constraint defined for that layer as part of the applicable Differential Pairs Routing rule.

- The clearance from a net in a differential pair to any other electrical object not part of the pair is monitored by the applicable Clearance rule.

- While the optimal Width-Gap settings may be achievable for most of the board, there will often be areas, such as under a BGA component, where smaller and tighter Width-Gap settings must be used. Defining the Min Gap to be less than the Preferred Gap allows the router to bring the pair members closer to each other, where obstacles require this. While this works, it comes at a cost; routing operations become much more complicated and are, therefore, slower. This requirement can also be achieved by defining multiple differential pair routing rules - a lower-priority rule that targets the differential pair across the board and a higher-priority rule that targets the differential pair in the specific area where a narrower Width-Gap setting is required. You then target the differential pair in that area by defining a Room Definition rule for that area and use that room as part of the scope of the differential pair routing rule that requires a tighter Width-Gap setting.

- Differential Pair classes can be defined on the schematic for use in rule scoping.

► Learn more about Differential Pair Clearance Checking

).

). ).

).