PCB 编辑器是一个规则驱动的设计环境,在这个环境中,您可以定义许多类型的设计约束,这些约束可以被检查以确保您的电路板的完整性。在线 DRC 功能会在您工作时监控启用的规则,并立即突出显示任何检测到的设计违规情况。或者,您也可以运行批量 DRC 来测试设计是否符合规则,并生成一份详细说明启用的规则和任何检测到的违规情况的报告。

在本教程的早期,您检查并配置了一些设计约束,包括电气间隙、布线宽度和布线过孔样式。除这些之外,当创建新板时,还会自动定义许多其他设计规则。

配置和运行设计规则检查 (DRC)

主页面: 设置与运行 DRC

通过运行设计规则检查(DRC)来检查设计是否有违规情况。在线和批量 DRC均可在设计规则检查器对话框中配置,可通过从主菜单中选择“工具”»“设计规则检查”命令来访问该对话框。该对话框提供一般报告选项(报告选项 -  )和配置测试特定规则类型的能力(要检查的规则 -

)和配置测试特定规则类型的能力(要检查的规则 -  )。

)。

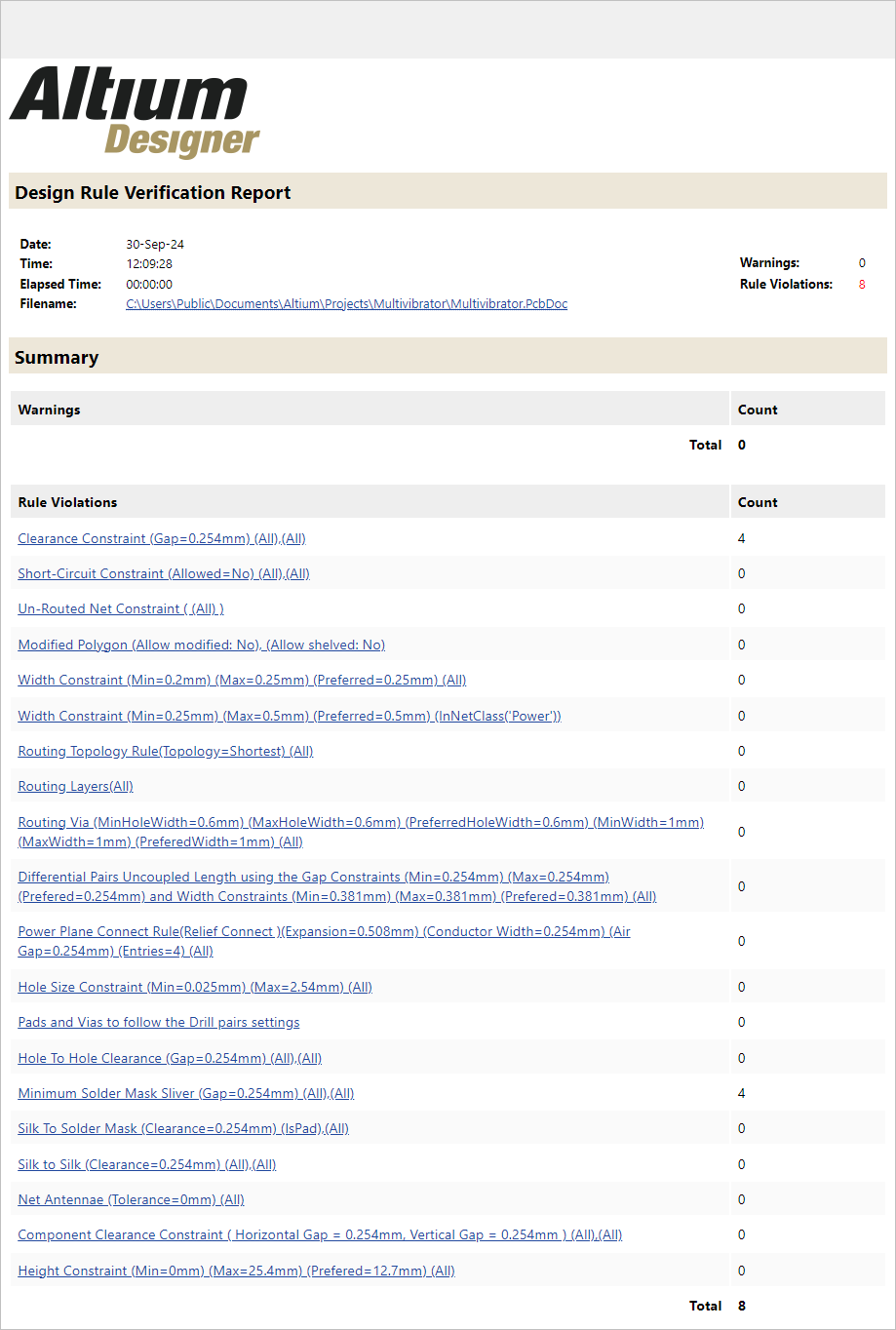

通过点击对话框底部的 按钮来运行设计规则检查(DRC)。DRC运行后,消息面板会打开并列出所有检测到的违规情况。如果在对话框中启用了创建报告文件选项,则设计规则验证报告将在单独的文档标签页中打开。报告详细说明了启用检查的规则、检测到的违规数量以及每项违规的具体详情。

按钮来运行设计规则检查(DRC)。DRC运行后,消息面板会打开并列出所有检测到的违规情况。如果在对话框中启用了创建报告文件选项,则设计规则验证报告将在单独的文档标签页中打开。报告详细说明了启用检查的规则、检测到的违规数量以及每项违规的具体详情。

-

从主菜单选择Tools » Design Rule Check 命令,打开设计规则检查器对话框。

-

在对话框的报告选项页面上,确保启用了创建报告文件选项。

-

在对话框的要检查的规则页面上,右击网格区域并选择批量DRC - 使用中项。

-

禁用测试点规则的批量DRC。为此,请在树中选择测试点部分,并禁用此类别中四种规则类型的批量复选框。

-

点击对话框底部的 按钮运行DRC。 设计规则检查器对话框将关闭,报告将打开。它将包括(至少):

按钮运行DRC。 设计规则检查器对话框将关闭,报告将打开。它将包括(至少):

报告的上半部分详细说明了启用检查的规则和检测到的违规数量。点击规则可跳转至并检查这些违规。

报告的下半部分显示了每个被违反的规则,后面跟着违规对象的列表。点击违规条目可跳转至PCB上的该对象。

检测到的违规行为也将在打开的消息面板中列出。

定位并解决违规问题

主页: 查询与解决设计违规问题

作为设计师,您必须找到 PCB 中的违规行为、确定其状况和实际故障程度,并找出解决违规行为的最合适方法。

解决间隙违规问题

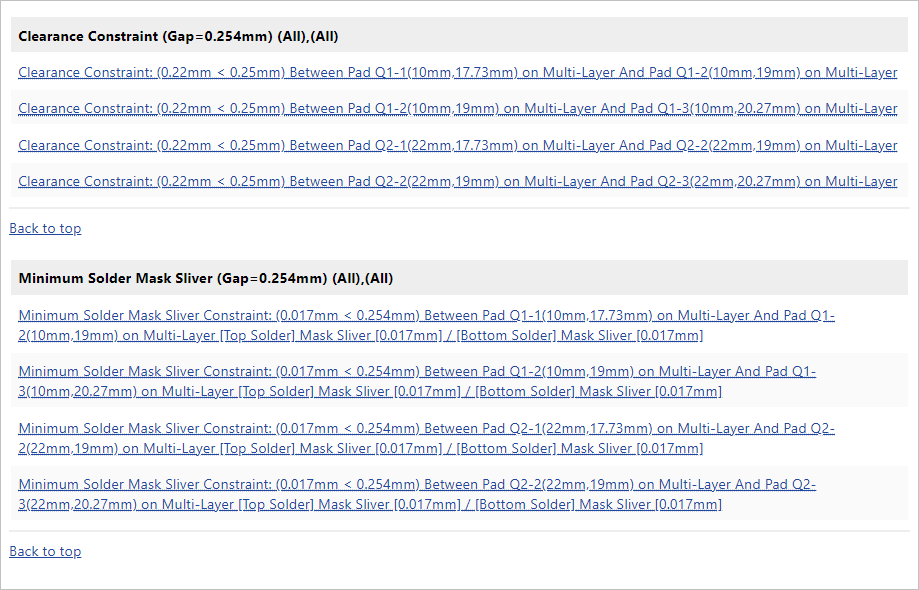

在教程设计中,晶体管封装焊盘之间的间隙约束违规了四次。解决这些违规的方法有两种:

由于0.25毫米的间隙相当宽裕,而实际间隙非常接近这个值(0.22毫米),在这种情况下,一个不错的选择是配置规则以允许较小的间隙。这种解决方案在这种情况下是可以接受的,因为唯一具有通孔焊盘的其他组件是连接器,其焊盘间距为 1 毫米。如果不是这种情况,最好的解决方案是添加第二个间隙约束,仅针对晶体管焊盘,就像对阻焊扩展规则所做的那样。

我应该使用约束管理器还是PCB规则和约束编辑器对话框?

根据教程设计中可用的是约束管理器还是PCB规则和约束编辑器对话框(您可以通过在项目的PCB文档打开时,从PCB编辑器打开设计主菜单并检查是否有约束管理器或规则命令来快速检查),使用下面其中一个可折叠部分中描述的相应方法。

解决间隙违规问题(PCB规则和约束编辑器对话框)

-

点击设计空间顶部的PCB文档选项卡,使其成为活动文档。

-

打开PCB规则和约束编辑器对话框(设计» 规则)。

-

在对话框左侧的电气类别中找到并选择现有的间隙规则。

-

在规则约束的网格区域将TH Pad – 至 – TH Pad值更改为0.22毫米。要做到这一点,点击单元格,输入0.22,然后按Enter。

❯ ❮

Javascript ID: Tutorial_Dlg_PCBRulesAndConstraintsEditor_Clearance_AD24

|

-

点击应用接受更改并保持PCB规则和约束编辑器打开。

解决阻焊层最小间隙违规问题

阻焊层是涂在电路板外表面上的一层薄薄的漆状层,为铜提供保护和绝缘覆盖层。阻焊层上会形成开口,用于将元件和电线焊接到铜上。这些开口在 PCB 编辑器中显示为阻焊层上的对象(请注意,阻焊层是在负片中定义的 - 您看到的对象将成为实际阻焊层上的孔)。

在制造过程中,阻焊层采用不同的技术。成本最低的方法是使用阻焊层将其丝网印刷到电路板表面。为了解决层对齐问题,阻焊层开口通常比焊盘大,这反映在默认设计规则中使用的 4 mil(~0.1 mm)扩展值上。

还有其他应用阻焊层的技术,这些技术可以提供更高质量的层配准和更准确的形状定义。如果使用这些技术,阻焊层扩展可以更小甚至为零。减小掩模开口可降低出现阻焊条或丝印层与阻焊层间隙违规的可能性。

这是一个阻焊层细条违规。紫色表示每个焊盘周围的阻焊层膨胀部分。

要查看阻焊层最小间隙违规的详细信息,必须启用阻焊层显示。使用 “查看配置”面板配置层可见性。

如果不考虑制造成品电路板所采用的制造技术,诸如此类的阻焊问题就无法解决。

例如,如果这是一块用于高价值产品的复杂多层电路板,那么很可能会采用高质量的阻焊技术,从而允许阻焊层膨胀很小或为零。但是,像本教程中的电路板这样的简单双面电路板更有可能被制造为低成本产品,需要使用低成本的阻焊技术。这意味着通过减少整个电路板的阻焊层膨胀来解决阻焊层裂片违规问题并不是合适的解决方案。

与 PCB 设计的许多方面一样,解决方案在于有针对性地进行深思熟虑的权衡,以尽量减少其影响。

要解决这个违规问题,您可以:

这是一个设计决策,需要根据您对组件的了解以及将要使用的制造和组装技术来做出。如果增大阻焊层开口以完全去除晶体管焊盘之间的阻焊层细条,那么这些焊盘之间就更有可能形成焊锡桥接;而减小阻焊层开口虽然仍然会留下一道细条(这道细条可能可接受,也可能不可接受),但还会引入阻焊层与焊盘对准问题的可能性。

在本教程中,您将结合使用第二和第三种选项,将最小细条宽度减小到适合本电路板设置的数值,并且仅针对晶体管焊盘减小阻焊层膨胀。

我应该使用约束管理器还是PCB规则和约束编辑器对话框?

根据教程设计中是否可用约束管理器或PCB规则和约束编辑器对话框(当项目的 PCB 文档打开时,您可以通过从 PCB 编辑器中 打开设计主菜单并检查约束管理器 或规则命令来快速检查),使用下面可折叠部分中描述的相应方法。

解决阻焊条违规问题(PCB规则和约束编辑器对话框)

-

第一步是减少允许的阻焊条宽度。为此,在PCB 规则和约束编辑器对话框左侧树的制造类别 中找到并选择名为“MinimumSolderMaskSliver”的现有最小阻焊条规则。

-

对于此类设计,可以接受与焊盘间距相等的值,即 0.22 毫米(~8.7 mil)。编辑阻焊层最小间隙值,使其位于规则的 约束0.22区域 内。

-

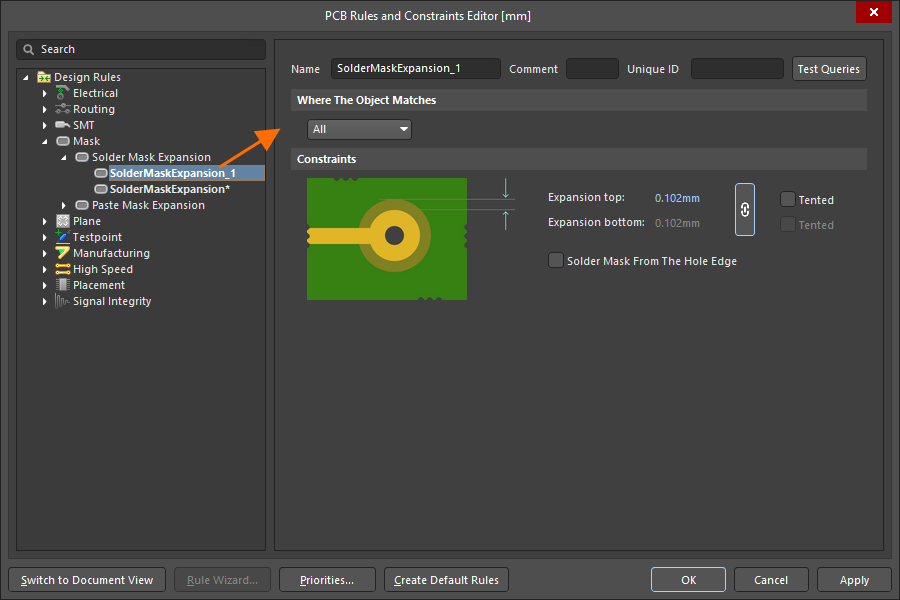

下一步是仅为晶体管添加一个阻焊层扩展规则,将该规则下的阻焊层扩展减小到零。这样做意味着阻焊层开口的大小将与焊盘相同,从而使焊盘之间的阻焊细条宽度等于焊盘之间的分离距离(0.22毫米)。在左侧树状结构中展开“Mask”类别,然后展开“Solder Mask Expansion”规则类型。应该有一个名为“SolderMaskExpansion”的规则。

-

点击该规则以选择它并显示其设置。它将指定一个扩展值为0.102mm(4 mil)。

由于只有晶体管焊盘违反了规则,因此您无需编辑该值,而是创建一个新规则。

-

要添加新的阻焊层扩展规则,请在左侧树状目录中的现有规则上右键单击,然后从上下文菜单中选择新建规则。

-

将创建一个名为SolderMaskExpansion_1的新规则。点击它以显示其设置。

-

将规则设置编辑为如下所示:

-

点击确定接受更改并关闭PCB规则和约束编辑器对话框。

-

通过在项目面板中右键单击PCB文档条目并从上下文菜单中选择保存,将PCB文档保存到本地。

解决违规后运行设计规则检查

现在,重新运行DRC以确保所有违规都已解决。

在生成输出之前,始终确认您有一个清晰的设计规则验证报告。

-

打开设计规则检查器对话框(工具 » 设计规则检查),并确保在报告选项页面上启用了创建报告文件选项。

-

点击 按钮。

按钮。

-

将生成一份新报告并在单独的文档选项卡中打开。确保其中不包含任何规则违规。

-

从项目中删除生成的 DRC 报告。它将在设计发布过程中生成。为此,请在“项目”面板中的Generated\Documents条目下找到报告文件,右键单击它并选择“从项目中删除”命令。在打开的“从项目中删除”对话框中,选择“删除文件”选项。

-

关闭当前打开的所有文档。您可以右键单击设计空间顶部的文档选项卡,然后从上下文菜单中 选择“关闭所有文档”命令。

-

将项目保存到工作区。为此,点击项目面板中项目条目旁的保存到服务器控件,在打开的保存到服务器对话框中,在评论字段中输入有意义的评论(例如,PCB设计完成),然后点击确定按钮。