父页面: 捕捉您的设计思想为原理图

电子设计包含重复电路部分并不罕见。它可能是立体声放大器,或者是64通道混音台。这种类型的设计完全支持一套称为多通道设计的功能集。

视频多路复用器的两个解码通道,使用多通道设计结构意味着解码通道只需捕捉一次。

在多通道设计中,您只需捕捉重复电路一次,然后指示软件重复所需次数。当设计自动编译时,它会在内存中展开,所有组件和连接性都会根据用户定义的通道命名方案重复所需次数。

您捕捉的逻辑设计实际上从未被展平,源始终保持为多通道原理图。当您将其转移到PCB布局时,物理组件和网络会自动按所需次数步进。您可以完全访问用于在原理图和PCB之间工作的标准交叉探测和交叉选择工具。PCB编辑器中还有一个工具可以复制一个通道的放置和布线到所有其他通道,并且能够轻松移动和重新定位整个通道。

动态编译

相关页面: 验证您的设计项目

设计连接模型在每个用户操作后通过动态编译逐步更新。您不需要手动编译项目,因为这是自动完成的。对于设计项目,自动编译过程执行三个功能:

- 实例化设计层次结构。

- 在所有设计图纸之间建立网络连接。

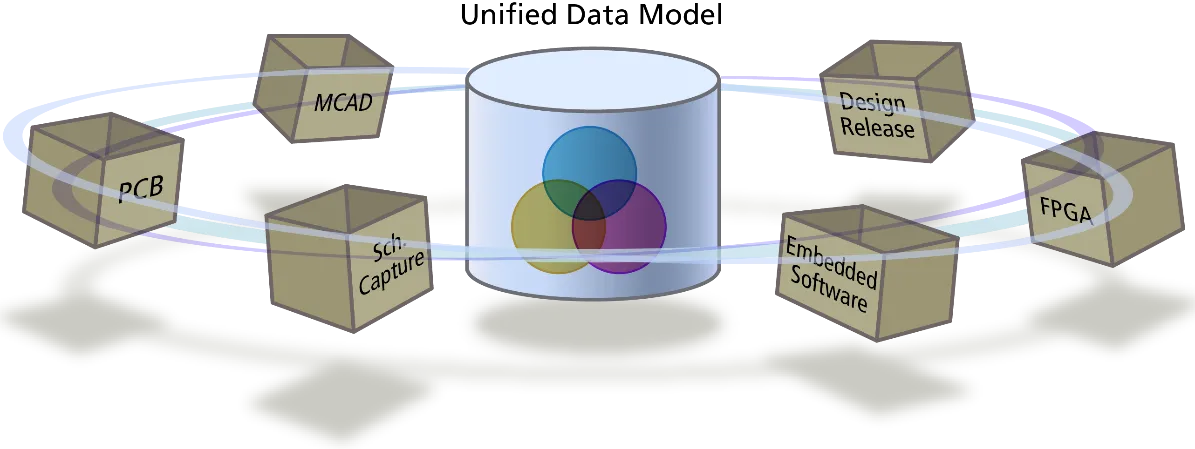

- 构建设计的内部统一数据模型(UDM)。

这确保所做的任何设计更改都会立即反映在导航器和项目面板中。

项目的编译模型被称为统一数据模型(UDM)。UDM包括设计中每个组件的详细描述,以及它们之间是如何连接的。

为了检查UDM和编译器设置之间的逻辑、电气和绘图错误,您必须验证项目。可以通过从主菜单选择项目 » 验证项目命令或右键单击项目面板中的项目条目,并从上下文菜单中选择验证项目命令来访问此命令。

编译器检测到的任何违规行为都会在消息面板中列为警告和/或错误。编译器在检查源文件是否有违规行为时,会使用在项目选项对话框的错误报告和连接矩阵标签页上定义的选项(适用于项目类型)。

在Altium Designer 20.0之前的软件版本中,项目必须手动编译以构建统一数据模型。从那时起,设计数据模型在每次用户操作后通过动态编译逐步更新 - 创建所谓的动态数据模型(DDM)。项目不涉及手动编译,一切都是自动完成的。设计连接模型在每次用户操作后也会通过动态编译逐步更新。

统一数据模型

要理解多通道设计,有助于了解设计数据是如何管理的。软件的一个基本元素是统一数据模型(UDM)。当项目自动编译时,会创建一个单一的、连贯的模型,该模型位于设计过程的中心。然后可以使用软件内的各种编辑器和服务访问和操作模型中的数据。UDM的结构旨在容纳设计的所有方面的所有信息,包括组件及其连接性,而不是为各种设计领域使用单独的数据存储。

统一数据模型使所有设计数据可供所有编辑器使用,并有助于提供像多通道设计这样的复杂功能。

UDM与分层设计系统相结合,用于提供多通道设计功能。"通道"是Sheet Symbol内的电路 - 在这个Sheet Symbol下可以是单个图纸,也可以是包含其他子图纸的项目结构的整个分支。您还可以在通道内创建通道,在两级多通道设计中,上层通道被称为银行,下层通道被称为通道。

因为这个完整的、适用于PCB的描述存在于内存中,所以只要有一种系统化的方法来处理重复对象,例如组件指定器和网络,就可以重复电路的一部分。系统命名在项目选项对话框的多通道标签中定义,如下所述。

创建多通道设计

当电路的一部分被重复时,设计就是多通道的。这是在图纸符号级别完成的,方法有:

- 放置多个都引用同一个子原理图的图纸符号,或

- 配置单个图纸符号以重复所需次数的引用子原理图

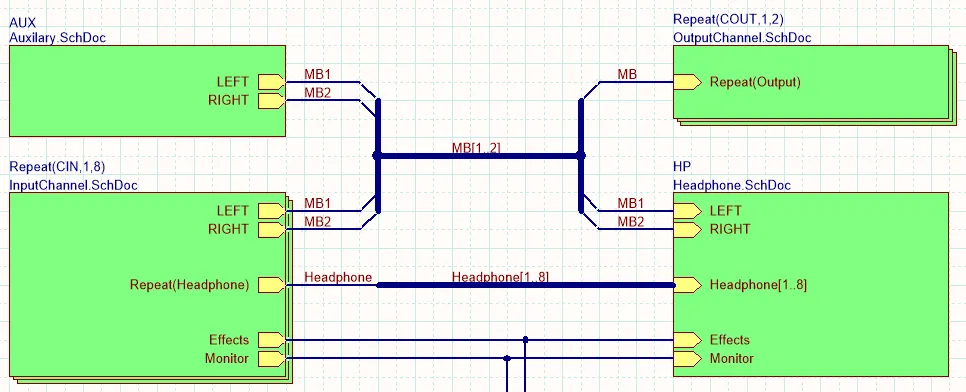

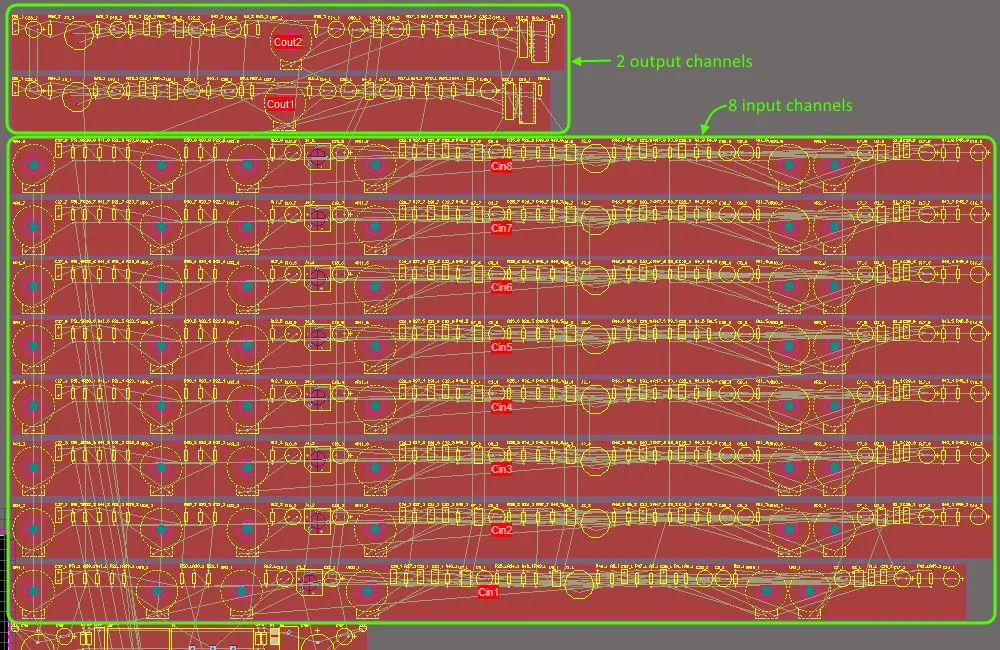

第一张图片 - 有四个图纸符号,都引用同一个子图纸(PortIO.SchDoc)。第二张图片 - 通过使用Repeat关键字,InputChannel.SchDoc重复了八次,OutputChannel.SchDoc重复了两次。

上面的图片展示了创建多通道设计的两种方法。在第一张图片中,有四个图纸符号都引用同一个子图纸(PortIO.SchDoc)。在第二张图片中,InputChannel.SchDoc通过图纸符号的指定器字段中的Repeat关键字重复了八次,OutputChannel.SchDoc重复了两次。

项目中重复的组件标识符和网络名称通过使用标准命名方案来解决。例如,一种命名方案是在重复的组件和网络标识符(网络标签和端口)中添加通道索引,如下图中的高亮部分所示。

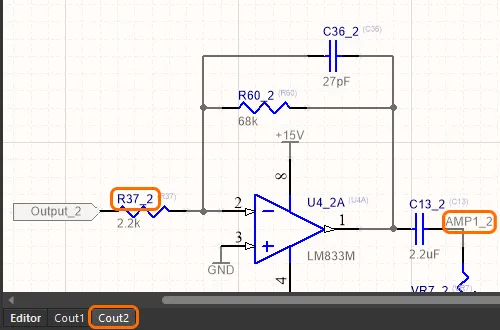

注意当项目打开时,原理图底部出现的标签页。 编辑器 标签页包含您所捕获的逻辑设计,其他编译后的标签页(COUT1 和 COUT2)也会出现,代表将传输到PCB编辑器的物理设计。每个物理通道都会有一个标签页。

编译后的项目,显示了逻辑视图的标签页,以及传输到PCB的每个物理通道的标签页。注意重复的标识符和网络标识符是如何管理的。

重复关键字

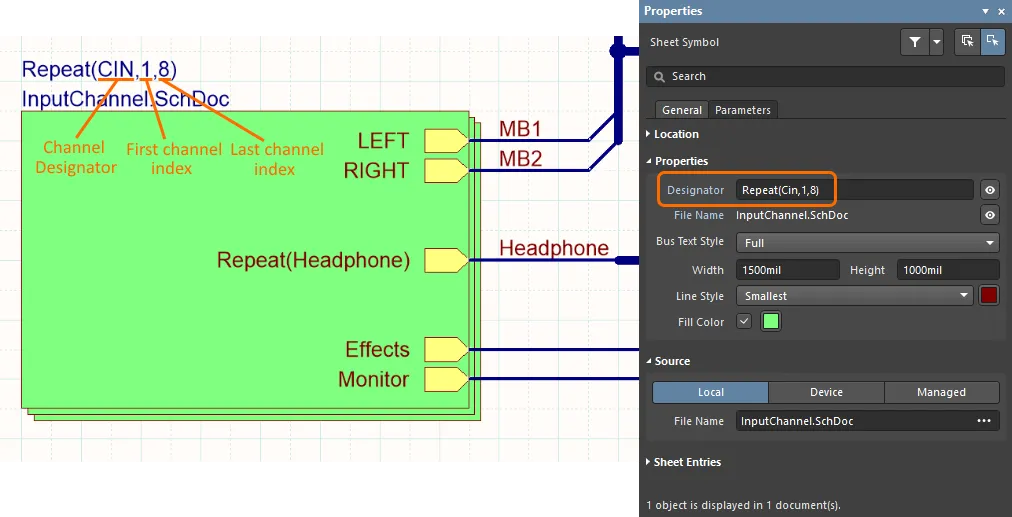

如前所述,通过放置多个引用相同子图的表格符号,或者在表格符号的标识符字段中包含Repeat关键字来重复一个通道。当使用Repeat关键字时,表格符号被绘制为一组堆叠的表格符号。

Repeat语句定义了通道标识符和通道数量。注意表格符号是如何被绘制为一组堆叠的符号,以表示重复的通道。

每个通道由来自表格符号标识符的通道标识符标识。当通过放置多个表格符号来通道化设计时,通道标识符是为每个表格符号定义的标识符值。如果通过使用Repeat关键字来通道化设计,通道标识符是由Repeat关键字定义的ChannelIdentifier+ChannelIndex。

当使用Repeat关键字时,标识符字段的语法如下:

Repeat(<ChannelIdentifier>,<ChannelIndex_1>,<LastChannelIndex_n>)

当在

项目选项对话框的选项标签页上启用

表格符号的新索引选项时,任何数字或数字都可以用作重复表格符号的第一个或最后一个索引,包括0;最后一个索引必须始终大于第一个索引,且不允许使用负数。

多通道命名

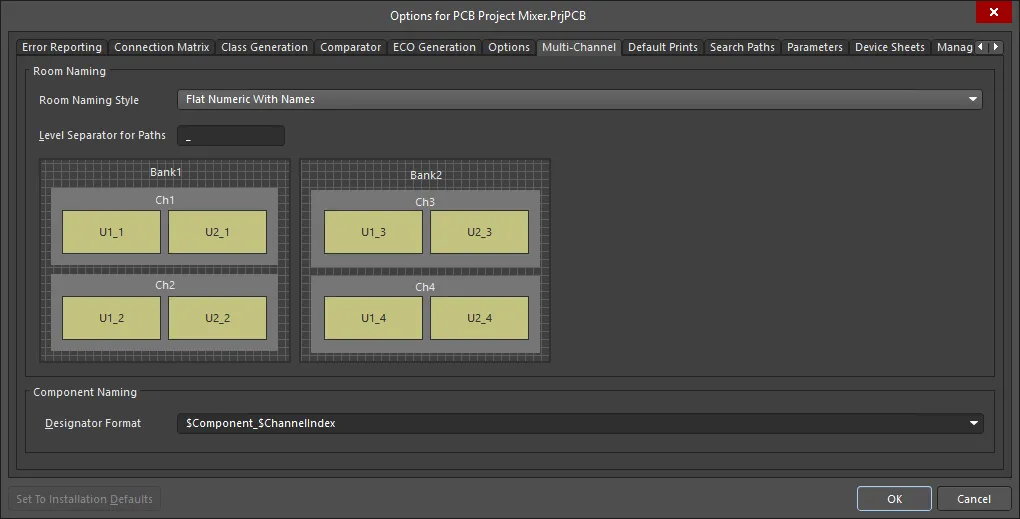

能够一次捕获然后重复 - 多通道设计 - 的概念是通过构建软件的统一数据模型(UDM)来实现的。重复的组件使用系统化的命名方案命名,该方案在项目选项对话框的多通道标签上配置,如下所示。

该对话框包括一个上部分用于控制Room的命名,和一个下部分用于控制这些Room内组件的命名。在Room级别,有2种扁平命名风格和3种层次命名风格,通常情况下,如果设计中有通道内的通道,你只需要选择一个层次命名风格。否则,一个扁平的Room命名风格更短且更容易理解。

对于组件命名,$Component$ChannelAlpha 或 $Component_$ChannelIndex 选项将提供最短且最容易解释的组件指示符。也可以使用可用关键字构建自己的指示符命名方案。

通过在项目选项对话框的多通道标签上选择系统化的命名方案,来管理重复的组件(和网络)。

- 除了组件之外,组件命名方案还用于在每个通道内唯一标识网络。该方案用于重命名网络标识符,包括网络标签和端口。

- 这些名称在原理图表上的显示将在下面的显示编译后的名称部分讨论。

Room的作用

ROOM是一个PCB设计对象,用于定义板上的一个区域,然后可以用两种方式使用:

- 包含对象 - 虽然Room像任何多边形形状对象一样放置,但实际上它是作为一个放置设计规则创建的。Room定义的一部分是指定必须包含在该Room内的对象 - 这通常是组件。当该Room移动时,Room内的所有组件也会移动。

- 限定其他设计规则 - 除了作为自己的规则之外,Room还可以用来限定其他设计规则。例如,一个路由宽度设计规则定义了一类网络的路由宽度,然后一个优先级更高的设计规则,其范围为Room,可以指定在该Room内应用于该类网络的不同宽度。

Room与多通道设计非常契合。它们可以在设计从原理图编辑器转移到PCB编辑器时自动创建,基于项目选项对话框的类生成标签上的选项,为每个表符号创建一个Room。除了将该通道的组件聚集在一起,Room还可以用于命名该Room内的组件。Room及其在板设计过程中的作用将在本文的多通道PCB设计部分进一步讨论。

如果您更喜欢扁平化的元件编号系统,可以通过执行板级注释来替换系统化的命名方案。之所以称为板级注释,是因为元件指示器只应用于完整的、编译后的设计(物理设计),这个设计最终将成为PCB。

多通道设计中的连通性

对于多通道设计,将网络标识符范围设置为自动、分层或严格分层。多通道设计必须是分层的,因为软件使用这种结构模型在设计编译时在内存中实例化通道。

软件必须支持两种不同的连通性要求,连接到重复通道的网络将是:

对此的支持程度取决于定义通道的方法(多个工作表符号,或通过Repeat关键字)。如果设计使用多个工作表符号(每个通道一个单独的工作表符号),那么网络连通性是明确的,由设计者放置的布线定义。

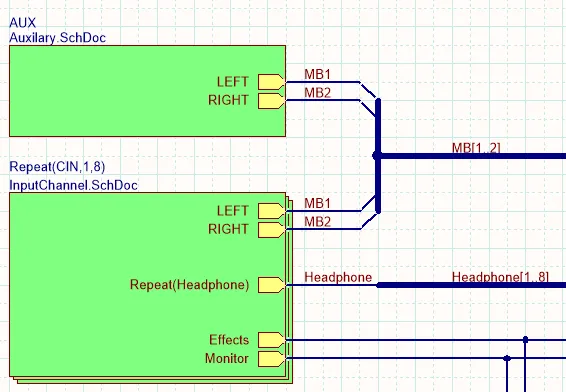

这个设计使用Repeat关键字创建多个通道。

如果设计使用Repeat关键字,那么以下连通性约定适用。

| 将网络传递给所有通道 |

如果需要在所有通道中都能使用某个网络,只需将其连接到工作表入口,如上图中连接到InputChannel.SchDoc工作表符号的Monitor网络所示。网络Effects、MB1和MB2也将在所有通道中可用。总线中的网络也是以同样的方式处理的,当总线连接到工作表入口时,该总线中的每个元素都将在所有通道中可用。 |

| 将网络传递给特定通道 |

要将总线中的单个网络分配给每个通道,需要在工作表入口使用Repeat关键字,如上图中Headphone总线所示,工作表入口的名称为Repeat(Headphone)。在这种情况下,网络Headphone1将连接到通道CIN1,Headphone2将连接到通道CIN2,依此类推。如果使用Repeat关键字创建通道,则无法将单个网络仅传递给一个通道。如果需要这样做,您必须为每个通道放置一个单独的工作表符号。 |

请注意,使用Repeat关键字时不支持将线束传递给通道。

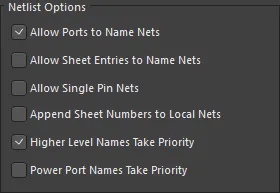

网络的命名方式

最终,每个网络在PCB上只能有一个名称(一个PCB网络不能有两个名称)。软件会自动解决具有多个名称的网络,使其在项目中只有一个单一的名称——在多通道设计中配置命名选项非常重要,以确保您的网络以对您有意义的方式标记。网络命名选项位于项目选项对话框的选项标签中的网表选项部分。

在多通道设计中设置这些选项的一个好方法是启用高级别名称优先选项,并在连接到通道化子图的所有网络上放置网络标签。

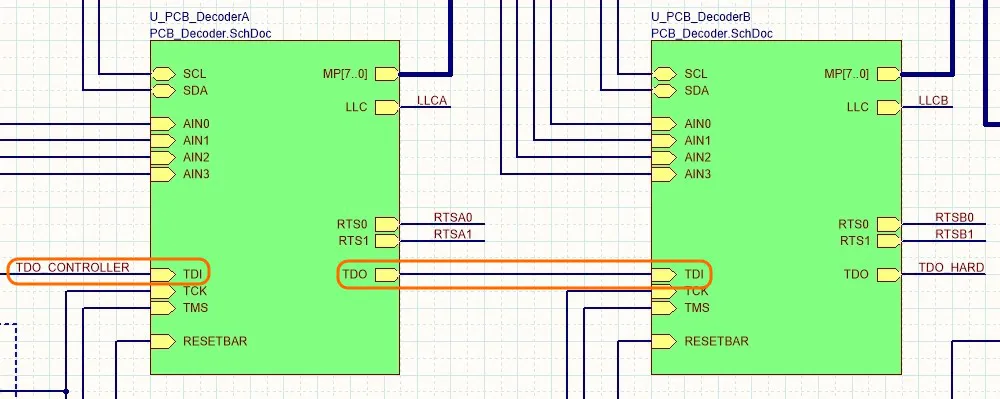

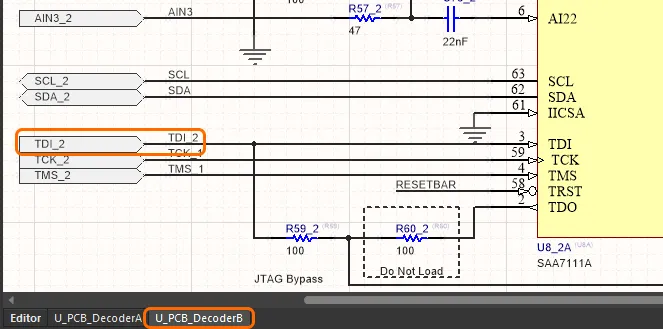

例如,考虑下面的图片。注意两个表符号都指向PCB_Decoder.SchDoc图纸,因此这个电路有2个通道,分别标识为U_PCB_DecoderA和U_PCB_DecoderB。

表符号包括一个称为TDI的表项,它是JTAG边界扫描链中的Test Data In线。DecoderA的TDO(测试数据输出)然后连接到链中下一个设备的TDI,该设备位于DecoderB通道中。

通过放置两个都引用相同原理图PCB_Decoder.SchDoc的表符号来创建两个解码器通道。

打开项目时,底部的原理图视图中会出现通道标签U_PCB_DecoderA和U_PCB_DecoderB,这些标签显示了将传递给PCB编辑器的物理设计。在下面的图片中,左边的编辑器标签下显示了捕获的解码器电路原理图,其后是该原理图的两个物理通道U_PCB_DecoderA和U_PCB_DecoderB。

在原始捕获的原理图中,设计师将网络标记为TDI(第一张图片)。注意软件如何在DecoderA标签中应用了更高级别的网络名称TDO_CONTROLLER(第二张图片),因为它是一个更高级别的网络名称(已经设置为在此设计中优先)。对于DecoderB,没有定义更高级别的名称,所以原始网络名称TDI在这个通道中被标识为TDI_2(第三张图片),因为这是在项目 选项对话框的多通道标签上定义的命名方案(组件命名方案用于标识每个通道内的组件和网络)。

PCB_Decoder.SchDoc原理图:第一张图片 - 捕获的原理图;第二和第三张图片 - 两个通道的编译视图。

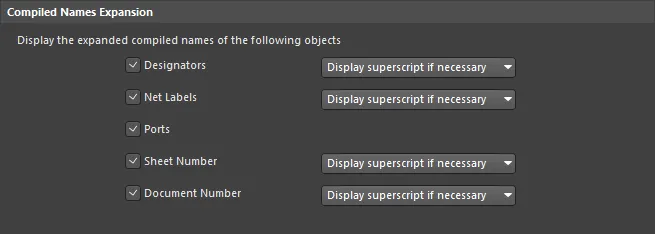

显示编译后的名称

在多通道设计中追踪和分析网络可能会令人困惑,因为名称必须改变以识别重复的网络,但仍需保持唯一性。为了帮助解决这个问题,有许多选项可以控制编译后对象名称的显示,包括组件的Designators(指示符)、Net Labels(网络标签)、Power Ports(电源端口)和Ports(端口)。还有Sheet(工作表)和Document Numbers(文档编号)的选项,当你准备生成打印类型输出时,这些将非常重要。

编译后对象名称的显示在Preferences(偏好设置)对话框的Schematic - Compiler(原理图 - 编译器)页面中进行配置,如下图所示。

配置编译后对象名称的显示,上标对于组件指示符很有帮助。

通常你会希望显示指示符和网络标签,如果你在诊断问题,端口也很方便。工作表编号和文档编号也很重要,必须正确配置,你可以在Design Annotation(设计注释)部分找到有关组件和工作表编号的信息链接。

请注意,Preferences(偏好设置)对话框的Schematic - Compiler(原理图 - 编译器)页面上的Net Labels(网络标签)选项也决定了Power Port(电源端口)对象的展开。

如果选择了Display superscript if necessary(必要时显示上标)选项,当前文档视图将包括来自不可见视图的对象标识符作为上标。根据你的偏好进行配置。

多通道设计的通道2(CIN2)视图。注意原始逻辑原理图的指示符和网络名称是如何显示为上标的。

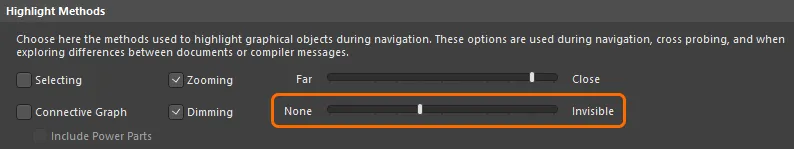

想知道为什么在通道(物理)标签页中一些原理图元素显示暗淡吗?默认设置是在通道标签页中以标准显示强度显示可编辑对象,非可编辑对象则显示暗淡。暗淡设置在首选项对话框的系统 - 导航页面中设置。暗淡对象的优点是它有助于防止您尝试执行不支持的编辑操作,例如在通道标签页中移动网络标签。根据需要设置暗淡级别。

解决多个网络名称错误

原理图编辑器的错误检查选项默认标记每个具有多个名称的网络。这可能发生在您故意更改名称时,例如当网络进入一个表符号,您更愿意在该表内使用不同的名称。下面的图片显示了这方面的一些例子,其中左和右输出被捆绑成总线在顶层表,但在表条目中被称为Left和Right。

之所以使用总线,是因为它允许两个输出通道由单个带有重复关键字的表符号表示。如果为左和右通道使用单独的导线,则设计师需要为左和右输出通道放置单独的表符号(都指向相同的子原理图表),然后将每个输出连接到其各自的输出表符号。

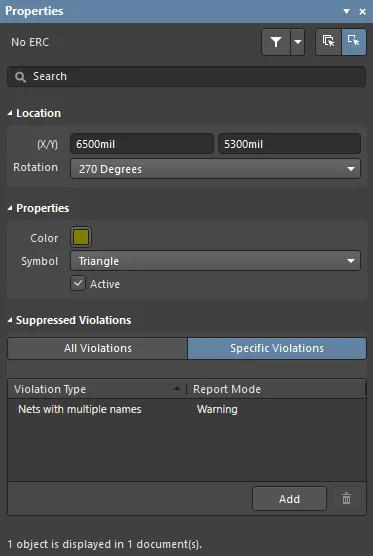

您必须指导软件如何处理多个网络标识符。为此,您需要:

- 在项目选项对话框的错误报告标签中将具有多个名称的网络错误检查设置为不报告。这不是首选选项,因为它阻止了整个设计中对此错误条件的所有检查。或者,您可以,

- 通过在消息面板中右击错误/警告并选择为此违规放置特定无ERC标记命令,在受影响的网络上放置特定无ERC指令。这样做会将您置于无ERC对象放置模式,光标附带预配置的特定无ERC标记,准备放置在错误的网络上。放置后,双击配置样式和颜色。

注意橙色圈出的小三角形;这是已放置的特定无ERC标记,用于禁用MB1和MB2网络上的重复网络名称错误。

多板设计注释

设计捕获过程的关键部分是对设计进行注释,即为每个组件和每个原理图表赋予唯一的标识符。这是多通道设计中的两阶段过程 - 首先,您放置的组件和您绘制的表必须编号。然后,由重复通道实例化的组件和表也必须编号。

如果您更喜欢扁平的组件编号系统,可以通过执行板级注释来替换系统化的命名方案。之所以称为板级注释,是因为组件指示器只应用于完整的、编译后的设计(物理设计),这个设计最终将成为PCB。请注意,原理图注释是进行板级注释的先决条件,确保多部分组件被打包,每个组件都有唯一的标识符。

这些板级注释存储在一个.Annotation文件中,该文件将每个逻辑指示器映射到分配的物理指示器。这个文件是项目的一部分,因此系统会提示您保存它。

请注意,在多通道设计中的注释过程可能会导致组件指示器非常长,因此在PCB上放置指示器字符串可能会很困难。您可以在PCB上选择逻辑和物理指示器显示 -

了解更多。

为了系统地根据位置为PCB编辑器中的目标组件分配指示器,您还可以使用

PCB位置注释。

多通道PCB设计

当您将设计从原理图编辑器转移到PCB编辑器时,如果在项目选项中启用了Room创建,则每个图纸的组件将被聚集在PCB放置Room中。

在多通道设计中使用Room的一个大优势是,PCB编辑器支持从一个Room(通道)复制放置和布线到其他Room(通道)。Room也可以像单个对象一样移动,简化了在PCB上排列通道的过程。

在设计从原理图编辑器转移到PCB编辑器后,八个输入和两个输出通道,红色区域是Room。

PCB Room的作用

一个Room是一个PCB设计对象,用于定义电路板上的一个区域,然后可以用两种方式使用:

- 包含对象 - 虽然Room像任何多边形形状对象一样被放置,但实际上它是作为一个放置设计规则创建的。Room定义的一部分是指定必须包含在该Room内的对象 - 这些通常是组件。当该Room移动时,Room内的所有组件也会随之移动。

- 限定其他设计规则 - 除了本身是一个规则外,Room还可以用来限定其他设计规则。例如,一个路由宽度设计规则定义了一类网络的路由宽度,然后一个优先级更高的设计规则,其范围为Room,可以指定在该Room内应用于该类网络的不同宽度。

在多通道设计中,Room的工作效果非常好。它们可以在设计从原理图编辑器转移到PCB编辑器时自动创建,基于类生成标签页中的选项,在项目选项对话框中,每个工作表符号都有一个Room。除了将该通道的组件聚集在一起外,Room还可以用于命名该Room内的组件。

有用的Room操作命令

- 设计 » Room - 这个子菜单有许多用于定义和修改Room的有用命令。

- 设计 » Room » 复制Room格式 - 使用此命令复制一个Room(通道)的放置和路由,到其他Room(通道)

- 设计 » Room » 移动Room - 可以通过点击和按住,任何没有其他设计对象下的地方来移动Room。光标将吸附到最近的组件焊盘或Room顶点(以较近者为准)。当您无法点击和按住而不点击设计对象时,请使用此命令。

- 编辑 » 选择 » Room连接 - 使用此命令选择所有从焊盘开始并在Room内结束的铜段。

组件如何连接

每个原理图组件通过唯一标识符(UID)链接到其PCB组件。当原理图组件放置在图纸上时,会分配UID,然后在设计转移到PCB编辑器时,将UID分配给PCB组件。这种方案适用于简单设计,但无法支持多通道设计,其中每个物理通道都重复相同的原理图组件(因此PCB组件将具有相同的UID)。

为了解决这个问题,通过结合父级表符号的UID和原理图组件的UID来创建PCB组件的UID。根据创建多通道设计的方式,PCB UID的语法略有不同。

对于通过放置多个引用相同原理图表的表符号来创建的多通道设计,每个表符号都可以提供唯一的ID,因此PCB UID的格式为:

\SheetSymbolUID\SchComponentUID

对于使用Repeat关键字创建的多通道设计,只有1个表符号UID可用,因此PCB UID还包括ChannelIndex,格式为:

\ChannelIndex+SheetSymbolUID\SchComponentUID

组件链接通过编辑组件链接对话框(PCB编辑器中的项目»组件链接命令)进行管理。在此对话框中应用更改时,PCB UID将更新以匹配原理图UID。

上述解释描述了组件如何连接。请注意,Altium Designer的更新版本(18.0及以后)不再在面板和对话框中显示UID。

在PCB上显示指示器

在多通道设计中定位指示器字符串可能很困难,因为它们可能相当长。除了选择一个能产生短名称的命名选项外,另一个选项是仅显示原始的逻辑组件指示而不是完整名称。例如,C30_CIN1将显示为C30。这将需要在板上添加一些其他标记来指示不同的通道,例如在组件覆盖层上绘制一个框来围绕每个通道。

您可以在PCB编辑器属性面板的其他部分选择逻辑和物理指示器显示(查看»面板»属性)。如果您选择在多通道设计中显示组件的逻辑指示器,这些将在PCB上显示,并在任何输出中显示,例如打印和Gerber文件。然而,在生成物料清单时,始终使用唯一的物理指示器。

► 了解更多关于注释组件

参数化多通道分层设计

重用设计部分的挑战,例如,将表符号链接到您公司首选的电源原理图,是组件的值并不总是从一个设计到另一个设计是固定的。

参数化分层设计解决了这个问题 - 它允许您将元件值的指定从原理图页面移动到引用该页面的页面符号中。这种能力也完美地适用于多通道设计,允许您在每个通道中拥有不同的元件值。请注意,这确实要求每个通道都有自己的页面符号,因为这是存储元件值的地方。

例如,图形均衡器可以多次重复相同的电路,每个通道之间的唯一区别是元件值。所以一个电容器在不同的通道中可能取值0.12µF、0.056µF和0.033µF。实现这一点很简单,因为您在引用每个通道的页面符号中指定这些值,从而无需拥有许多只有元件值不同的类似原理图。

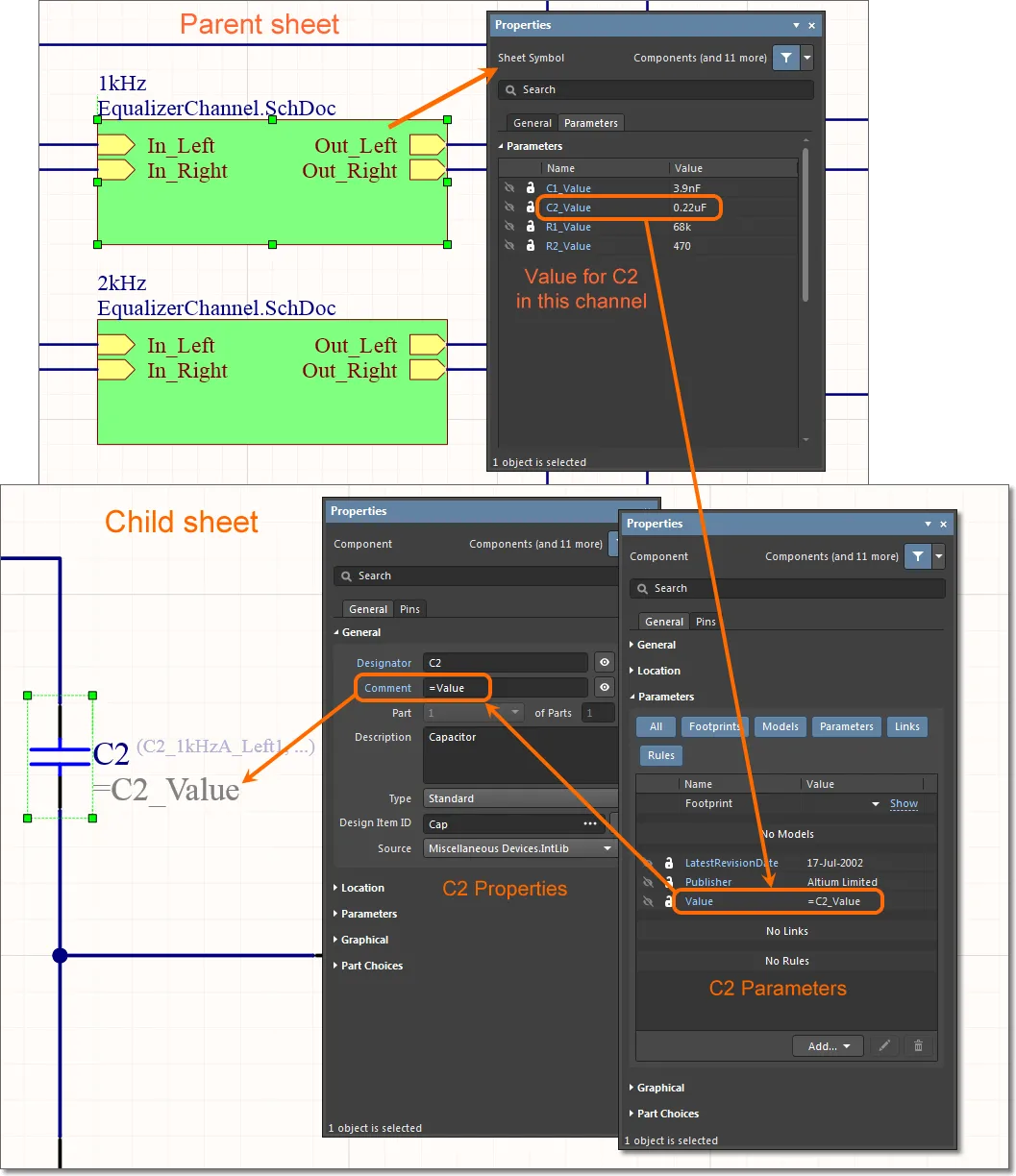

参数化元件是通过将它们的值声明为页面符号上的一个参数,然后在目标元件上引用该参数来定义的。下面的图片显示了左侧的图形均衡器的顶层页面,以及其旁边的1KHz页面符号的参数。图片还显示了捕获的低级原理图和编译的1KHz通道(由下方的标签页选择)。

一个图形均衡器,在每个通道中具有不同的电容器和电阻值;实际的元件值在页面符号中定义,因此只需要捕获一个低级原理图。

这些页面符号参数中的每一个也被定义为低级页面上的原理图元件的值参数,如下图所示。每个页面符号参数的值传递给相关的原理图元件,在那里它被映射到元件的注释字段中。请注意,如果直接使用值参数来显示原理图元件的值,而不是元件的注释参数,唯一的要求是将页面符号参数映射到元件的值参数(Value=C2_Value)并使其可见。

因为值参数的值为=C2_Value,编译器知道它必须在更高级别的页面符号中查找实际的元件值。

参数化层次结构不仅限于元件值。您可以参数化地引用任何元件参数,以及原理图页面上的其他对象文本标签,除了基本的连接元素,如元件ID、端口对象和文档文件名。如果您从层次结构中很多页面上的符号引用参数,系统将搜索层次结构,直到找到匹配的参数。